为新式待机准备硬件

进入新式待机状态时,硬件组件必须准备好转换为低功率工作模式。 在软件组件和应用已准备好进行低功耗操作后,硬件组件(包括其软件设备驱动程序)必须同样做好准备,以便实现低功耗操作。

本文的其余部分说明如何在准备片上系统 (SoC) 外部和内部的设备,以在硬件平台进入待机状态后在低功率模式下运行。

硬件转换为低功率模式

SoC 外部和 SoC 内部的所有设备都必须在睡眠期间进入低功率模式,以便实现较长的电池寿命。 在硬件平台进入睡眠状态之后,平台中的设备会按照从 SoC 外部设备开始的有序过程切换到低功率模式。

首先,SoC 或核心芯片外部的所有设备都必须进入低功率模式。 电源模式可能是时钟封闭空闲状态(例如,将 I²C 连接的触摸控制器置于睡眠模式)。 或者,电源模式可能是名为 D3cold 的电源封闭 0 瓦状态。 USB 连接的 Web 摄像头通常会在新式待机期间转换为 D3cold。 有关详细信息,请参阅“为 USB 设备支持 D3cold”。

对于将设备转换为最低功率模式,每个设备类和连接总线都有其自己的术语和要求。 但是,系统设计人员应为新式待机期间平台中的每个设备规划低功率操作模式,这十分重要。 系统的电池寿命以及将 SoC 本身置于低功率模式的能力取决于 SoC 自身外部的每个设备的正确电源管理。

接下来,将网络和无线电设备置于低功率睡眠模式。 在睡眠期间,这些设备通常仍会应用电源以维护连接,需要在必要时唤醒 SoC。 通常,通信和无线电设备会进入 D2/D3 低功率状态,但进入每种状态是特定于设备且特定于总线的。

在 SoC 外部的所有设备(包括通信设备)都断电后,SoC 上的主机控制器会关闭。 几乎每个 SoC 都具有 USB、I²C、GPIO、SDIO 和 UART 主机控制器。 SoC 上的每个组件都必须关闭,才能使 SoC 进入低功率模式。

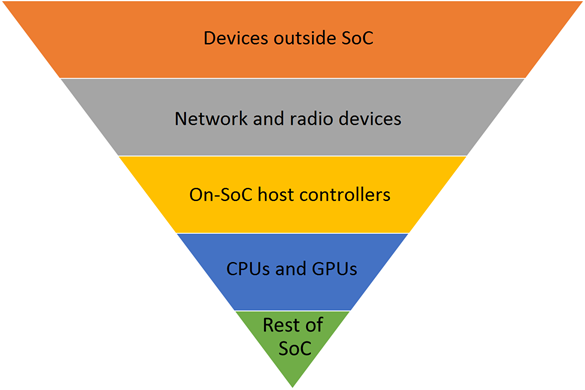

为睡眠期间的低功率准备硬件的过程可直观显示为一个倒金字塔,如下图所示。 当整个 SoC 芯片关闭后,便可以实现最低功率,但这种情况仅在金字塔中它上面的每个设备集都关闭后才会出现。

关闭 SoC 外部的设备

SoC 芯片外部的每个设备都必须进入低功率模式,以实现两个主要目标:

- 降低设备的功耗。

- 允许 SoC 自身关闭,具体方法是允许设备连接到的 SoC 内部主机控制器关闭。

用于关闭 SoC 外部的每个设备的方法因设备类和连接的总线而异。

SoC 外部的某些设备置于 0 瓦的未使用电源状态(称为 D3cold)。 适用于 D3cold 的常见设备包括摄像头和传感器。 驱动程序必须保存设备的注册状态,然后将设备转换为 D3 电源状态。 ACPI 固件会通过切换 GPIO 线路或是从电源管理 IC (PMIC) 关闭电源轨,来移除电源。

SoC 外部的某些设备置于低功率空闲模式,在该模式下会维持注册状态,或者设备可能只是进行时钟封闭。 例如,许多触摸控制器都具有功耗不到 1 毫瓦的时钟封闭状态。 使用时钟封闭状态的典型优势是可以加快开机时间并降低成本,而不必将设备连接到可切换的电源轨。

通常,SoC 外部的每个设备都必须能够进入功耗不到 1 毫瓦的低功率模式。 在具有内部时钟封闭状态时无法实现此功率级别的设备应通过 D3cold 实现电源封闭。

网络和无线电设备是 1 毫瓦准则的显著例外。 网络和无线电设备可能需要更多功率来维护网络连接或侦听无线设备。 某些系统设计人员将这些功率状态转换称为“运行时 D3”(RTD3)。

PCIe 设备的导向式电源管理

SoC 外部的 PCIe 卡必须启用一种称为 Device-S4 的导向式电源管理机制,以便确保它们可以进入低功率模式。 在没有 Device-S4 的情况下,如果用户在桌面新式待机系统上使用用户可访问的插槽将设备插入到 PCIe 根端口,并且设备驱动程序不支持运行时 D3 (RTD3),则 PCIe 设备可能会阻止系统进入 DRIPS。 若要避免此问题,OEM 必须将 PCIe 设备的根端口选择加入 Device-S4。 若要将 Device-S4 与给定 PCIe 设备结合使用,必须满足以下要求:

- 必须将设备的父 PCIe 根端口指定为 DRIPS 的约束。

- 父 PCIe 根端口必须在根端口的 D0->D3 时为根端口的所有下游子级应用基础设备重置,并在 D3->D0 转换时对这些子级解除基础设备重置的断言。 有关 PCIe 基础重置的详细信息,请参阅 PCI Express 基本规范的第 6.6.1 节。 可通过补充 ACPI 机制来提供基础重置的应用。 有关详细信息,请参阅本指南以了解 PCI 电源管理。 若要指示平台遵循此基础重置要求,固件必须使用对 GUID {FDF06FAD-F744-4451-BB64-ECD792215B10} 的支持定义 _DSD。 如果不这样做,则不会为该 PCIe 根端口下的设备触发导向式 DRIPS。 有关详细信息,请参阅 PCIe 根端口的 ACPI 设备特定数据 (_DSD)。

- 对于给定 PCIe 根端口,电源资源必须唯一,即不与任何其他根端口共享。

请注意,需要兼容性支持模块 (CSM) 的 PCIe 卡在新式待机系统中无法正常工作。 由于 UEFI 安全启动要求,新式待机系统上的 BIOS 中不支持 CSM。 有关详细信息,请参阅 Windows 硬件兼容性计划规范。

有关特定设备类的电源管理的详细信息,建议系统设计人员查看用于新式待机的特定于设备的电源管理,以及 Microsoft Collaborate 上的特定于设备的文档。

关闭网络设备

关闭网络和无线电设备是为睡眠期间的低功率操作准备硬件的另一个重要部分。 网络和无线电设备与 SoC 外部的其他设备不同,因为它们必须在应用电源的情况下保持开机,以便侦听感兴趣的事件并唤醒 SoC。 例如,在检测到匹配的数据包时,Wi-Fi 无线电必须能够侦听与 WoL 模式匹配的数据包并唤醒 SoC。

在睡眠期间,Windows 会在网络设备应唤醒 SoC 时将这些设备转换为 D2/D3 状态。 在将设备置于低功率 D2/D3 状态之前,Windows 网络堆栈会配置 WoL 模式和协议卸载。 所有网络设备(包括 Wi-Fi、移动宽带 (MBB) 和有线以太网)都必须能够在睡眠期间进入 D2/D3 状态。 如果网络设备不需要唤醒系统,则 Windows 会将设备转换为 D3 状态。 如果用户启用了飞行模式或禁用了特定网络设备,则可以将网络设备置于 D3 状态。

每个设备都具有用于从最低功率模式唤醒 SoC 的不同物理方法。 SDIO 或 UART 上的网络设备应向 GPIO 线路发出信号以唤醒 SoC。 通过 USB 或 HSIC 连接的网络设备应使用带内 USB 恢复信号唤醒 SoC。 PCI 或 PCIe 总线上的网络设备应使用带内 PME 信号唤醒 SoC。

此外,如果用户为无线电设备(如蓝牙或近场通信 (NFC) 设备)打开了无线电,则此设备应转换为 D2 状态。 在 D2 状态下,蓝牙无线电会侦听来自配对鼠标和键盘的输入事件。 如果检测到输入事件,则蓝牙无线电会切换连接到 SoC 的 GPIO 线路,使 SoC 从低功率模式唤醒。

每个网络或无线电设备都具有其自己针对新式待机的关闭功能实现。 建议系统设计人员阅读 Microsoft Collaborate 网站上特定于设备类的文档。

关闭 SoC 内部主机控制器

在 SoC 外部的所有设备(包括网络和无线电设备)关闭后,设备连接到的主机控制器必须关闭。 常见主机控制器包括 USB、PCI、SDIO、GPIO 和 I²C。

每个主机控制器的驱动程序只能在连接到主机控制器的每个设备都关闭后才关闭硬件。 一个常见示例是 USB 主机控制器。 仅当连接到它的所有 USB 设备都进入了选择性挂起状态后,USB 主机控制器才能关闭。 如果 USB 主机控制器连接了 USB 鼠标和键盘,则只有在鼠标和键盘都关闭后,主机控制器才能关闭。 如果鼠标或键盘保持打开状态,则 USB 主机控制器也会保持打开状态。

SoC 上的所有主机控制器都必须在睡眠期间关闭,才能使 SoC 自身关闭。 这便是每个设备都执行设备电源管理至关重要的原因。 仅当每个主机控制器都关闭时,SoC 自身才能关闭。 仅当连接到它们的所有设备都关闭后,主机控制器才能关闭。

关闭 CPU 和 GPU

在电源管理方面,SoC 芯片上的 CPU 和 GPU 与其他设备不同。 CPU 和 GPU 会作为关闭 SoC 自身的一部分进行关闭,每当没有针对它们的软件活动时,便能够关闭。

系统上的大多数软件活动都通过“为新式待机准备软件”中详细介绍的准备阶段来停止。 Microsoft Store 应用会在 PLM 阶段中暂停。 桌面应用程序会在完成 DAM 阶段时暂停。 在平台进入复原阶段后保留的唯一 CPU 活动是 Windows 自身的空闲操作。 同样,几乎没什么 GPU 活动,因为所有应用程序都已暂停并且屏幕已关闭。

Windows 会持续管理系统上 CPU 的电源状态,即使在屏幕打开并且用户在使用 PC 时。 相同 CPU 电源状态管理会在睡眠期间将 CPU 置于低功率模式。 当所有 CPU 都处于低功率模式并且 SoC 上的所有主机控制器都关闭时,SoC 自身可以关闭。

关闭 SoC

当 SoC 上的所有单个主机控制器、CPU 和 GPU 都关闭后,Windows 会确定是否可安全地关闭整个 SoC 自身。 SoC 供应商会提供电源引擎插件 (PEP),用于向 Windows 告知何时保存 SoC 上的所有状态,以便 SoC 可准备好进入低功率模式。 对于基于 Intel 的 SoC,PEP 是内置提供的。

每个 SoC 供应商都具有不同的 SoC 范围低功率状态实现。 这些状态通常是时钟封闭或电源封闭状态,在这些状态下,内存内容以自刷新方式保留,系统可以通过可编程计时器和少量 GPIO 引脚(功耗非常小)来进行唤醒。 Windows 将最低 SoC 功率状态称为最深运行时空闲平台状态 (DRIPS)。

DRIPS 状态始终具有以下特征:

- 对于在自刷新模式下保留内存的 SoC,DRIPS 是最低功耗状态。

- DRIPS 允许 SoC 在出现来自网络、无线电和输入设备的事件时唤醒。

- 在 DRIPS 状态期间,不允许运行任何 CPU 代码。

- 当 SoC 处于 DRIPS 状态时,平台在睡眠期间的功耗可能最少(网络和无线电设备导致的功耗变化除外)。