Hinweis

Für den Zugriff auf diese Seite ist eine Autorisierung erforderlich. Sie können versuchen, sich anzumelden oder das Verzeichnis zu wechseln.

Für den Zugriff auf diese Seite ist eine Autorisierung erforderlich. Sie können versuchen, das Verzeichnis zu wechseln.

RSS mit Hardwarewarteschlange verbessert die Systemleistung relativ zu RSS mit einer einzelnen Hardware-Empfangswarteschlangenlösung. NICs, die Hardware-Warteschlangen unterstützen, ordnen empfangene Daten mehreren Empfangswarteschlangen zu. Die Empfangswarteschlangen sind einer CPU zugeordnet. Die NIC weist empfangene Daten CPUs basierend auf Hashwerten und einer Indirektionstabelle zu.

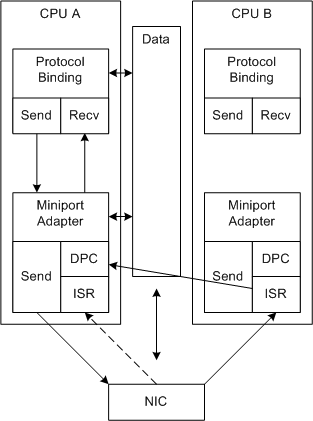

Die folgende Abbildung zeigt RSS mit NIC-Empfangswarteschlangen.

In der Abbildung stellen die gestrichelten Pfeile einen alternativen Pfad für die Empfangsverarbeitung dar. RSS kann die CPU nicht steuern, die den anfänglichen ISR-Aufruf empfängt. Der Treiber muss die Daten nicht in eine Warteschlange stellen, damit die ersten DPCs sofort auf der richtigen CPU geplant werden können.

Der folgende Vorgang wird für jeden Interrupt wiederholt:

Die NIC:

Verwendet DMA zum Ausfüllen von Puffern mit empfangenen Daten.

Der Miniporttreiber hat während der Initialisierung die Empfangspuffer im gemeinsam genutzten Speicher zugewiesen.

Berechnet einen Hashwert.

Stellt den Puffer für eine CPU in die Warteschlange und stellt die Warteschlangenzuweisungen für den Miniporttreiber bereit.

Beispielsweise könnte die NIC die Schritte 1-3 durchlaufen und dabei mittels DMA eine Liste der CPU-Zuordnungen nach dem Empfang einiger Pakete erstellen. Der spezifische Mechanismus bleibt dem NIC-Design überlassen.

Unterbricht das System.

Die empfangenen Puffer, die das System in einem Interrupt behandelt, werden zwischen den CPUs verteilt.

NDIS ruft die MiniportInterrupt-Funktion (ISR) des Miniporttreibers auf einer systembestimmten CPU auf.

Der Miniport-Treiber fordert NDIS auf, verzögerte Prozeduraufrufe (Deferred Procedure Calls, DPCs) für alle CPUs mit einer nicht leeren Warteschlange durchzuführen.

Beachten Sie, dass alle DPCs abgeschlossen sein müssen, bevor der Treiber Unterbrechungen aktiviert. Beachten Sie außerdem, dass der ISR möglicherweise auf einer CPU ausgeführt wird, die keine Puffer enthält, die verarbeitet werden sollen.

NDIS ruft die MiniportInterruptDPC-Funktion für jeden in der Warteschlange befindlichen DPC auf. Der DPC auf einer bestimmten CPU:

Build-Prozesse erhalten Deskriptoren für alle empfangenen Puffer in ihrer Warteschlange und leiten die Daten im Treiber-Stapel weiter.

Weitere Informationen finden Sie unter Angeben von RSS-Empfangsdaten.

Aktiviert die Unterbrechungen, wenn es der letzte DPC ist, der abgeschlossen werden soll. Dieser Interrupt ist abgeschlossen und der Vorgang wird erneut gestartet. Der Treiber muss eine Atomoperation verwenden, um den letzten DPC zu identifizieren. Beispielsweise kann der Treiber die NdisInterlockedDecrement-Funktion verwenden, um einen Atomzähler zu implementieren.