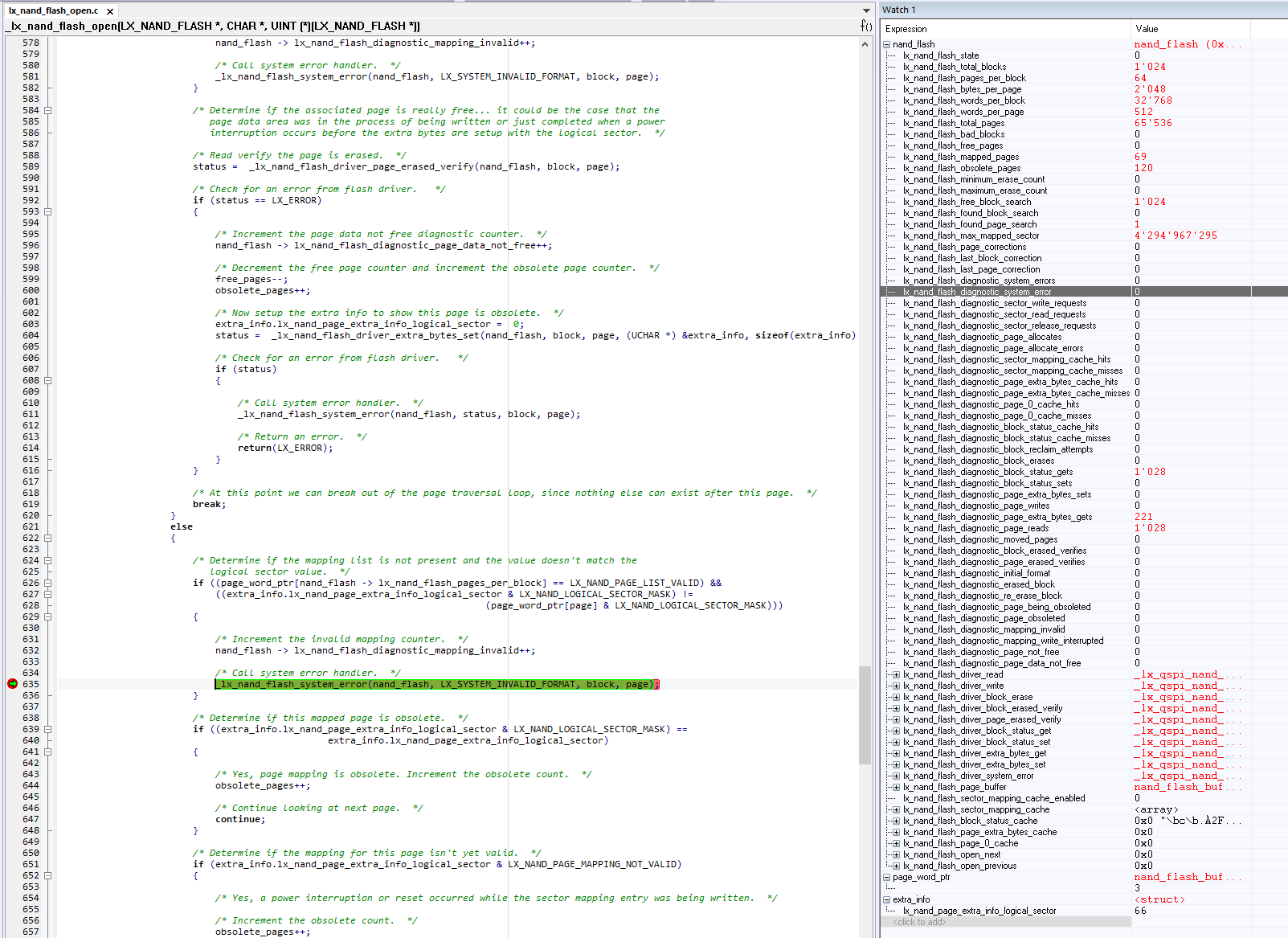

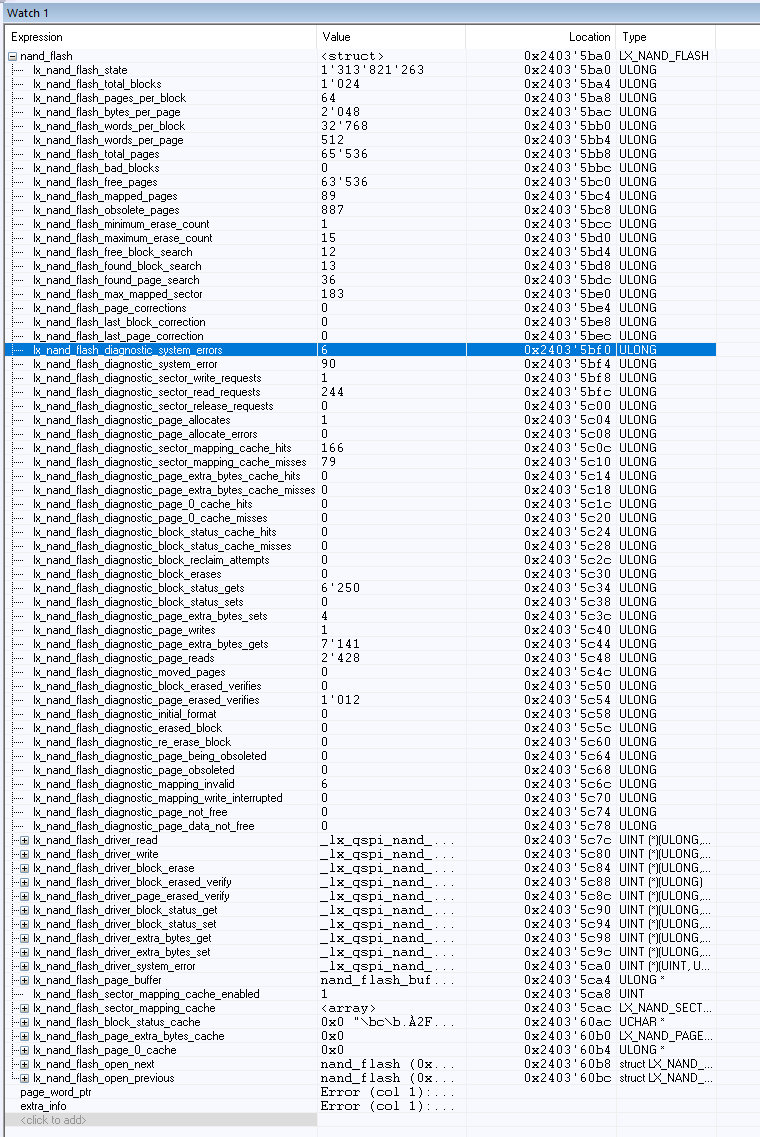

Based on another issue I ran into, I now see why LevelX has issues with HW ECC. This is just one example, there may be more.

Due to a bug/design flaw in LevelX, this causes an issue when the _lx_nand_flash_block_reclaim() runs and attempts to "Write the erased started indication."

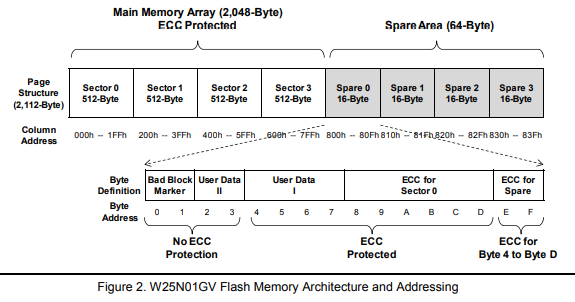

Basically what LevelX attempts to do is a read modify write of the NAND, without an erase, changing the value of a memory cell to LX_BLOCK_ERASE_STARTED. Since LX_BLOCK_ERASE_STARTED == 0 this would normally be OK, but the problem is the HW ECC for the sector has already been written based on the existing values. When verification is done after the write of LX_BLOCK_ERASE_STARTED, the verification fails because the return values are not correct. This is because the HW ECC attempts to correct what it assumes are errors.