Nota:

El acceso a esta página requiere autorización. Puede intentar iniciar sesión o cambiar directorios.

El acceso a esta página requiere autorización. Puede intentar cambiar los directorios.

Por Mark Russinovich

Publicado: 16 de diciembre de 2025

Coreinfo(3 MB)

Coreinfo(3 MB)

Introducción

Coreinfo es una utilidad que muestra la asignación entre los procesadores lógicos y el procesador físico, el nodo NUMA y el socket en el que residen, así como la memoria caché asignada a cada procesador lógico. Usa las API de Windows de bajo nivel (modo de usuario y modo kernel) para recuperar información detallada de topología de CPU directamente desde el sistema operativo. La versión de la línea de comandos genera la representación de la asignación a un procesador lógico con un asterisco, por ejemplo, "*". La interfaz de usuario proporciona varias vistas especializadas para explorar diferentes aspectos de la topología de CPU del sistema, incluidos núcleos lógicos y físicos, nodos NUMA, sockets, jerarquías de caché y métricas de rendimiento en tiempo real. Coreinfo es útil para obtener información sobre el procesador y la topología de caché del sistema.

Instalación

Extraiga el archivo en un directorio y, a continuación, ejecute Coreinfo escribiendo desde ese directorio Coreinfo / Coreinfo64 o Coreinfo64a, en función de la arquitectura. Inicie CoreInfoEx / CoreInfoEx64 / CoreInfoEx64a para la versión de la interfaz de usuario.

Nota: Algunas características pueden requerir privilegios administrativos para completar la recuperación de información.

Introducción a la interfaz de usuario

La interfaz de usuario de Coreinfo consta de varios componentes clave:

Diseño de ventana principal

- Panel superior: muestra información del sistema, incluidos el nombre de CPU, la arquitectura y los recuentos de núcleos.

- Panel de navegación (izquierda): proporciona acceso rápido a diferentes vistas

- Área de contenido (Centro): muestra los datos y visualizaciones de la vista seleccionada.

- Panel de detalles (parte inferior): muestra información detallada cuando se seleccionan núcleos o celdas

- Configuración: opciones de apariencia de acceso y preferencias de aplicación

La ventana principal muestra el diseño completo de la interfaz de usuario en modo oscuro

La ventana principal muestra el diseño completo de la interfaz de usuario en modo oscuro

Vistas de navegación

El panel de navegación izquierdo proporciona acceso a seis vistas especializadas:

1. Vista principal

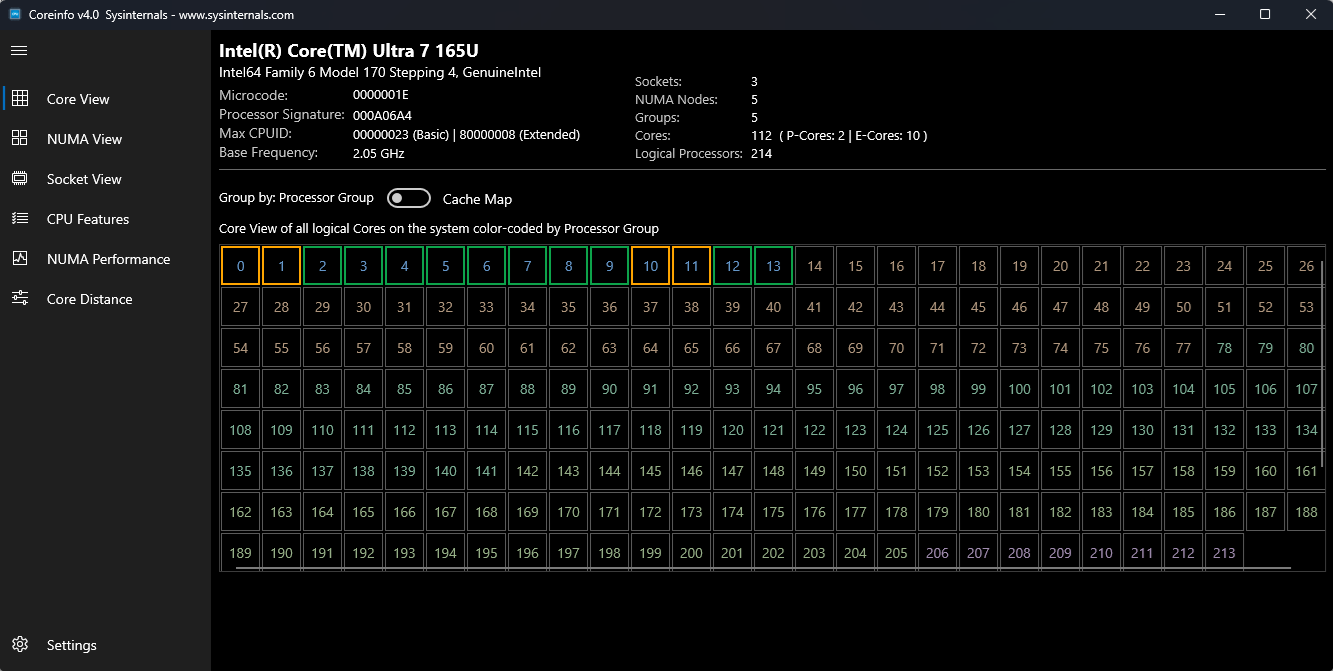

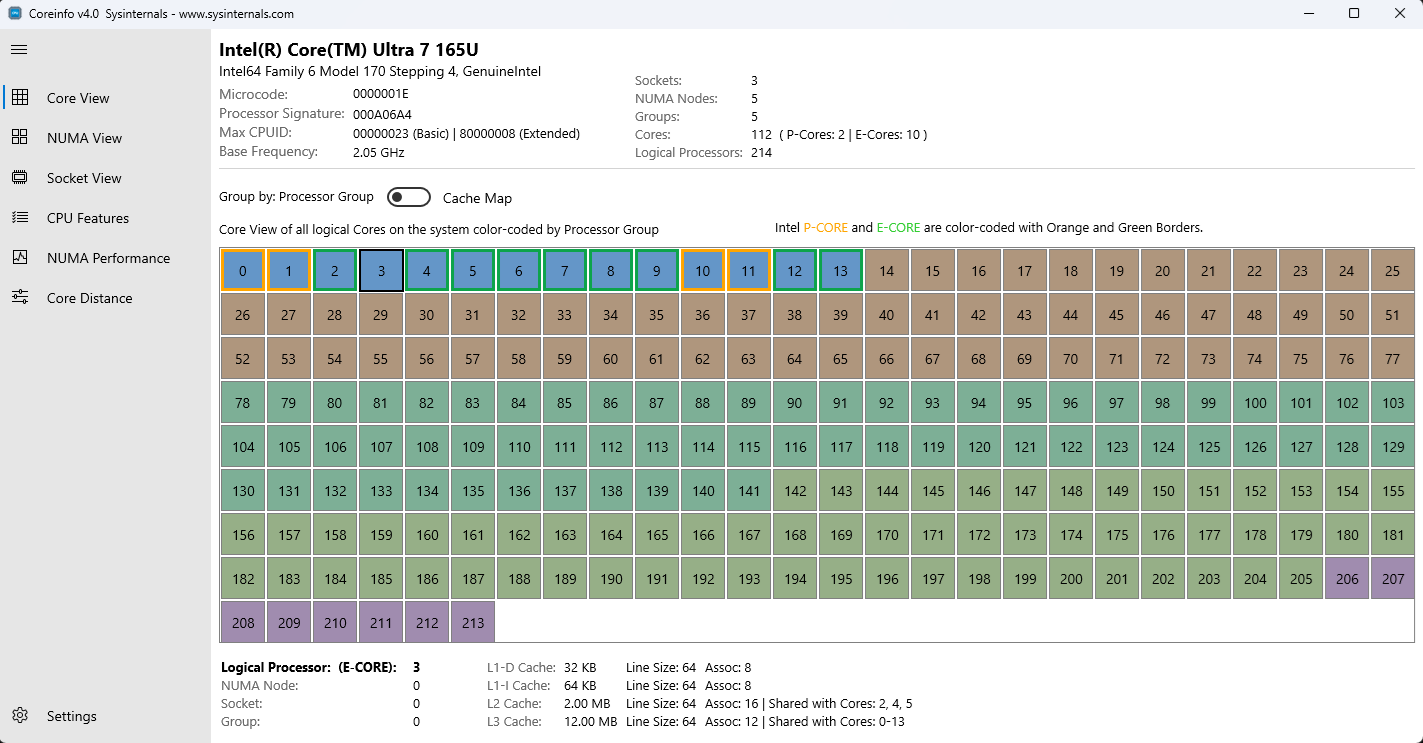

La vista núcleo muestra todos los procesadores lógicos del sistema en un diseño de cuadrícula, mostrando la relación entre los núcleos lógicos y sus recursos físicos.

Características:

- Diseño de cuadrícula: cada celda representa un procesador lógico

-

Indicadores básicos de tipo:

- Núcleos P (núcleos de rendimiento) - coloreados distintivamente

- Núcleos electrónicos (núcleos de eficiencia): coloreado de forma diferente

- Núcleos estándar: coloración predeterminada

- Alternancia de asignación de caché: cambiar entre la vista predeterminada y la vista de jerarquía de caché

- Selección interactiva: haga clic en cualquier núcleo para ver información detallada en el panel inferior.

Información mostrada:

- Número de procesador lógico

- Tipo de núcleo (P-Core/E-Core si procede)

- Niveles de caché asociados (L1, L2, L3)

- Asignación de nodos NUMA

- Asignación de sockets

- Asignación de grupo

que muestra procesadores lógicos en una disposición de cuadrícula

que muestra procesadores lógicos en una disposición de cuadrícula

Información del panel de detalles (cuando se selecciona un núcleo):

- Máscara de procesador y afinidad

- Jerarquía de caché (caché de datos, caché de instrucciones, caché unificada)

- Tamaños de caché y asociatividad

- Tamaños de línea de caché

2. Vista NUMA

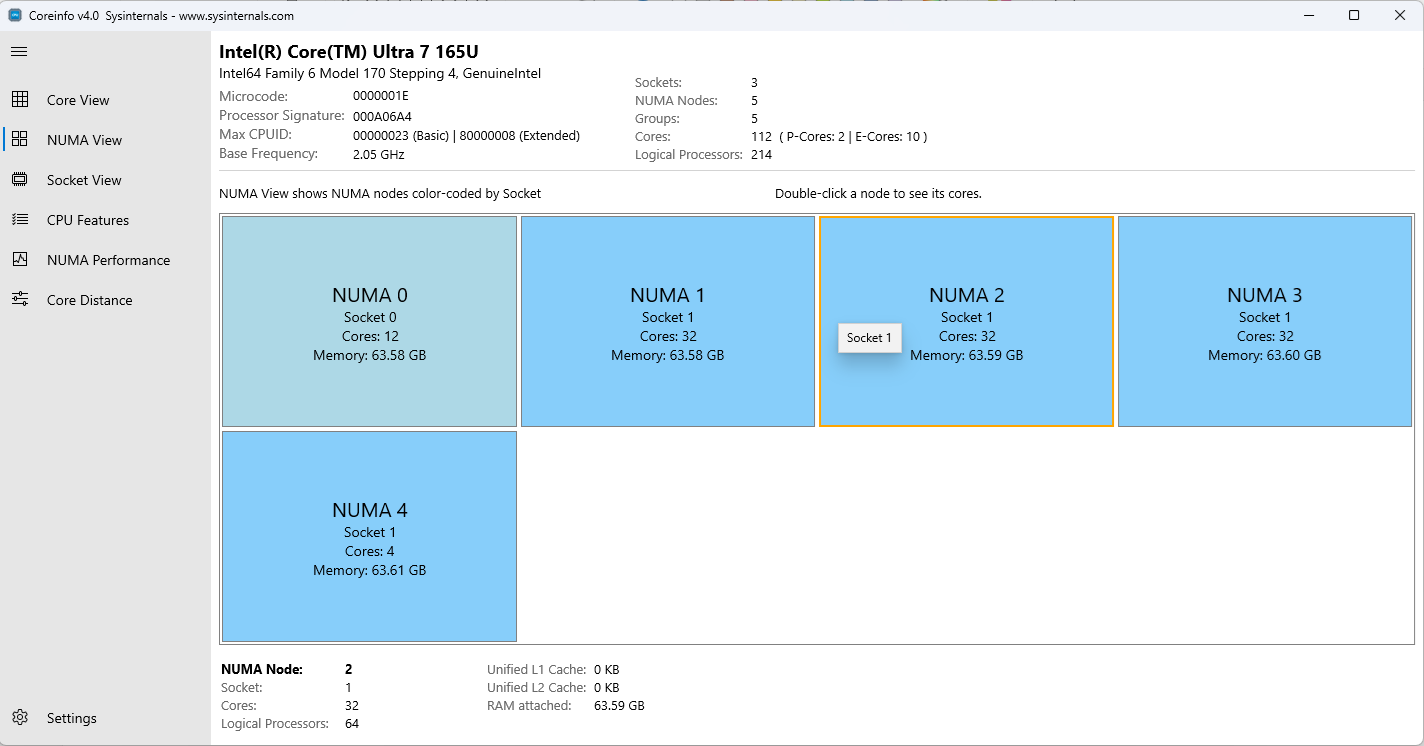

La vista NUMA (acceso a memoria no uniforme) organiza los núcleos por sus asignaciones de nodos NUMA, lo que facilita la comprensión de los patrones de acceso y localidad de memoria.

Características:

- Organización basada en nodos: núcleos agrupados por nodo NUMA

- Núcleos físicos versus lógicos: se muestran ambos recuentos para cada nodo

- Información de memoria: muestra la memoria disponible por nodo NUMA

-

Navegación interactiva:

- Haga clic con un solo clic en un nodo NUMA para mostrar sus detalles en el panel de detalles inferior.

- Haga doble clic en un nodo NUMA para ir a la vista principal que muestra todos los núcleos de ese nodo NUMA seleccionado.

- Presentación jerárquica: muestra la relación entre nodos NUMA y núcleos

Información mostrada:

- Número de nodos NUMA

- Núcleos por nodo NUMA (físico y lógico)

- Capacidad de memoria por nodo

- Distribución principal entre nodos

- Recuento de núcleos centrales de eficiencia (si aplica)

Vista NUMA que muestra los núcleos organizados por nodos NUMA

Vista NUMA que muestra los núcleos organizados por nodos NUMA

Casos de uso:

- Optimización de patrones de acceso a memoria

- Descripción del rendimiento de aplicaciones compatibles con NUMA

- Planificación de la distribución de procesos y subprocesos para obtener un rendimiento óptimo

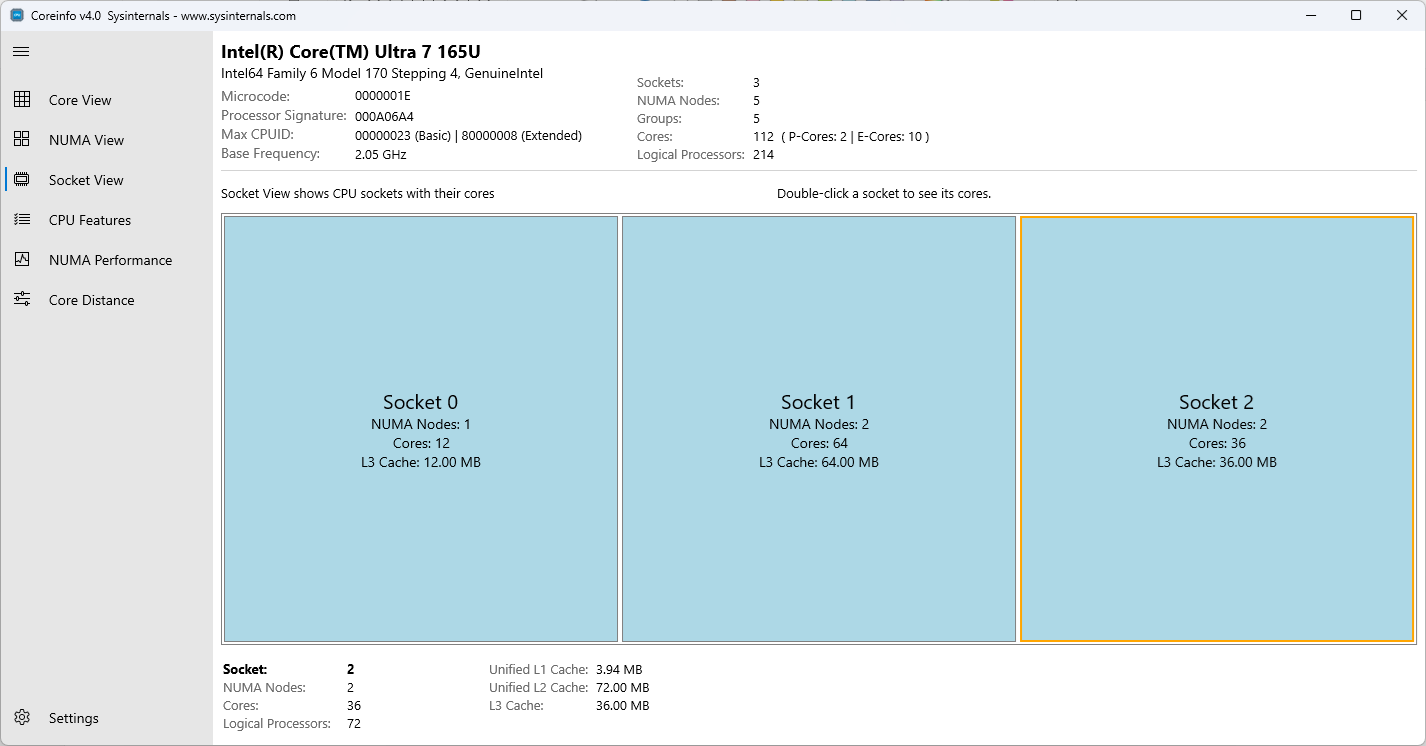

3. Vista de socket

La Vista de Socket muestra los núcleos organizados por su socket de CPU físico, útil para comprender los sistemas de varios sockets y la distribución de recursos a nivel de socket.

Características:

- Agrupación basada en socket: los núcleos organizados por un socket físico

- Información de socket: recuento de sockets y distribución de núcleos

-

Navegación interactiva:

- Haga clic con un solo clic en un socket para mostrar sus detalles en el panel de detalles inferior.

- Haga doble clic en un socket para ir a la vista núcleo en la que se muestran todos los núcleos de ese socket seleccionado.

- Uso compartido de caché: visualización de los núcleos que comparten cachés de nivel de socket

Información mostrada:

- Número de sockets físicos

- Núcleos por socket (físico y lógico)

- Información de caché de nivel de socket

- Nodos NUMA por zócalo

Vista de Socket que muestra los núcleos organizados por zócalos de CPU

Vista de Socket que muestra los núcleos organizados por zócalos de CPU

Casos de uso:

- Análisis del sistema de múltiples sockets

- Descripción de los costos de comunicación entre sockets

- Planeamiento de la distribución de cargas de trabajo en servidores de varios sockets

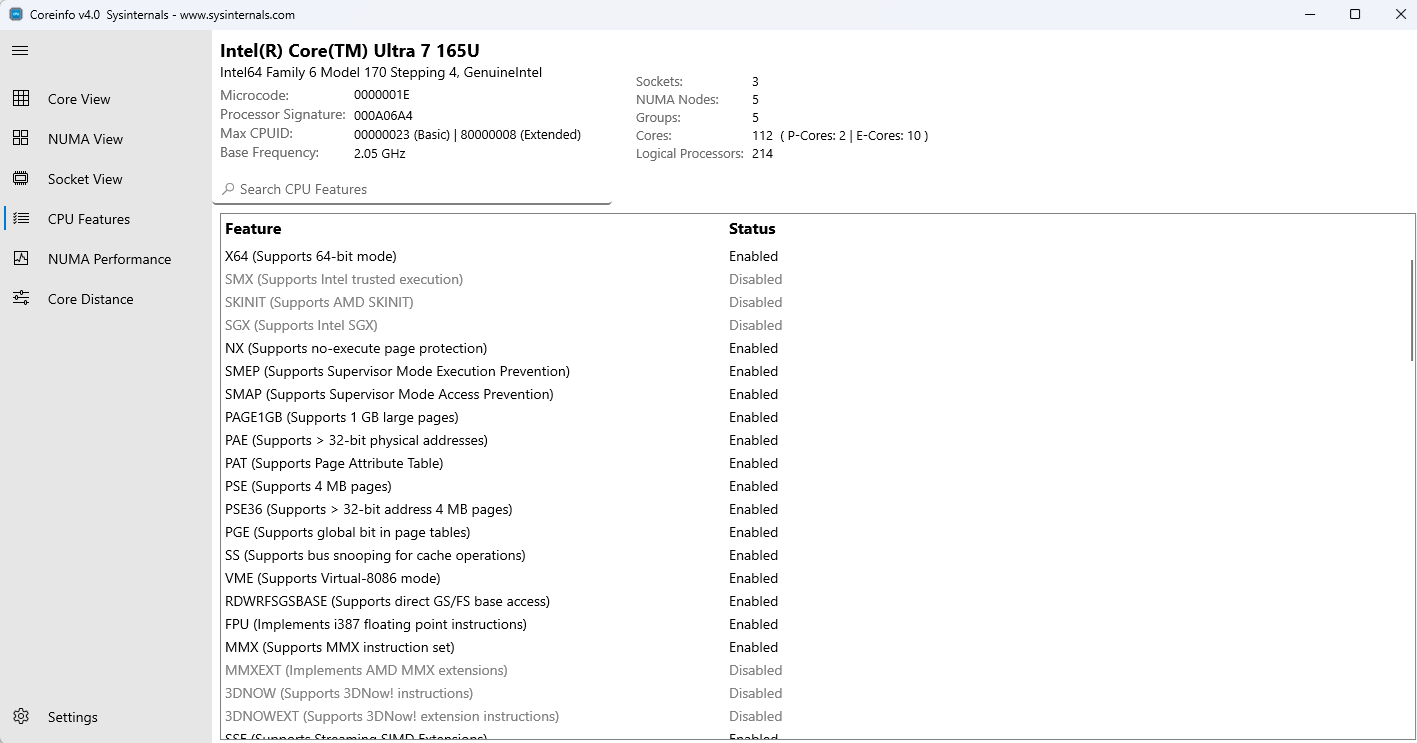

4. Vista de características de CPU

La vista Características de CPU muestra una lista completa de las funcionalidades del procesador, las extensiones del conjunto de instrucciones y las características de hardware compatibles con la CPU.

Características:

- Lista que se puede buscar: buscar rápidamente características específicas de CPU mediante la barra de búsqueda

-

Indicadores de estado: clara indicación visual de las características admitidas o no admitidas usando codificación de colores

- Las características admitidas se muestran en color normal

- Las características no admitidas o deshabilitadas están atenuadas

-

Categorías de características:

- Virtualización (VMX, SVM, HIPERVISOR)

- Compatibilidad de 64 bits (EM64T, NX)

- Conjuntos de instrucciones (SSE, AVX, AES, etc.)

- Administración de energía (EIST, ACPI, Termal)

- Características de seguridad (SMX, SKINIT)

- Características de memoria (PAE, PAT, PSE)

- Características de depuración y supervisión

Información mostrada:

- Abreviatura de características

- Estado de la característica (compatible o no compatible)

- Descripción completa de las características (en el panel de detalles)

Vista de características de la CPU que muestra la lista de capacidades del procesador

Vista de características de la CPU que muestra la lista de capacidades del procesador

Nota: Algunas características de virtualización (como VMX, SVM) se pueden notificar incorrectamente como no disponibles cuando se ejecutan con un hipervisor activo o cuando se ejecutan desde una máquina virtual. Coreinfo debe ejecutarse en un sistema sin que un hipervisor esté en ejecución para obtener resultados precisos.

Casos de uso:

- Comprobación de la disponibilidad del conjunto de instrucciones antes de implementar aplicaciones

- Comprobación de la compatibilidad con la virtualización

- Descripción de la generación y las funcionalidades del procesador

- Depuración de problemas de rendimiento relacionados con las características de CPU que faltan

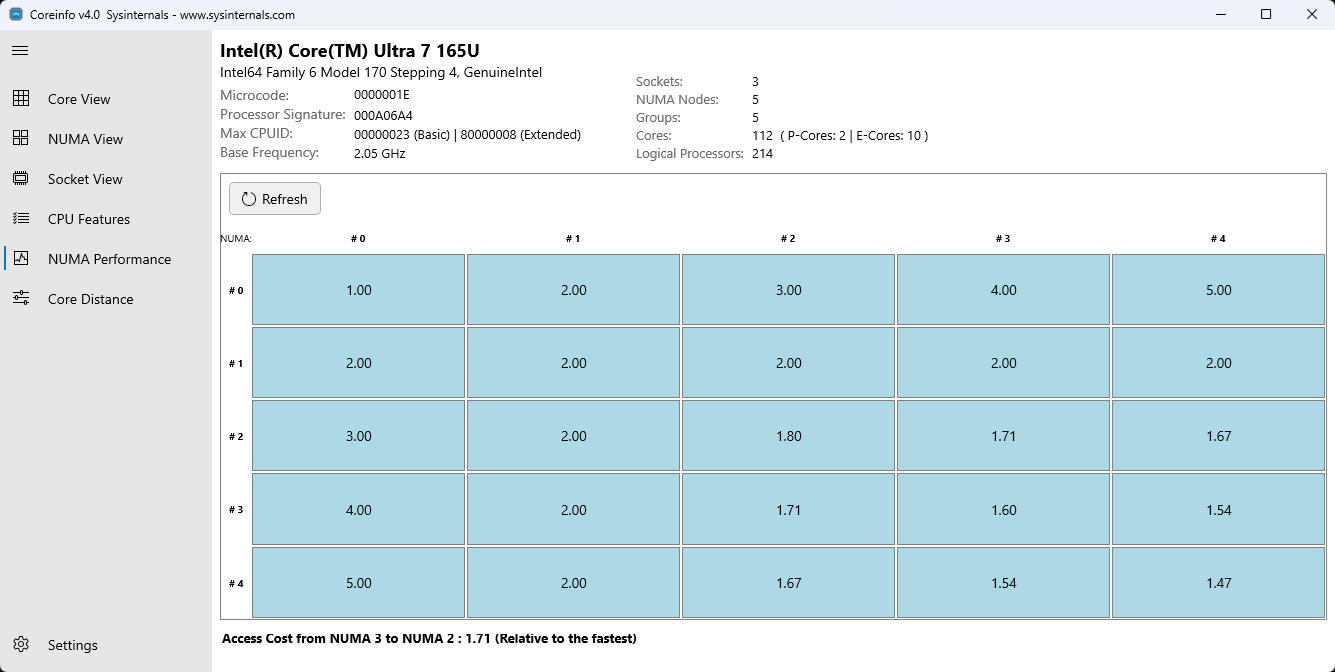

5. Vista de rendimiento NUMA

La vista de rendimiento de NUMA proporciona una visualización de cuadrícula que muestra los costos de acceso a la memoria entre nodos NUMA, lo que ayuda a identificar cuellos de botella de rendimiento en sistemas NUMA.

Características:

- Visualización de cuadrícula: matriz que muestra los costos de acceso a la memoria relativa entre nodos NUMA

- Matriz interactiva: mantenga el puntero sobre las celdas para ver información detallada sobre el rendimiento

- Actualizaciones en Tiempo Real: Los datos de rendimiento se actualizan dinámicamente al seleccionar el botón Actualizar

- Visualización de costos relativos: muestra el costo relativo de acceder a la memoria desde distintos nodos NUMA.

Información mostrada:

- Matriz de NxN donde N = número de nodos NUMA

- Costo de acceso a memoria del nodo NUMA de origen (fila) al nodo NUMA de destino (columna)

- Valores numéricos que muestran los costos de rendimiento relativos

- Las celdas diagonales muestran el acceso a la memoria local (normalmente el costo más bajo)

Grilla de rendimiento de NUMA que muestra los costos de acceso a la memoria

Grilla de rendimiento de NUMA que muestra los costos de acceso a la memoria

Descripción de la cuadrícula:

- Elementos diagonales: representan el acceso a memoria local (nodo que accede a su propia memoria): normalmente los valores más bajos

- Elementos fuera de la diagonal: representan el acceso a memoria remota con mayores costos relativos

- Simetría: la matriz puede no ser perfectamente simétrica, ya que los costos de acceso pueden variar según la dirección.

Casos de uso:

- Identificación de cuellos de botella de rendimiento relacionados con NUMA

- Optimización de estrategias de asignación de memoria

- Planeamiento del proceso o anclaje de subprocesos para sistemas NUMA

- Descripción de las penalizaciones de acceso a memoria entre nodos

Vista de Distancia del Núcleo

La vista Distancia básica muestra un mapa térmico detallado de los costos de comunicación entre núcleos de CPU individuales, lo que proporciona información sobre la latencia de núcleo a núcleo y la eficacia de la comunicación.

Características:

-

Mapa de calor a nivel de núcleo: matriz codificada por color que muestra las distancias relativas entre núcleos

- Verde/Azul = Baja latencia (mismo clúster principal, caché compartida)

- Amarillo/Naranja = Latencia media (mismo socket, clúster diferente)

- Rojo = latencia alta (socket diferente o nodo NUMA)

- Exploración interactiva: mantenga el puntero sobre el lienzo de la cuadrícula para ver información detallada de distancia

- Análisis pormenorizados: muestra las relaciones de núcleo a núcleo con la mejor granularidad

- Actualización dinámica: use el botón Actualizar para obtener dinámicamente los datos de distancia de núcleo actualizados.

Información mostrada:

- Matriz de NxN donde N = número de procesadores lógicos

- Distancia relativa o latencia del núcleo de origen (fila) al núcleo de destino (columna)

- Codificación de colores para la identificación visual rápida de las relaciones principales

- Métricas de distancia detalladas en el panel de detalles

Mapa térmico de la Vista de Distancia del Núcleo que muestra los costos de comunicación de núcleo a núcleo

Descripción del mapa de distancia:

- Elementos diagonales: siempre cero (núcleo a sí mismo)

- Distancia baja (verde): núcleos comparten caché L2 o L3

- Distancia media (amarillo):núcleos en el mismo socket, pero dominios de caché diferentes

- Distancia alta (rojo): núcleos en diferentes sockets o nodos NUMA

Casos de uso:

- Optimización de afinidad de hilos

- Descripción de los dominios de coherencia de caché

- Identificación de pares de núcleos óptimos para comunicar hilos

- Análisis del rendimiento de aplicaciones multiproceso

- Planeación de estrategias de anclaje de CPU para aplicaciones de baja latencia

Características interactivas

Selección y detalles principales

Al hacer clic en un núcleo en cualquier vista (Core, NUMA o Socket) se muestra información detallada en el panel de detalles inferior:

- Información del procesador: número de procesador lógico, máscara y afinidad

-

Jerarquía de caché:

- Caché de datos L1 (tamaño, asociatividad, tamaño de línea)

- Caché de instrucciones L1 (tamaño, asociatividad, tamaño de línea)

- Caché L2 (tamaño, asociatividad, tamaño de línea)

- Caché L3 (tamaño, asociatividad, tamaño de línea)

- Información de topología: asignaciones de grupos, sockets y nodos NUMA

- Tipo de núcleo: P-Core, E-Core o designación de núcleo estándar

Funcionalidad de búsqueda

La vista Características de CPU incluye una barra de búsqueda que permite localizar rápidamente características específicas del procesador:

- Haga clic en el icono de búsqueda.

- Escriba el nombre o la abreviatura de la característica.

- La lista filtra automáticamente para mostrar las características coincidentes.

- Borrar la búsqueda para restaurar la lista completa

Alternancia de mapa de caché

En la vista principal, cambie entre dos modos de visualización:

- Modo predeterminado: muestra los núcleos en su disposición lógica

- Modo de asignación de caché: reorganiza los núcleos para visualizar las relaciones de uso compartido de caché

Navegación entre vistas

- Usar el panel de navegación izquierdo para cambiar entre vistas

- Al visualizar un nodo o socket NUMA específico, al hacer clic en la misma vista de nuevo, regresa a la vista general.

- La vista actual está resaltada en el panel de navegación

Configuración y personalización

Acceda a la configuración a través de la opción Configuración en el menú de navegación.

Configuración de apariencia

Opciones de tema:

- Luz: combinación de colores claro optimizada para entornos brillantes

- Oscuro: combinación de colores oscuro para reducir la tensión ocular

- Valor predeterminado del sistema: coincide automáticamente con la preferencia de tema de Windows

Save To File (Guardar en el archivo)

Exportar datos de topología principales:

- Use la opción Guardar en para volcar los datos de topología principal en un archivo.

- El formato de salida es idéntico a la salida de la herramienta de línea de comandos.

Descripción de la topología del sistema

Tipos principales (arquitectura híbrida)

Las CPU modernas pueden presentar arquitecturas híbridas con diferentes tipos principales:

- Núcleos P (rendimiento): núcleos optimizados para un alto rendimiento en cargas de trabajo de un solo núcleo y exigentes

- Núcleos electrónicos (eficiencia): núcleos eficientes energéticamente optimizados para tareas en segundo plano y cargas de trabajo multiproceso

La interfaz de usuario de Coreinfo identifica y diferencia claramente estos tipos principales en todas las vistas aplicables.

Arquitectura NUMA

¿Qué es NUMA? El acceso a memoria no uniforme (NUMA) es un diseño de memoria donde cada procesador tiene memoria local a la que puede acceder rápidamente y a la memoria remota que requiere comunicación entre procesadores.

Por qué importa:

- El acceso a memoria local es significativamente más rápido que el acceso remoto

- El rendimiento de la aplicación puede verse afectado drásticamente por la colocación de NUMA

- Descripción de la topología NUMA es fundamental para la informática de alto rendimiento

Uso de la interfaz de usuario de Coreinfo para la optimización de NUMA:

- Uso de la vista NUMA para comprender la topología NUMA del sistema

- Verifique la vista de rendimiento de NUMA para comprobar los costos de acceso de memoria.

- Optimización de la ubicación de subprocesos y procesos según las asignaciones de nodos NUMA

- Utilice Vista de Distancia de Núcleo para comprender la comunicación de núcleo a núcleo dentro y entre nodos NUMA

Jerarquía de caché

Niveles de caché:

- Caché L1: menor y más rápido, dividido en cachés de datos e instrucciones

- Caché L2: caché unificada más grande, normalmente privada para cada núcleo

- Caché L3: caché unificada más grande, a menudo compartida entre varios núcleos

Uso de la información de caché:

- Comprender qué núcleos comparten recursos de caché

- Optimización de la localidad de datos para núcleos de uso compartido de caché

- Usar el modo de asignación de caché en la vista principal para visualizar dominios de caché

Uso de Coreinfo desde la línea de comandos

Para cada recurso se muestra un mapa de los procesadores visibles para el sistema operativo que corresponden a los recursos especificados, con "*" que representa los procesadores aplicables. Por ejemplo, en un sistema de 4 núcleos, una línea en la salida de caché con un mapa compartido por núcleos 3 y 4.

Uso:

coreinfo [-c][-f][-g][-l][-n][-s][-m][-v]

| Parámetro | Descripción |

|---|---|

| -c | Volcar información sobre los núcleos. |

| -f | Información de características principales de volcado de memoria. |

| -g | Volcado de información sobre grupos. |

| -l | Volcado de información sobre las memorias caché. |

| -n | Volcado de información sobre nodos NUMA. |

| -s | Volcado de información sobre sockets. |

| -m | Costo de acceso de NUMA de volcado. |

| -v | Volcar solo características relacionadas con la virtualización, incluida la compatibilidad con la traducción de direcciones de segundo nivel. (requiere derechos administrativos en sistemas Intel). |

Todas las opciones excepto -v se seleccionan de forma predeterminada.

Salida de Coreinfo:

Coreinfo v4.0 - Dump information on system CPU and memory topology

Copyright © 2008-2025 Mark Russinovich

Sysinternals - www.sysinternals.com

Intel(R) Core(TM) Ultra 7 165U

Intel64 Family 6 Model 170 Stepping 4, GenuineIntel

Microcode signature: 0000001E

Processor signature: 000A06A4

Maximum implemented CPUID leaves: 00000023 (Basic), 80000008 (Extended).

Maximum implemented address width: 48 bits (virtual), 46 bits (physical).

HTT * Hyperthreading enabled

CET * Supports Control Flow Enforcement Technology

Kernel CET - Kernel-mode CET Enabled

User CET * User-mode CET Allowed

X64 * Supports 64-bit mode

SMX - Supports Intel trusted execution

SKINIT - Supports AMD SKINIT

SGX - Supports Intel SGX

NX * Supports no-execute page protection

SMEP * Supports Supervisor Mode Execution Prevention

SMAP * Supports Supervisor Mode Access Prevention

PAGE1GB * Supports 1 GB large pages

PAE * Supports > 32-bit physical addresses

PAT * Supports Page Attribute Table

PSE * Supports 4 MB pages

PSE36 * Supports > 32-bit address 4 MB pages

PGE * Supports global bit in page tables

SS * Supports bus snooping for cache operations

VME * Supports Virtual-8086 mode

RDWRFSGSBASE * Supports direct GS/FS base access

FPU * Implements i387 floating point instructions

MMX * Supports MMX instruction set

MMXEXT - Implements AMD MMX extensions

3DNOW - Supports 3DNow! instructions

3DNOWEXT - Supports 3DNow! extension instructions

SSE * Supports Streaming SIMD Extensions

SSE2 * Supports Streaming SIMD Extensions 2

SSE3 * Supports Streaming SIMD Extensions 3

SSSE3 * Supports Supplemental SIMD Extensions 3

SSE4a - Supports Streaming SIMDR Extensions 4a

SSE4.1 * Supports Streaming SIMD Extensions 4.1

SSE4.2 * Supports Streaming SIMD Extensions 4.2

AES * Supports AES extensions

AVX * Supports AVX instruction extensions

AVX2 * Supports AVX2 instruction extensions

AVX-512-F - Supports AVX-512 Foundation instructions

AVX-512-DQ - Supports AVX-512 double and quadword instructions

AVX-512-IFAMA - Supports AVX-512 integer Fused multiply-add instructions

AVX-512-PF - Supports AVX-512 prefetch instructions

AVX-512-ER - Supports AVX-512 exponential and reciprocal instructions

AVX-512-CD - Supports AVX-512 conflict detection instructions

AVX-512-BW - Supports AVX-512 byte and word instructions

AVX-512-VL - Supports AVX-512 vector length instructions

FMA * Supports FMA extensions using YMM state

MSR * Implements RDMSR/WRMSR instructions

MTRR * Supports Memory Type Range Registers

XSAVE * Supports XSAVE/XRSTOR instructions

OSXSAVE * Supports XSETBV/XGETBV instructions

RDRAND * Supports RDRAND instruction

RDSEED * Supports RDSEED instruction

CMOV * Supports CMOVcc instruction

CLFSH * Supports CLFLUSH instruction

CX8 * Supports compare and exchange 8-byte instructions

CX16 * Supports CMPXCHG16B instruction

BMI1 * Supports bit manipulation extensions 1

BMI2 * Supports bit manipulation extensions 2

ADX * Supports ADCX/ADOX instructions

DCA - Supports prefetch from memory-mapped device

F16C * Supports half-precision instruction

FXSR * Supports FXSAVE/FXSTOR instructions

FFXSR - Supports optimized FXSAVE/FSRSTOR instruction

MONITOR * Supports MONITOR and MWAIT instructions

MOVBE * Supports MOVBE instruction

ERMSB * Supports Enhanced REP MOVSB/STOSB

PCLMULDQ * Supports PCLMULDQ instruction

POPCNT * Supports POPCNT instruction

LZCNT * Supports LZCNT instruction

SEP * Supports fast system call instructions

LAHF-SAHF * Supports LAHF/SAHF instructions in 64-bit mode

HLE - Supports Hardware Lock Elision instructions

RTM - Supports Restricted Transactional Memory instructions

DE * Supports I/O breakpoints including CR4.DE

DTES64 - Can write history of 64-bit branch addresses

DS - Implements memory-resident debug buffer

DS-CPL - Supports Debug Store feature with CPL

PCID * Supports PCIDs and settable CR4.PCIDE

INVPCID * Supports INVPCID instruction

PDCM * Supports Performance Capabilities MSR

RDTSCP * Supports RDTSCP instruction

TSC * Supports RDTSC instruction

TSC-DEADLINE * Local APIC supports one-shot deadline timer

TSC-INVARIANT * TSC runs at constant rate

xTPR * Supports disabling task priority messages

EIST * Supports Enhanced Intel Speedstep

ACPI * Implements MSR for power management

TM * Implements thermal monitor circuitry

TM2 * Implements Thermal Monitor 2 control

APIC * Implements software-accessible local APIC

x2APIC * Supports x2APIC

CNXT-ID - L1 data cache mode adaptive or BIOS

MCE * Supports Machine Check, INT18 and CR4.MCE

MCA * Implements Machine Check Architecture

PBE * Supports use of FERR#/PBE# pin

PSN - Implements 96-bit processor serial number

HTT * Hyperthreading

PREFETCHW * PrefetchW instruction support

HYPERVISOR * Hypervisor is present

VMX - Supports Intel hardware-assisted virtualization

EPT - Supports Intel extended page tables (SLAT)

URG - Supports Intel unrestricted guest

Logical to Physical Processor Map:

**------------ Physical Processor 0 (Hyperthreaded)

--*----------- Physical Processor 1

---*---------- Physical Processor 2

----*--------- Physical Processor 3

-----*-------- Physical Processor 4

------*------- Physical Processor 5

-------*------ Physical Processor 6

--------*----- Physical Processor 7

---------*---- Physical Processor 8

----------**-- Physical Processor 9 (Hyperthreaded)

------------*- Physical Processor 10

-------------* Physical Processor 11

Logical Processor to Socket Map:

************** Socket 0

Logical Processor to NUMA Node Map:

************** NUMA Node 0

No NUMA nodes.

Logical Processor to Cache Map:

**------------ Data Cache 0, Level 1, 48 KB, Assoc 12, LineSize 64

**------------ Instruction Cache 0, Level 1, 64 KB, Assoc 16, LineSize 64

**------------ Unified Cache 0, Level 2, 2 MB, Assoc 16, LineSize 64

************-- Unified Cache 1, Level 3, 12 MB, Assoc 12, LineSize 64

--*----------- Data Cache 1, Level 1, 32 KB, Assoc 8, LineSize 64

--*----------- Instruction Cache 1, Level 1, 64 KB, Assoc 8, LineSize 64

--****-------- Unified Cache 2, Level 2, 2 MB, Assoc 16, LineSize 64

---*---------- Data Cache 2, Level 1, 32 KB, Assoc 8, LineSize 64

---*---------- Instruction Cache 2, Level 1, 64 KB, Assoc 8, LineSize 64

----*--------- Data Cache 3, Level 1, 32 KB, Assoc 8, LineSize 64

----*--------- Instruction Cache 3, Level 1, 64 KB, Assoc 8, LineSize 64

-----*-------- Data Cache 4, Level 1, 32 KB, Assoc 8, LineSize 64

-----*-------- Instruction Cache 4, Level 1, 64 KB, Assoc 8, LineSize 64

------*------- Data Cache 5, Level 1, 32 KB, Assoc 8, LineSize 64

------*------- Instruction Cache 5, Level 1, 64 KB, Assoc 8, LineSize 64

------****---- Unified Cache 3, Level 2, 2 MB, Assoc 16, LineSize 64

-------*------ Data Cache 6, Level 1, 32 KB, Assoc 8, LineSize 64

-------*------ Instruction Cache 6, Level 1, 64 KB, Assoc 8, LineSize 64

--------*----- Data Cache 7, Level 1, 32 KB, Assoc 8, LineSize 64

--------*----- Instruction Cache 7, Level 1, 64 KB, Assoc 8, LineSize 64

---------*---- Data Cache 8, Level 1, 32 KB, Assoc 8, LineSize 64

---------*---- Instruction Cache 8, Level 1, 64 KB, Assoc 8, LineSize 64

----------**-- Data Cache 9, Level 1, 48 KB, Assoc 12, LineSize 64

----------**-- Instruction Cache 9, Level 1, 64 KB, Assoc 16, LineSize 64

----------**-- Unified Cache 4, Level 2, 2 MB, Assoc 16, LineSize 64

------------*- Data Cache 10, Level 1, 32 KB, Assoc 8, LineSize 64

------------*- Instruction Cache 10, Level 1, 64 KB, Assoc 8, LineSize 64

------------** Unified Cache 5, Level 2, 2 MB, Assoc 16, LineSize 64

-------------* Data Cache 11, Level 1, 32 KB, Assoc 8, LineSize 64

-------------* Instruction Cache 11, Level 1, 64 KB, Assoc 8, LineSize 64

Logical Processor to Group Map:

************** Group 0

Descargar Coreinfo(3 MB)Ejecutar ahora desde Sysinternals Live.

Descargar Coreinfo(3 MB)Ejecutar ahora desde Sysinternals Live.

Se ejecuta en:

- Cliente: Windows 11 y versiones posteriores.

- Servidor: Windows Server 2016 y versiones posteriores.