État de prise en charge de MT3620

Ce document décrit la status actuelle de la prise en charge d’Azure Sphere pour mediaTek MT3620. Vous pouvez également consulter la documentation relative au produit MT3620, disponible en téléchargement sur la page web de MediaTek MT3620. En outre, MediaTek produit le Guide de l’utilisateur du matériel MT3620, qui est un guide détaillé pour l’intégration du MCU MT3620 dans votre propre matériel.

Important

Dans le contexte de ce document, non pris en charge actuellement signifie que l’utilisation de la fonctionnalité par les clients est limitée à l’heure actuelle, et cette restriction est susceptible d’être supprimée à l’avenir. À l’inverse, non accessible signifie que la fonctionnalité ne peut pas être utilisée par les clients, et cette restriction est peu susceptible de changer.

Si vous avez des demandes de fonctionnalités ou des commentaires, vos commentaires sont les bienvenus sur le forum de la communauté Azure Sphere.

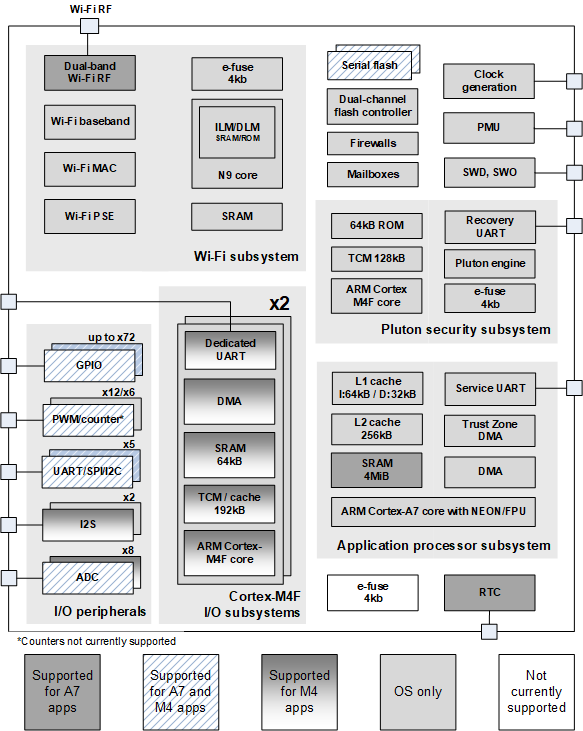

Diagramme de blocs MT3620

Le diagramme de blocs montre la prise en charge fournie pour chaque composant MT3620. Les sections qui suivent le diagramme fournissent des détails supplémentaires sur ces composants.

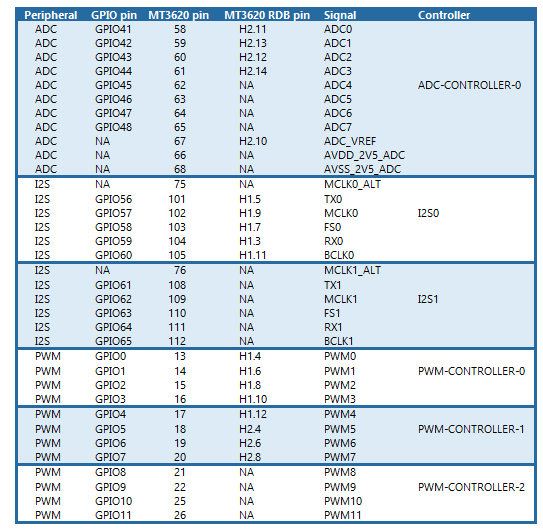

Périphériques d’E/S

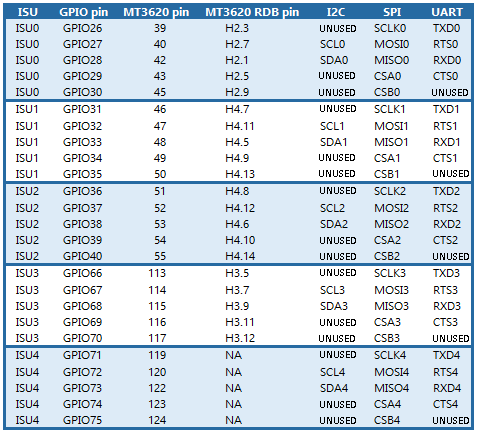

La conception du MT3620 comprend un total de 76 broches d’E/S programmables. Comme indiqué dans les deux tableaux suivants, la plupart des broches sont multiplexées entre les E/S à usage général (GPIO) et d’autres fonctions. En plus des broches GPIO répertoriées, GPIO12-23 sont disponibles sur les broches MT3620 27-38 respectivement.

En se référant au tableau suivant, les broches marquées « UNUSED » ne sont pas utilisées par le périphérique ISU associé et peuvent être configurées pour être utilisées en tant que broches GPIO.

Note

Une fois qu’un périphérique ISU a été alloué à un cœur, les 5 broches ISU, y compris les broches inutilisées, sont limitées à l’utilisation dans ce cœur.

GPIO/PWM/compteurs

Certaines broches sont multiplexées entre GPIO, la modulation de largeur d’impulsion (PWM) et les compteurs matériels.

Les fonctions GPIO actuellement prises en charge définissent la sortie haute/faible et l’entrée de lecture. Les modes de conduite d’évacuation/open source ouverts et le contrôle de la force de conduite sont également pris en charge. Les interruptions externes sont prises en charge sur le cœur M4, mais pas sur le cœur A7.

Le MT3620 a 12 canaux PWM, identifiés par PWM0-PWM11. Ils sont organisés en 3 groupes de 4 canaux. Chaque groupe est associé à un contrôleur PWM (PWM-CONTROLLER-0, PWM-CONTROLLER-1, PWM-CONTROLLER-2). Les canaux PWM et les épingles GPIO GPIO0 à GPIO11 sont mappés aux mêmes broches sur le MT3620. Si votre application utilise un contrôleur PWM, toutes les broches associées à ce contrôleur sont allouées pour être utilisées comme sorties PWM et aucune d’entre elles ne peut être utilisée pour GPIO.

Le matériel PWM peut être configuré pour utiliser l’une des trois fréquences d’horloge fixe : 32 KHz, 2 MHz (XTAL/13) ou 26 MHz (XTAL). Sur les cœurs en temps réel (RT), une application en temps réel (RTApp) peut sélectionner l’horloge à utiliser comme base. Sur le cœur de haut niveau (A7), le pilote Linux utilise toujours l’horloge de 2 MHz. Cela entraîne des limitations de cycle de service et de période dans les applications de haut niveau, comme expliqué dans Utiliser des PWM dans des applications de haut niveau.

Blocs d’interface série (ISU)

La conception MT3620 comprend cinq blocs d’interface série, chacun contenant cinq broches. (Ces blocs sont également appelés ISU, pour « I2C, SPI, UART. ») Ces blocs d’interface série peuvent multiplexer GPIO, UART (Universal Asynchrone Receiver-Émetteur), I2C (Inter-integrated Circuit) et SPI (Serial Peripheral Interface).

UART est pris en charge à 1200, 2400, 4800, 9600, 19200, 38400, 57600, 115200, 230400, 460800, 500000, 576000, 921600, 1000000, 11520000, 1500000 et 2000000 baud. Il existe une mémoire tampon de réception matérielle de 32 octets. Les paramètres UART suivants sont pris en charge, avec 8N1 (8 bits de données, 1 bit d’arrêt et aucune parité) comme paramètre par défaut :

- Bit de données : 5, 6, 7 et 8.

- Bit d’arrêt : 1 et 2.

- Parité : impair, pair et aucun.

- Mode de contrôle de flux : RTS/CTS, XON/XOFF et aucun contrôle de flux.

Les transactions SPI sont prises en charge jusqu’à 40 MHz. Vous pouvez connecter jusqu’à deux appareils SPI subordonnés à chaque ISU. Lorsque vous utilisez un port ISU comme interface spi master, vous ne pouvez pas utiliser le même port qu’une interface I2C ou UART. Les opérations SPI en lecture et en écriture bidirectionnelles simultanées (duplex intégral) au sein d’une transaction de bus unique ne sont pas prises en charge. Les paramètres SPI suivants sont pris en charge :

- Mode de communication (polarité de l’horloge, phase d’horloge) : mode SPI 0 (CPOL = 0, CPHA = 0), mode SPI 1 (CPOL = 0, CPHA = 1), mode SPI 2 (CPOL = 1, CPHA = 0) et mode SPI 3 (CPOL = 1, CPHA = 1).

- Ordre des bits : le moins significatif est envoyé en premier, et le plus significatif est envoyé en premier.

- Polarité de sélection de puce : actif-élevé, actif-bas. Actif-bas est le paramètre par défaut.

Les adresses d’appareils subordonnés 7 bits sont prises en charge pour I2C. Les adresses subordonnées I2C 8 bits ou 10 bits ne sont pas prises en charge. Lorsque vous utilisez un port ISU comme interface de master I2C, vous ne pouvez pas utiliser le même port qu’une interface SPI ou UART. Les lectures I2C de 0 octet ne sont pas prises en charge. Les paramètres I2C suivants sont pris en charge :

- Vitesses de bus 100 KHz, 400 KHz et 1 MHz.

- Délai d’expiration personnalisé pour les opérations.

I2S

Deux blocs de cinq broches sont multiplexés entre GPIO et I2S. I2S est actuellement pris en charge pour les applications M4 uniquement.

ADC

Le MT3620 contient un ADC 12 bits avec 8 canaux d’entrée. Un bloc de huit broches est multiplexé entre GPIO et ADC. Les canaux d’entrée ADC et les broches GPIO GPIO41 à GPIO48 correspondent aux mêmes broches sur le MT3260. Toutefois, si votre application utilise l’ADC, les 8 broches sont allouées pour être utilisées en tant qu’entrées ADC et aucune d’entre elles ne peut être utilisée pour GPIO.

Sous-systèmes ARM Cortex-M4F

Le MT3620 comprend deux sous-systèmes ARM Cortex-M4F à usage général, chacun disposant d’un bloc GPIO/UART dédié.

Le MT3620 prend en charge une fréquence d’horloge par défaut de 26 MHz. Toutefois, chaque cœur M4 peut être configuré indépendamment pour s’exécuter à n’importe quelle fréquence d’horloge comprise entre 1 MHz et 200 MHz en définissant son registre HCLK_CK_CTRL. Le code suivant illustre une façon de définir la fréquence d’horloge sur 200 MHz :

volatile unsigned int *hclk_ck_ctrl = (unsigned int *)0x2101000c;

*hclk_ck_ctrl = 0x00040200;

Note

Pour plus d’informations sur la programmation des cœurs M4 sur le MT3620, consultez la documentation MT3620 publiée par MediaTek. Si la feuille de données ne contient pas toutes les informations dont vous avez besoin, envoyez un e-mail à Avnet (Azure.Sphere@avnet.com) pour demander la feuille de données complète.

Les sous-systèmes ARM Cortex-M4F peuvent être programmés pour prendre en charge les interruptions externes. Pour plus d’informations, consultez Utiliser des interruptions externes dans des applications compatibles en temps réel .

Sous-système du processeur d’application

Le sous-système ARM Cortex-A7 exécute une application cliente avec le noyau Linux, les services et les bibliothèques fournis par Microsoft.

Le service UART est dédié aux fonctionnalités système du sous-système A7. Il n’est pas disponible pour l’utilisation de l’application cliente.

Le bloc d’e-fusible programmable à usage unique, pour stocker des informations spécifiques à l’appareil, ne peut pas être utilisé par les applications clientes.

sous-système Wi-Fi

Le sous-système Wi-Fi est actuellement conforme à la norme IEEE 802.11 b/g/n à 2,4 GHz et 5 GHz.

Actuellement, Azure Sphere prend uniquement en charge l’authentification WPA2, EAP-TLS et l’authentification ouverte (sans mot de passe).

Pour plus d’informations sur le test et l’étalonnage des fréquences radio , consultez Outils de test RF .

Contrôle de l’alimentation

Le MT3620 inclut des fonctionnalités de mise sous tension et de profil d’alimentation pour contrôler la consommation d’énergie. Pour plus d’informations, consultez Considérations relatives à La mise hors tension et Considérations relatives au profil d’alimentation.

Horloges et sources d’alimentation

Le cristal main ne peut actuellement être que de 26 MHz. Les fréquences crystal autres que 26 MHz ne sont actuellement pas prises en charge dans les logiciels.

Détection du brownout

La détection de brownout n’est actuellement pas prise en charge.

Minuteurs de surveillance du matériel

Le MTK3620 comprend plusieurs minuteurs de surveillance :

- Un minuteur de surveillance dédié à l’utilisation par le domaine de sécurité Pluton. Ce minuteur de surveillance n’est pas disponible pour une utilisation par les applications.

- Un minuteur de surveillance disponible pour le processeur de l’application. Le système d’exploitation Azure Sphere utilise ce minuteur de surveillance pour les services système. Ce minuteur de surveillance n’est pas disponible pour les applications.

- Un minuteur de surveillance pour chacun des cœurs en temps réel. Ces minuteurs de surveillance sont disponibles pour les applications en temps réel.

Pour plus d’informations, consultez Utiliser un minuteur de surveillance dans une rtapp .

SWD, SWO

Le débogage par câble série (SWD, broches 98-99) est pris en charge uniquement pour les applications M4. La sortie de câble série (SWO, broche 100) n’est pas prise en charge actuellement. Le débogage d’une application A7 est pris en charge par un mécanisme gdb fourni par Microsoft.

RAM et flash

Le MT3620 comprend environ 5 Mo de RAM sous-système, dont 256 Kio dans chaque sous-système d’E/S et 4 Mo dans le sous-système d’application A7.

Le MT3620 peut être commandé avec 16 Mo de mémoire flash SPI.

Pour plus d’informations sur la RAM et le flash disponibles pour les applications, consultez Mémoire disponible pour les applications.

Prise en charge des tests de fabrication

La documentation et les utilitaires permettant de prendre en charge l’intégration d’applications de test de fabrication personnalisées avec des processus d’usine ne sont pas encore disponibles.

Brochage

| Épingler# | Nom de l’épingle | Fonctions principales | Type | Description | Commentaires |

|---|---|---|---|---|---|

| 1 | GND | P | Sol | ||

| 2 | AVDD_3V3_WF_A_PA | PI | Rail d’alimentation 3,3 V pour amplificateur de puissance Wi-Fi 5 GHz | ||

| 3 | AVDD_3V3_WF_A_PA | PI | Rail d’alimentation 3,3 V pour amplificateur de puissance Wi-Fi 5 GHz | ||

| 4 | NC | ||||

| 5 | NC | ||||

| 6 | AVDD_1V6_WF_TRX | PI | Rail d’alimentation 1,6 V pour Wi-Fi transmission/réception | ||

| 7 | AVDD_1V6_WF_AFE | PI | Rail d’alimentation 1.6V pour Wi-Fi front-end analogique | ||

| 8 | NC | ||||

| 9 | AVDD_1V6_XO | PI | Rail d’alimentation 1,6 V pour main oscillateur à cristaux | ||

| 10 | MAIN_XIN | IA | Entrée de l’oscillateur à cristaux principaux | ||

| 11 | WF_ANTSEL0 | FAIRE | Wi-Fi sélection d’antenne pour le commutateur DPDT externe | ||

| 12 | WF_ANTSEL1 | FAIRE | Wi-Fi sélection d’antenne pour le commutateur DPDT externe | ||

| 13 | GPIO0 | GPIO0/PWM0 | DIO | GPIO prenant en charge les interruptions multiplexé avec une sortie PWM | |

| 14 | GPIO1 | GPIO1/PWM1 | DIO | GPIO prenant en charge les interruptions multiplexé avec une sortie PWM | |

| 15 | GPIO2 | GPIO2/PWM2 | DIO | GPIO prenant en charge les interruptions multiplexé avec une sortie PWM | |

| 16 | GPIO3 | GPIO3/PWM3 | DIO | GPIO prenant en charge les interruptions multiplexé avec une sortie PWM | |

| 17 | GPIO4 | GPIO4/PWM4 | DIO | GPIO prenant en charge les interruptions multiplexé avec une sortie PWM | |

| 18 | GPIO5 | GPIO5/PWM5 | DIO | GPIO prenant en charge les interruptions multiplexé avec une sortie PWM | |

| 19 | GPIO6 | GPIO6/PWM6 | DIO | GPIO prenant en charge les interruptions multiplexé avec une sortie PWM | |

| 20 | GPIO7 | GPIO7/PWM7 | DIO | GPIO prenant en charge les interruptions multiplexé avec une sortie PWM | |

| 21 | GPIO8 | GPIO8/PWM8 | DIO | GPIO prenant en charge les interruptions multiplexé avec une sortie PWM | |

| 22 | GPIO9 | GPIO9/PWM9 | DIO | GPIO prenant en charge les interruptions multiplexé avec une sortie PWM | |

| 23 | DVDD_1V15 | PI | Rail d’alimentation 1.15V | ||

| 24 | DVDD_3V3 | PI | Rail d’alimentation 3.3V | ||

| 25 | GPIO10 | GPIO10/PWM10 | DIO | GPIO prenant en charge les interruptions multiplexé avec une sortie PWM | |

| 26 | GPIO11 | GPIO11/PWM11 | DIO | GPIO prenant en charge les interruptions multiplexé avec une sortie PWM | |

| 27 | GPIO12 | DIO | GPIO prenant en compte les interruptions | Les interruptions ne sont pas prises en charge actuellement | |

| 28 | GPIO13 | DIO | GPIO prenant en compte les interruptions | Les interruptions ne sont pas prises en charge actuellement | |

| 29 | GPIO14 | DIO | GPIO prenant en compte les interruptions | Les interruptions ne sont pas prises en charge actuellement | |

| 30 | GPIO15 | DIO | GPIO prenant en compte les interruptions | Les interruptions ne sont pas prises en charge actuellement | |

| 31 | GPIO16 | DIO | GPIO prenant en compte les interruptions | Les interruptions ne sont pas prises en charge actuellement | |

| 32 | GPIO17 | DIO | GPIO prenant en compte les interruptions | Les interruptions ne sont pas prises en charge actuellement | |

| 33 | GPIO18 | DIO | GPIO prenant en compte les interruptions | Les interruptions ne sont pas prises en charge actuellement | |

| 34 | GPIO19 | DIO | GPIO prenant en compte les interruptions | Les interruptions ne sont pas prises en charge actuellement | |

| 35 | GPIO20 | DIO | GPIO prenant en compte les interruptions | Les interruptions ne sont pas prises en charge actuellement | |

| 36 | GPIO21 | DIO | GPIO prenant en compte les interruptions | Les interruptions ne sont pas prises en charge actuellement | |

| 37 | GPIO22 | DIO | GPIO prenant en compte les interruptions | Les interruptions ne sont pas prises en charge actuellement | |

| 38 | GPIO23 | DIO | GPIO prenant en compte les interruptions | Les interruptions ne sont pas prises en charge actuellement | |

| 39 | GPIO26 | GPIO26/ SCLK0/TXD0 | DIO | GPIO multiplexé avec les fonctions ISU 0 | |

| 40 | GPIO27 | GPIO27/ MOSI0/RTS0/SCL0 | DIO | GPIO multiplexé avec les fonctions ISU 0 | |

| 41 | GND | P | Sol | ||

| 42 | GPIO28 | GPIO28/ MISO0/RXD0/SDA0 | DIO | GPIO multiplexé avec les fonctions ISU 0 | |

| 43 | GPIO29 | GPIO29/CSA0/CTS0 | DIO | GPIO multiplexé avec les fonctions ISU 0 | |

| 44 | DVDD_1V15 | PI | Rail d’alimentation 1.15V | ||

| 45 | GPIO30 | GPIO30/CSB0 | DIO | GPIO multiplexé avec les fonctions ISU 0 | |

| 46 | GPIO31 | GPIO31/ SCLK1/TXD1 | DIO | GPIO multiplexé avec les fonctions ISU 1 | |

| 47 | GPIO32 | GPIO32/ MOSI1/RTS1/SCL1 | DIO | GPIO multiplexé avec les fonctions ISU 1 | |

| 48 | GPIO33 | GPIO33/ MISO1/RXD1/SDA1 | DIO | GPIO multiplexé avec les fonctions ISU 1 | |

| 49 | GPIO34 | GPIO34/CSA1/CTS1 | DIO | GPIO multiplexé avec les fonctions ISU 1 | |

| 50 | GPIO35 | GPIO35/CSB1 | DIO | GPIO multiplexé avec les fonctions ISU 1 | |

| 51 | GPIO36 | GPIO36/ SCLK2/TXD2 | DIO | GPIO multiplexé avec les fonctions ISU 2 | |

| 52 | GPIO37 | GPIO37/ MOSI2/RTS2/SCL2 | DIO | GPIO multiplexé avec les fonctions ISU 2 | |

| 53 | GPIO38 | GPIO38/ MISO2/RXD2/SDA2 | DIO | GPIO multiplexé avec les fonctions ISU 2 | |

| 54 | GPIO39 | GPIO39/CSA2/CTS2 | DIO | GPIO multiplexé avec les fonctions ISU 2 | |

| 55 | GPIO40 | GPIO40/CSB2 | DIO | GPIO multiplexé avec les fonctions ISU 2 | |

| 56 | DVDD_3V3 | PI | Rail d’alimentation 3.3V | ||

| 57 | DVDD_1V15 | PI | Rail d’alimentation 1.15V | ||

| 58 | GPIO41 | GPIO41/ADC0 | DIO | GPIO multiplexé avec entrée ADC | |

| 59 | GPIO42 | GPIO42/ADC1 | DIO | GPIO multiplexé avec entrée ADC | |

| 60 | GPIO43 | GPIO43/ADC2 | DIO | GPIO multiplexé avec entrée ADC | |

| 61 | GPIO44 | GPIO44/ADC3 | DIO | GPIO multiplexé avec entrée ADC | |

| 62 | GPIO45 | GPIO45/ADC4 | DIO | GPIO multiplexé avec entrée ADC | |

| 63 | GPIO46 | GPIO46/ADC5 | DIO | GPIO multiplexé avec entrée ADC | |

| 64 | GPIO47 | GPIO47/ADC6 | DIO | GPIO multiplexé avec entrée ADC | |

| 65 | GPIO48 | GPIO48/ADC7 | DIO | GPIO multiplexé avec entrée ADC | |

| 66 | AVDD_2V5_ADC | PI | Rail d’alimentation 2,5 V pour ADC | ||

| 67 | VREF_ADC | IA | Tension de référence pour ADC | ||

| 68 | AVSS_2V5_ADC | P | Terrain pour ADC | ||

| 69 | EXT_PMU_EN | FAIRE | Sortie d’activation de l’alimentation externe | ||

| 70 | RÉVEIL | DI | Sortie de veille externe du mode de veille le plus profond | Non pris en charge actuellement | |

| 71 | AVDD_3V3_RTC | PI | Rail d’alimentation 3,3 V pour horloge en temps réel | ||

| 72 | RTC_XIN | IA | Entrée de l’oscillateur en cristal d’horloge en temps réel | ||

| 73 | RTC_XOUT | AO | Sortie de l’oscillateur en cristal d’horloge en temps réel | ||

| 74 | AVDD_3V3_XPPLL | PI | Rail d’alimentation 3.3V pour boucle interne à verrouillage de phase | ||

| 75 | I2S_MCLK0_ALT | AO | Alternative analogique à MCLK0 | I2S est actuellement pris en charge pour les applications M4 uniquement. | |

| 76 | I2S_MCLK1_ALT | AO | Alternative analogique à MCLK1 | I2S est actuellement pris en charge pour les applications M4 uniquement. | |

| 77 | DVDD_1V15 | PI | Rail d’alimentation 1.15V | ||

| 78 | DVDD_1V15 | PI | Rail d’alimentation 1.15V | ||

| 79 | VOUT_2V5 | Bon de commande | Sortie de LDO interne 2.5V | ||

| 80 | AVDD_3V3 | PI | Rail d’alimentation 3.3V | ||

| 81 | PMU_EN | DI | Remplacement de PMU interne | ||

| 82 | RÉSERVÉS AU | ||||

| 83 | GND | P | Sol | ||

| 84 | SENSE_1V15 | IA | Entrée de sens pour stabiliser l’alimentation 1.15V | ||

| 85 | VOUT_1V15 | Bon de commande | Sortie de LDO interne 1.15V | ||

| 86 | AVDD_1V6_CLDO | PI | Rail d’alimentation 1.6V pour le LDO interne 1.15V core | ||

| 87 | PMU_CAP | Un | Connecter un condensateur entre cette broche et AVDD_3V3_BUCK pour maintenir la stabilité pmu | ||

| 88 | AVDD_3V3_BUCK | PI | Rail d’alimentation 3.3V pour convertisseur DC-DC 1.6V buck interne | ||

| 89 | AVDD_3V3_BUCK | PI | Rail d’alimentation 3.3V pour convertisseur DC-DC 1.6V buck interne | ||

| 90 | VOUT_1V6 | Bon de commande | Sortie du convertisseur buck 1.6V interne | ||

| 91 | VOUT_1V6 | Bon de commande | Sortie du convertisseur buck 1.6V interne | ||

| 92 | AVSS_3V3_BUCK | P | Terre pour le convertisseur buck interne 1.6V | ||

| 93 | AVSS_3V3_BUCK | P | Terre pour le convertisseur buck interne 1.6V | ||

| 94 | DEBUG_RXD | DI | Réservé au débogage Azure Sphere | ||

| 95 | DEBUG_TXD | FAIRE | Réservé au débogage Azure Sphere | ||

| 96 | DEBUG_RTS | FAIRE | Réservé au débogage Azure Sphere | ||

| 97 | DEBUG_CTS | DI | Réservé au débogage Azure Sphere | ||

| 98 | SWD_DIO | DIO | ARM SWD pour le débogage Cortex-M4F | ||

| 99 | SWD_CLK | DI | ARM SWD pour le débogage Cortex-M4F | ||

| 100 | SWO | FAIRE | ARM SWO pour le débogage Cortex-M4F | Non pris en charge actuellement | |

| 101 | GPIO56 | GPIO56/TX0 | DIO | GPIO multiplexé avec I2S 0 | I2S est actuellement pris en charge pour les applications M4 uniquement. |

| 102 | GPIO57 | GPIO57 /MCLK0 | DIO | GPIO multiplexé avec I2S 0 | I2S est actuellement pris en charge pour les applications M4 uniquement. |

| 103 | GPIO58 | GPIO58/FS0 | DIO | GPIO multiplexé avec I2S 0 | I2S est actuellement pris en charge pour les applications M4 uniquement. |

| 104 | GPIO59 | GPIO59/RX0 | DIO | GPIO multiplexé avec I2S 0 | I2S est actuellement pris en charge pour les applications M4 uniquement. |

| 105 | GPIO60 | GPIO60/ BCLK0 | DIO | GPIO multiplexé avec I2S 0 | I2S est actuellement pris en charge pour les applications M4 uniquement. |

| 106 | DVDD_1V15 | PI | Rail d’alimentation 1.15V | ||

| 107 | DVDD_3V3 | PI | Rail d’alimentation 3.3V | ||

| 108 | GPIO61 | GPIO61/TX1 | DIO | GPIO multiplexé avec I2S 1 | I2S est actuellement pris en charge pour les applications M4 uniquement. |

| 109 | GPIO62 | GPIO62/ MCLK1 | DIO | GPIO multiplexé avec I2S 1 | I2S est actuellement pris en charge pour les applications M4 uniquement. |

| 110 | GPIO63 | GPIO63/FS1 | DIO | GPIO multiplexé avec I2S 1 | I2S est actuellement pris en charge pour les applications M4 uniquement. |

| 111 | GPIO64 | GPIO64/RX1 | DIO | GPIO multiplexé avec I2S 1 | I2S est actuellement pris en charge pour les applications M4 uniquement. |

| 112 | GPIO65 | GPIO65/ BCLK1 | DIO | GPIO multiplexé avec I2S 1 | I2S est actuellement pris en charge pour les applications M4 uniquement. |

| 113 | GPIO66 | GPIO66/ SCLK3/TXD3 | DIO | GPIO multiplexé avec les fonctions ISU 3 | |

| 114 | GPIO67 | GPIO67/ MOSI3/RTS3/SCL3 | DIO | GPIO multiplexé avec les fonctions ISU 3 | |

| 115 | GPIO68 | GPIO68/ MISO3/RXD3/SDA3 | DIO | GPIO multiplexé avec les fonctions ISU 3 | |

| 116 | GPIO69 | GPIO69/CSA3/CTS3 | DIO | GPIO multiplexé avec les fonctions ISU 3 | |

| 117 | GPIO70 | GPIO70/CSB3 | DIO | GPIO multiplexé avec les fonctions ISU 3 | Prend actuellement en charge GPIO uniquement |

| 118 | DVDD_3V3 | PI | Rail d’alimentation 3.3V | ||

| 119 | GPIO71 | GPIO71/ SCLK4/TXD4 | DIO | GPIO multiplexé avec les fonctions ISU 4 | |

| 120 | GPIO72 | GPIO72/ MOSI4/RTS4/SCL4 | DIO | GPIO multiplexé avec les fonctions ISU 4 | |

| 121 | DVDD_1V15 | PI | Rail d’alimentation 1.15V | ||

| 122 | GPIO73 | GPIO73/ MISO4/RXD4/SDA4 | DIO | GPIO multiplexé avec les fonctions ISU 4 | |

| 123 | GPIO74 | GPIO74/CSA4/CTS4 | DIO | GPIO multiplexé avec les fonctions ISU 4 | |

| 124 | GPIO75 | GPIO75/CSB4 | DIO | GPIO multiplexé avec les fonctions ISU 4 | |

| 125 | SYSRST_N | DI | Réinitialisation du système, faible actif | ||

| 126 | DVDD_1V15 | PI | Rail d’alimentation 1.15V | ||

| 127 | SERVICE_TXD | FAIRE | Port de service Azure Sphere | Non disponible pour l’utilisation de l’application cliente | |

| 128 | SERVICE_RTS | FAIRE | Port de service Azure Sphere | Non disponible pour l’utilisation de l’application cliente | |

| 129 | SERVICE_RXD | DI | Port de service Azure Sphere | Non disponible pour l’utilisation de l’application cliente | |

| 130 | SERVICE_CTS | DI | Port de service Azure Sphere | Non disponible pour l’utilisation de l’application cliente | |

| 131 | RÉSERVÉS AU | ||||

| 132 | DVDD_1V15 | PI | Rail d’alimentation 1.15V | ||

| 133 | DVDD_3V3 | PI | Rail d’alimentation 3.3V | ||

| 134 | RECOVERY_RXD | DI | Port de récupération Azure Sphere | Non disponible pour l’utilisation de l’application cliente | |

| 135 | RECOVERY_TXD | FAIRE | Port de récupération Azure Sphere | Non disponible pour l’utilisation de l’application cliente | |

| 136 | RECOVERY_RTS | FAIRE | Port de récupération Azure Sphere | Non disponible pour l’utilisation de l’application cliente | |

| 137 | RECOVERY_CTS | DI | Port de récupération Azure Sphere | Non disponible pour l’utilisation de l’application cliente | |

| 138 | IO0_GPIO85 | IO0_GPIO85/ IO0_RXD | DI | GPIO dédié multiplexé avec UART pour E/S M4 0 | |

| 139 | IO0_GPIO86 | IO0_GPIO86/ IO0_TXD | FAIRE | GPIO dédié multiplexé avec UART pour E/S M4 0 | |

| 140 | IO0_GPIO87 | IO0_GPIO87/ IO0_RTS | FAIRE | GPIO dédié multiplexé avec UART pour E/S M4 0 | |

| 141 | IO0_GPIO88 | IO0_GPIO88/ IO0_CTS | DI | GPIO dédié multiplexé avec UART pour E/S M4 0 | |

| 142 | IO1_GPIO89 | IO1_GPIO89/ IO1_RXD | DI | GPIO dédié multiplexé avec UART pour E/S M4 1 | |

| 143 | IO1_GPIO90 | IO1_GPIO90/ IO1_TXD | FAIRE | GPIO dédié multiplexé avec UART pour E/S M4 1 | |

| 144 | DVDD_3V3 | PI | Rail d’alimentation 3.3V | ||

| 145 | IO1_GPIO91 | IO1_GPIO91/ IO1_RTS | FAIRE | GPIO dédié multiplexé avec UART pour E/S M4 1 | |

| 146 | IO1_GPIO92 | IO1_GPIO92/ IO1_CTS | DI | GPIO dédié multiplexé avec UART pour E/S M4 1 | |

| 147 | RÉSERVÉS AU | ||||

| 148 | TEST | DI | Doit être tiré bas pour un fonctionnement normal | ||

| 149 | WF_G_RF_AUXIN | RF | Port de diversité de réception de Wi-Fi 2,4 GHz | ||

| 150 | NC | ||||

| 151 | AVDD_3V3_WF_G_PA | PI | Rail d’alimentation 3,3 V pour amplificateur de puissance Wi-Fi 2,4 GHz | ||

| 152 | NC | ||||

| 153 | WF_G_RF_ION | RF | Port d’antenne Wi-Fi 2,4 GHz (différentiel) | ||

| 154 | WF_G_RF_ION | RF | Port d’antenne Wi-Fi 2,4 GHz (différentiel) | ||

| 155 | WF_G_RF_IOP | RF | Port d’antenne Wi-Fi 2,4 GHz (différentiel) | ||

| 156 | WF_G_RF_IOP | RF | Port d’antenne Wi-Fi 2,4 GHz (différentiel) | ||

| 157 | NC | ||||

| 158 | AVDD_3V3_WF_G_TX | PI | Rail d’alimentation 3,3 V pour 2,4 GHz Wi-Fi transmission de puissance | ||

| 159 | WF_A_RF_AUXIN | RF | 5 GHz Wi-Fi recevoir le port de diversité | ||

| 160 | AVDD_3V3_WF_A_TX | PI | Rail d’alimentation 3,3 V pour transmission de puissance Wi-Fi 5 GHz | ||

| 161 | NC | ||||

| 162 | WF_A_RFIO | RF | Port d’antenne Wi-Fi 5 GHz (déséquilibré) | ||

| 163 | WF_A_RFIO | RF | Port d’antenne Wi-Fi 5 GHz (déséquilibré) | ||

| 164 | GND | P | Sol | ||

| 165 | EPAD | P | Sol |