Nota

L'accesso a questa pagina richiede l'autorizzazione. È possibile provare ad accedere o modificare le directory.

L'accesso a questa pagina richiede l'autorizzazione. È possibile provare a modificare le directory.

Di Mark Russinovich

Pubblicato: 16 dicembre 2025

Coreinfo(3 MB)

Coreinfo(3 MB)

Introduzione

Coreinfo è un'utilità che mostra il mapping tra i processori logici e il processore fisico, il nodo NUMA e il socket in cui risiedono, nonché le cache assegnate a ciascun processore logico. Usa API Windows di basso livello (modalità utente e modalità kernel) per recuperare informazioni dettagliate sulla topologia della CPU direttamente dal sistema operativo. La versione della riga di comando restituisce la rappresentazione del mapping a un processore logico con un asterisco, ad esempio '*'. L'interfaccia utente offre più visualizzazioni specializzate per esplorare diversi aspetti della topologia CPU del sistema, inclusi core logici e fisici, nodi NUMA, socket, gerarchie di cache e metriche delle prestazioni in tempo reale. Coreinfo è utile per ottenere informazioni dettagliate sul processore e la topologia della cache del sistema.

Installazione

Estrarre l'archivio in una directory e quindi eseguire Coreinfo digitando da tale directory Coreinfo / Coreinfo64 o Coreinfo64a, a seconda dell'architettura. Avvia CoreInfoEx / CoreInfoEx64 / CoreInfoEx64a per la versione dell'interfaccia utente.

Nota: Alcune funzionalità possono richiedere privilegi amministrativi per il recupero completo delle informazioni.

Panoramica dell'interfaccia utente

L'interfaccia utente coreinfo è costituita da diversi componenti chiave:

Layout finestra principale

- Pannello superiore: visualizza le informazioni di sistema, tra cui il nome della CPU, l'architettura e i conteggi dei core

- Riquadro di spostamento (a sinistra): consente di accedere rapidamente a visualizzazioni diverse

- Area contenuto (Centro): mostra i dati e le visualizzazioni della visualizzazione selezionata

- Riquadro dettagli (in basso): visualizza informazioni dettagliate quando vengono selezionati core o celle

- Impostazioni: Opzioni di accesso e preferenze dell'applicazione

che mostra il layout completo dell'interfaccia utente, la modalità scura

che mostra il layout completo dell'interfaccia utente, la modalità scura

Viste di navigazione

Il riquadro di spostamento a sinistra consente di accedere a sei visualizzazioni specializzate:

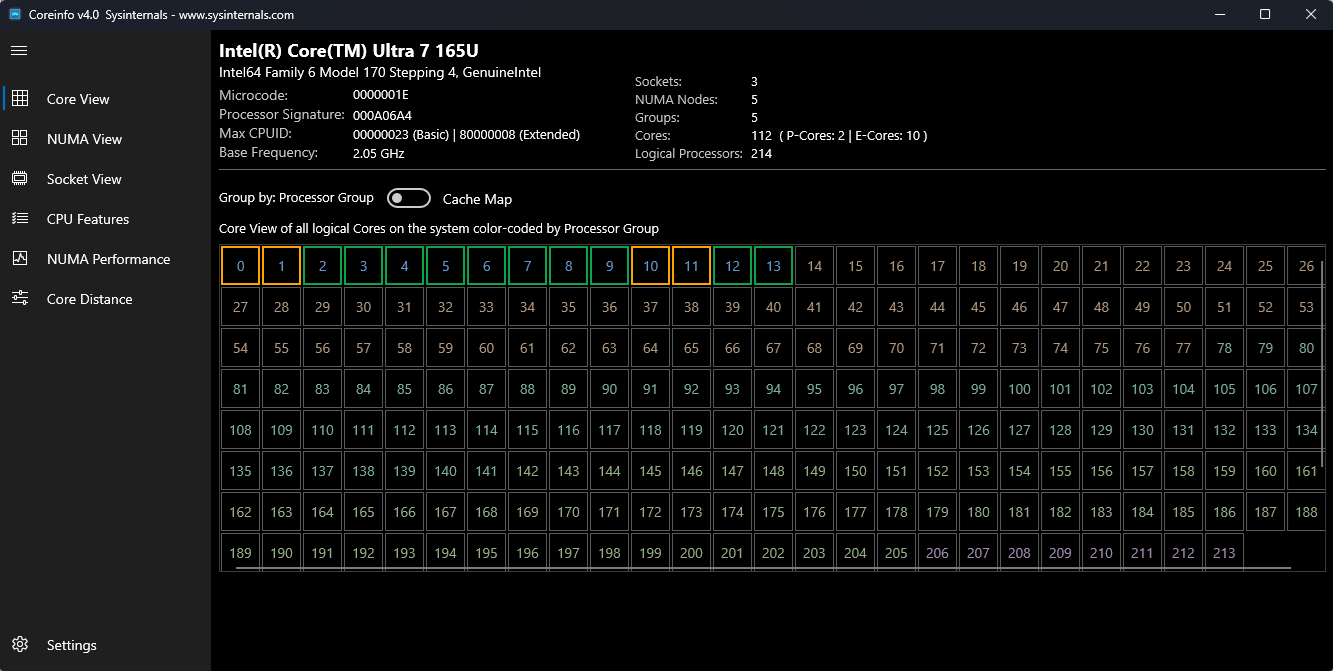

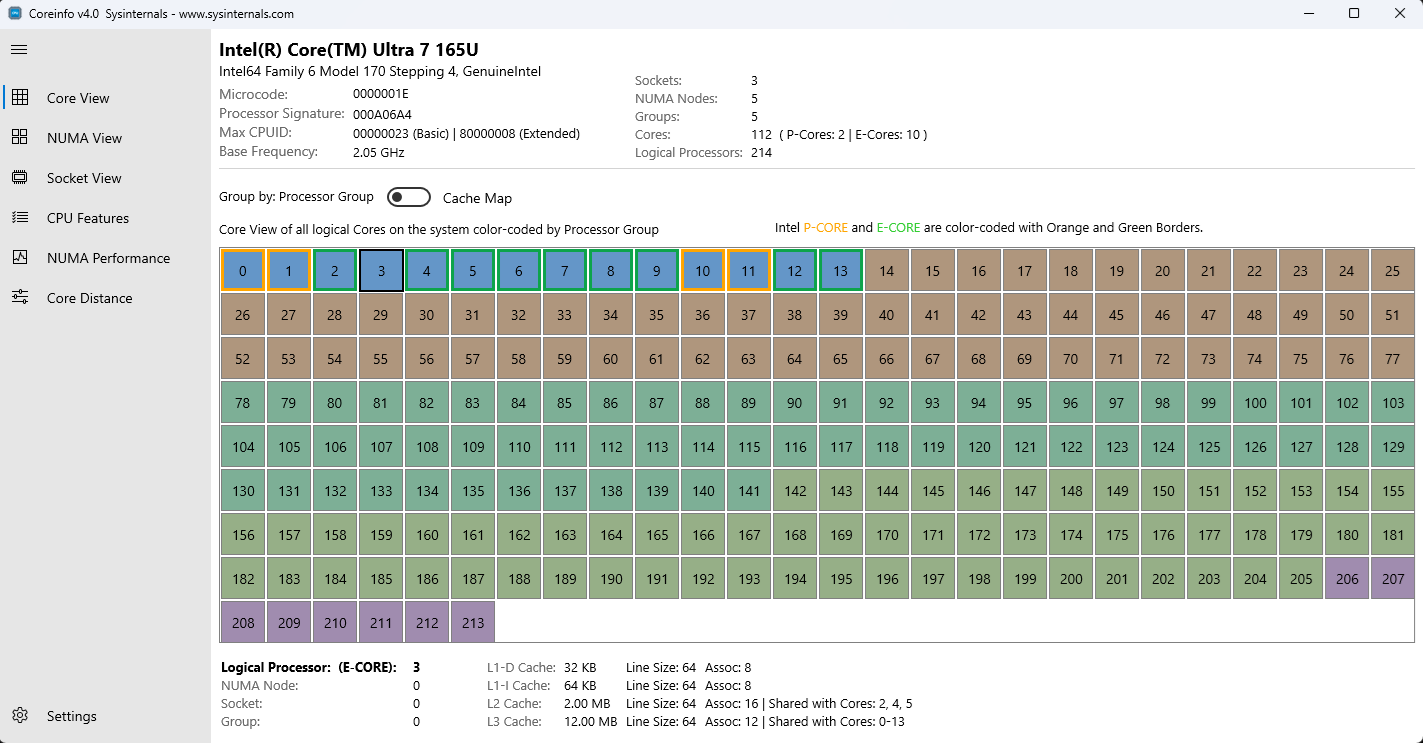

1. Visualizzazione principale

La visualizzazione Core visualizza tutti i processori logici nel sistema in un layout griglia, che mostra la relazione tra core logici e le relative risorse fisiche.

Funzionalità:

- Layout a griglia: ogni cella rappresenta un processore logico

-

Indicatori di tipo core:

- P-Core (core delle prestazioni) - colorati in modo distinto

- E-Core (core di efficienza) - colorati in modo diverso

- Core standard : colorazione predefinita

- Interruttore di mappatura cache: passare dalla visualizzazione predefinita alla visualizzazione della gerarchia della cache

- Selezione interattiva: fare clic su qualsiasi core per visualizzare informazioni dettagliate nel riquadro inferiore

Informazioni visualizzate:

- Numero processore logico

- Tipo core (P-Core/E-Core, se applicabile)

- Livelli di cache associati (L1, L2, L3)

- Assegnazione di nodo NUMA

- Assegnazione socket

- Assegnazione gruppo

Core View che mostra i processori logici nella disposizione a griglia

Core View che mostra i processori logici nella disposizione a griglia

Informazioni Riquadro dei Dettagli (quando è selezionato un core):

- Maschera di processore e affinità del processore

- Gerarchia della cache (cache dei dati, cache delle istruzioni, cache unificata)

- Dimensioni della cache e associatività

- Dimensioni della riga della cache

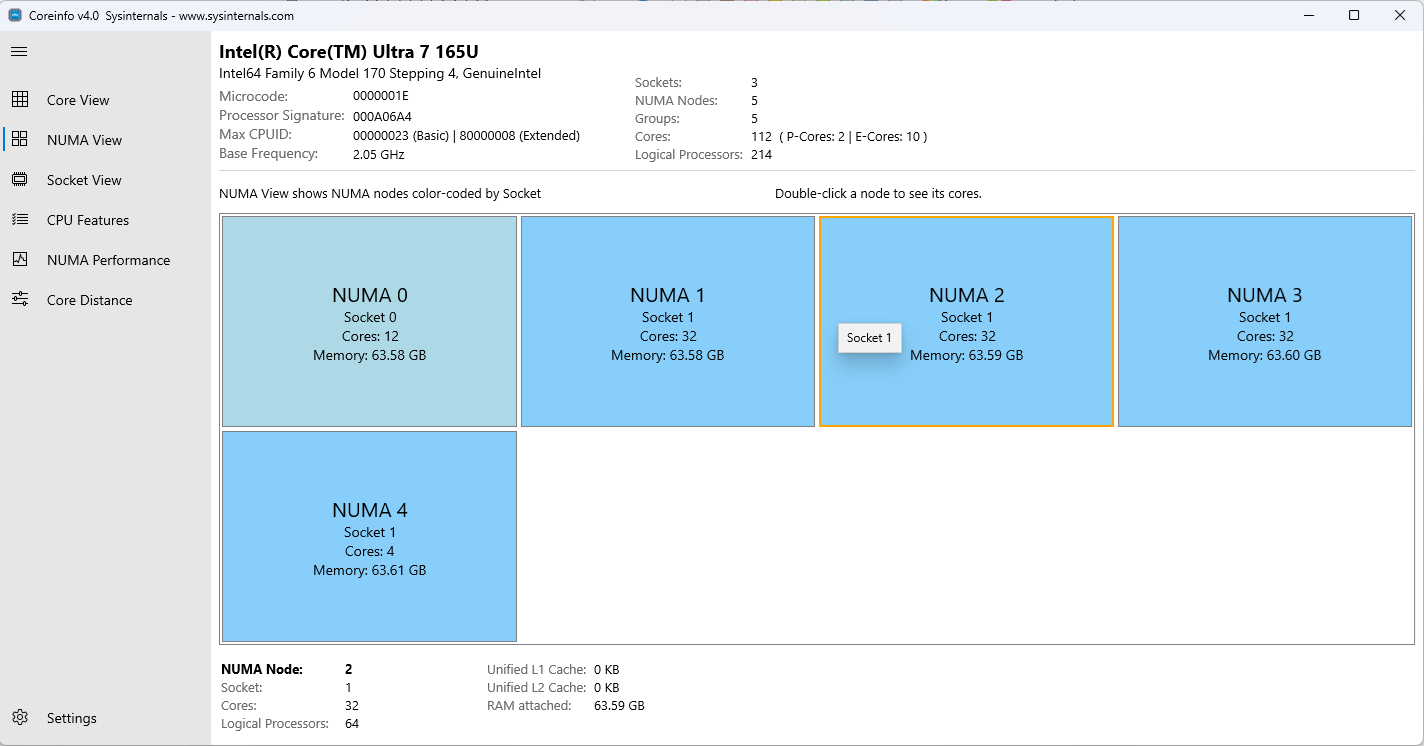

2. Visualizzazione NUMA

La visualizzazione NUMA (Non-Uniform Memory Access) organizza i core in base alle assegnazioni di nodi NUMA, semplificando la comprensione della località della memoria e dei modelli di accesso.

Funzionalità:

- Organizzazione basata su nodi: core raggruppati per nodo NUMA

- Core fisici e logici: mostra entrambi i conteggi per ogni nodo

- Informazioni sulla memoria: visualizza la memoria disponibile per ogni nodo NUMA

-

Spostamento interattivo:

- Fare clic su un nodo NUMA per visualizzarne i dettagli nel riquadro dei dettagli inferiore

- Fare doppio clic su un nodo NUMA per passare alla visualizzazione principale che mostra tutti i core del nodo NUMA selezionato

- Visualizzazione gerarchica: mostra la relazione tra nodi NUMA e core

Informazioni visualizzate:

- Numero di nodi NUMA

- Core per nodo NUMA (fisici e logici)

- Capacità di memoria per nodo

- Distribuzione principale tra nodi

- Numero di core di efficienza (se applicabile)

NUMA Visualizzazione NUMA che mostra i core organizzati dai nodi NUMA

NUMA Visualizzazione NUMA che mostra i core organizzati dai nodi NUMA

Casi d'uso:

- Ottimizzazione dei modelli di accesso alla memoria

- Informazioni sulle prestazioni dell'applicazione compatibile con NUMA

- Pianificazione del posizionamento di thread/processi per ottenere prestazioni ottimali

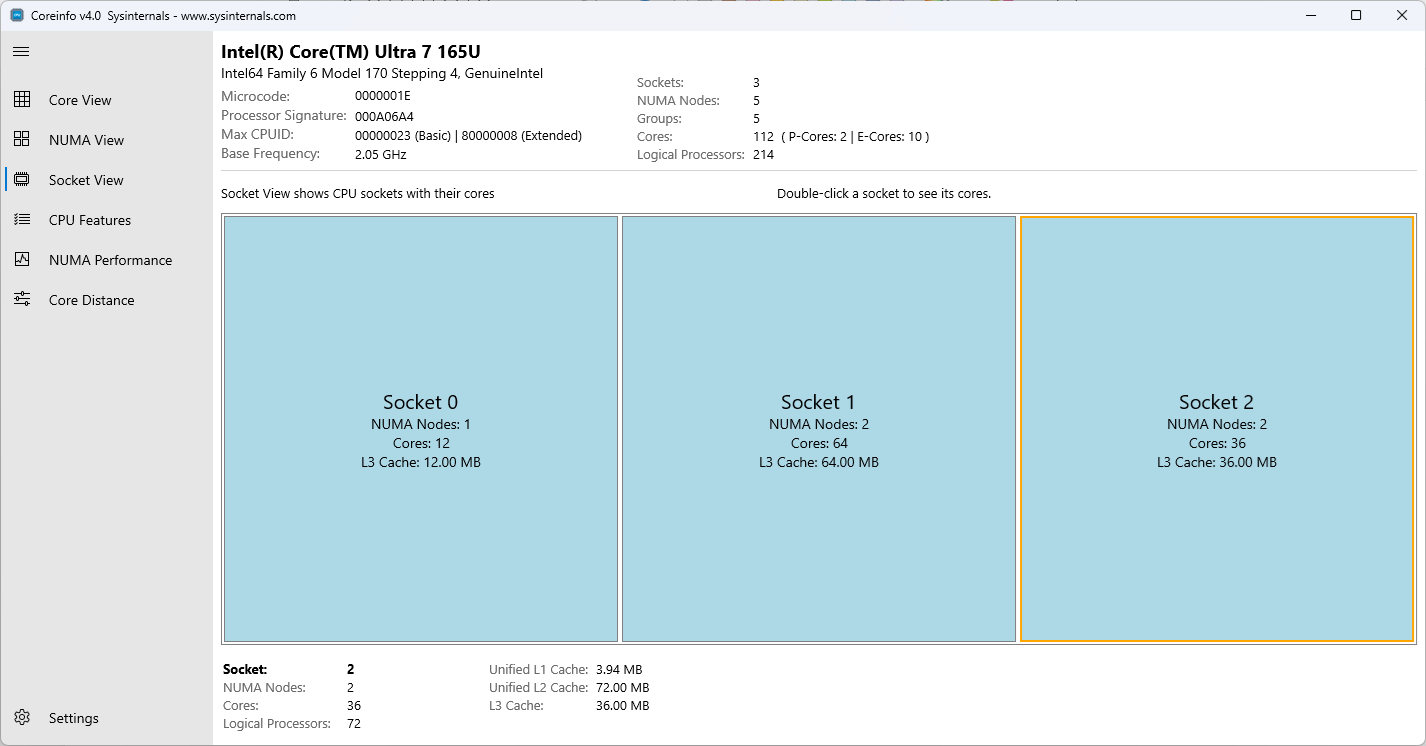

3. Visualizzazione socket

La visualizzazione Socket visualizza i core organizzati in base al socket CPU fisico, utile per comprendere i sistemi multi socket e la distribuzione delle risorse a livello di socket.

Funzionalità:

- Raggruppamento basato su socket: i core organizzati in base al socket fisico

- Informazioni sul socket: numero di socket e distribuzione core

-

Spostamento interattivo:

- Fare clic su un socket per visualizzarne i dettagli nel riquadro dei dettagli inferiore

- Fare doppio clic su un socket per passare alla Visualizzazione core che mostra tutti i core da quel socket selezionato

- Condivisione cache: visualizzare i core che condividono cache a livello di socket

Informazioni visualizzate:

- Numero di socket fisici

- Core per socket (fisici e logici)

- Informazioni sulla cache a livello di socket

- Nodi NUMA per socket

Socket View (Visualizzazione socket socket) che mostra i core organizzati in base ai socket CPU

Socket View (Visualizzazione socket socket) che mostra i core organizzati in base ai socket CPU

Casi d'uso:

- Analisi di sistema multi-socket

- Informazioni sui costi di comunicazione tra socket

- Pianificazione della distribuzione del carico di lavoro nei server multi socket

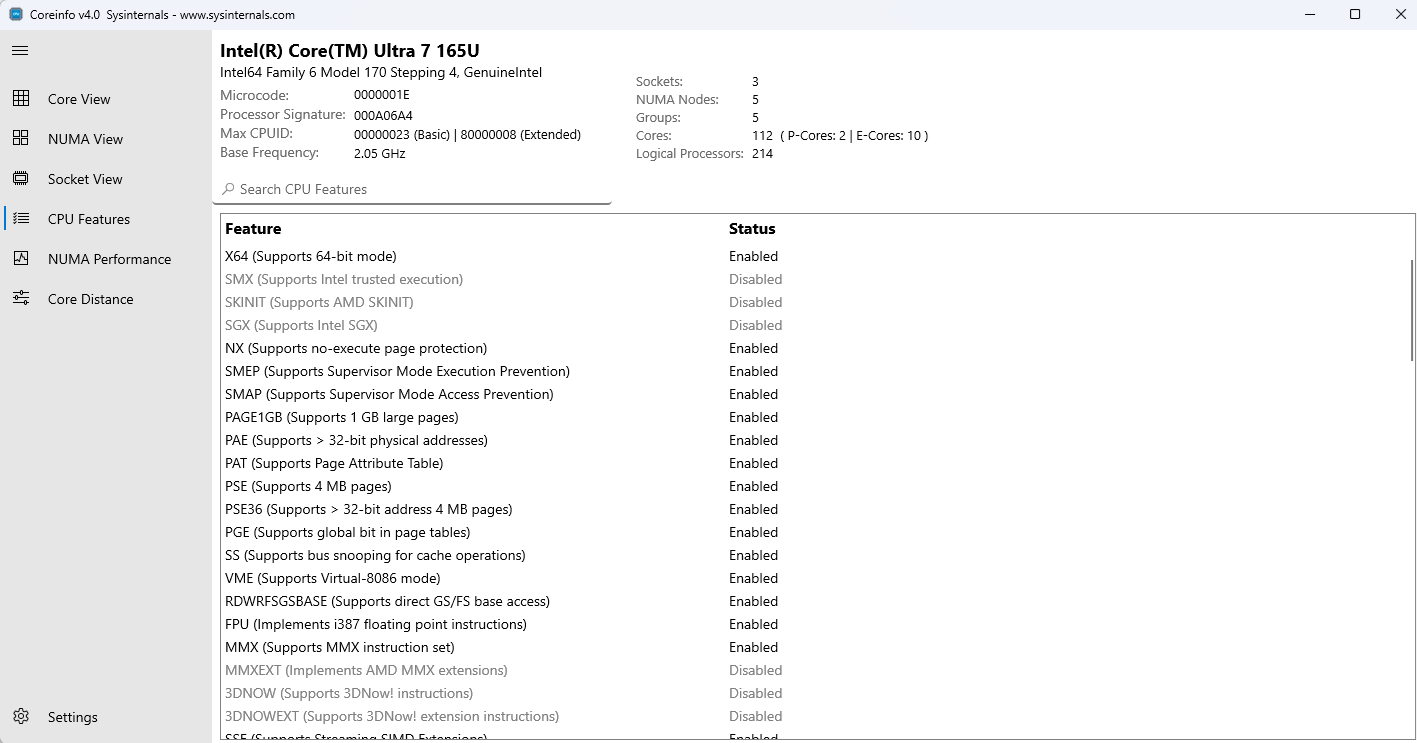

4. Visualizzazione funzionalità CPU

La visualizzazione Funzionalità CPU visualizza un elenco completo di funzionalità del processore, estensioni del set di istruzioni e funzionalità hardware supportate dalla CPU.

Funzionalità:

- Elenco ricercabile: trovare rapidamente funzionalità della CPU specifiche usando la barra di ricerca

-

Indicatori di stato: chiaro l'indicazione visiva delle funzionalità supportate/non supportate tramite codifica a colori

- Le funzionalità supportate vengono visualizzate a colori normali

- Le funzionalità non supportate/disabilitate sono disattivate

-

Categorie di funzionalità:

- Virtualizzazione (VMX, SVM, HYPERVISOR)

- Supporto per 64 bit (EM64T, NX)

- Set di istruzioni (SSE, AVX, AES e così via)

- Risparmio energia (EIST, ACPI, Thermal)

- Funzionalità di sicurezza (SMX, SKINIT)

- Funzionalità di memoria (PAE, PAT, PSE)

- Funzionalità di debug e monitoraggio

Informazioni visualizzate:

- Abbreviazione delle funzionalità

- Stato della funzionalità (supportato/non supportato)

- Descrizione completa della funzionalità (nel riquadro dei dettagli)

Visualizzazione delle caratteristiche del processore

Visualizzazione delle caratteristiche del processore

Nota: Alcune funzionalità di virtualizzazione( ad esempio VMX, SVM) possono essere segnalate in modo non corretto come non disponibili durante l'esecuzione con un hypervisor attivo o quando vengono eseguite dall'interno di una macchina virtuale. Coreinfo deve essere eseguito in un sistema senza un hypervisor in esecuzione per ottenere risultati accurati.

Casi d'uso:

- Verifica della disponibilità del set di istruzioni prima della distribuzione delle applicazioni

- Controllo del supporto per la virtualizzazione

- Informazioni sulla generazione e sulle funzionalità del processore

- Debug dei problemi di prestazioni relativi alle funzionalità della CPU mancanti

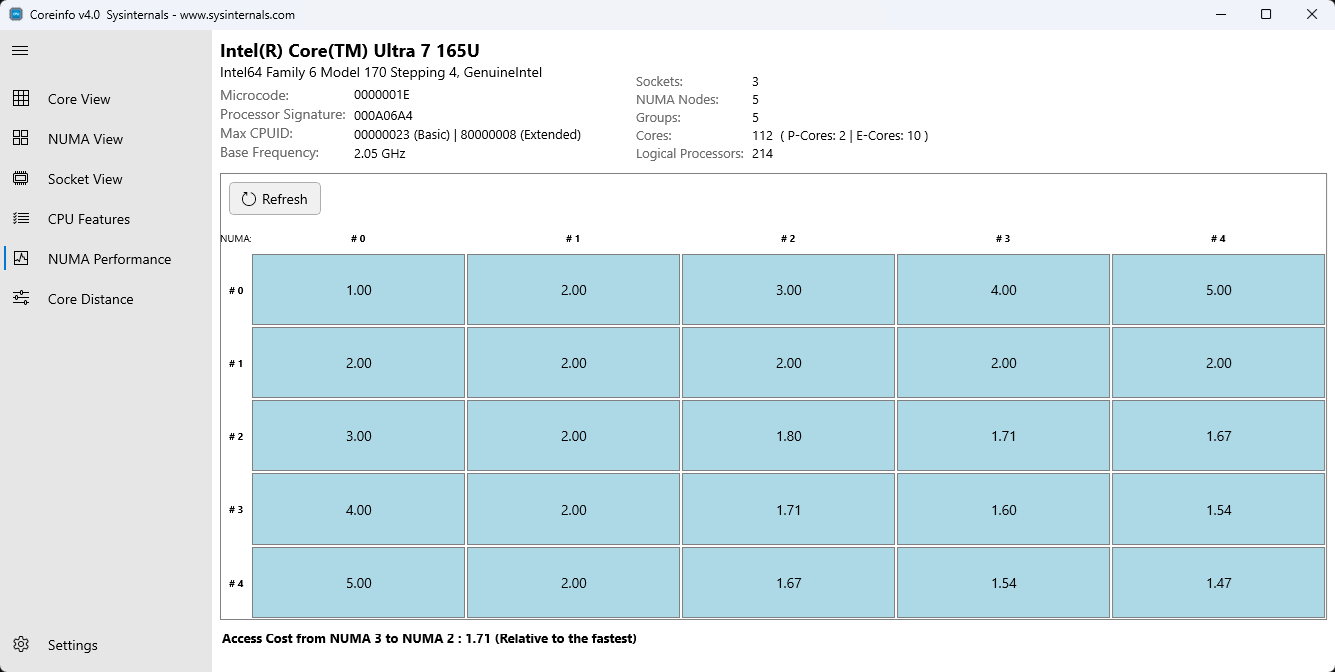

5. Visualizzazione prestazioni NUMA

La Visualizzazione delle Prestazioni NUMA offre una rappresentazione a griglia che mostra i costi di accesso alla memoria tra i nodi NUMA, aiutando a identificare i colli di bottiglia delle prestazioni nei sistemi NUMA.

Funzionalità:

- Visualizzazione griglia: matrice che visualizza i costi di accesso alla memoria relativi tra i nodi NUMA

- Matrice interattiva: passare il puntatore del mouse sulle celle per visualizzare informazioni dettagliate sulle prestazioni

- Aggiornamenti in tempo reale: aggiornamenti dei dati sulle prestazioni in modo dinamico selezionando il pulsante Aggiorna

- Visualizzazione dei costi relativi: mostra il costo relativo dell'accesso alla memoria da nodi NUMA diversi

Informazioni visualizzate:

- Matrice NxN in cui N = numero di nodi NUMA

- Costo dell'accesso alla memoria dal nodo NUMA di origine (riga) al nodo NUMA di destinazione (colonna)

- Valori numerici che mostrano i costi relativi delle prestazioni

- Le celle diagonali mostrano l'accesso alla memoria locale (in genere il costo più basso)

Griglia NUMA che mostra i costi di accesso alla memoria

Griglia NUMA che mostra i costi di accesso alla memoria

Informazioni sulla griglia:

- Elementi diagonali: rappresentare l'accesso alla memoria locale (nodo che accede alla propria memoria) - in genere i valori più bassi

- Elementi fuori diagonale: rappresentano l'accesso remoto alla memoria con costi relativi più elevati

- Simmetria: la matrice potrebbe non essere perfettamente simmetrica perché i costi di accesso possono variare in base alla direzione

Casi d'uso:

- Identificazione dei colli di bottiglia delle prestazioni legati a NUMA

- Ottimizzazione delle strategie di allocazione della memoria

- Pianificazione dell'aggiunta di processi/thread per i sistemi NUMA

- Informazioni sulle sanzioni per l'accesso alla memoria tra nodi

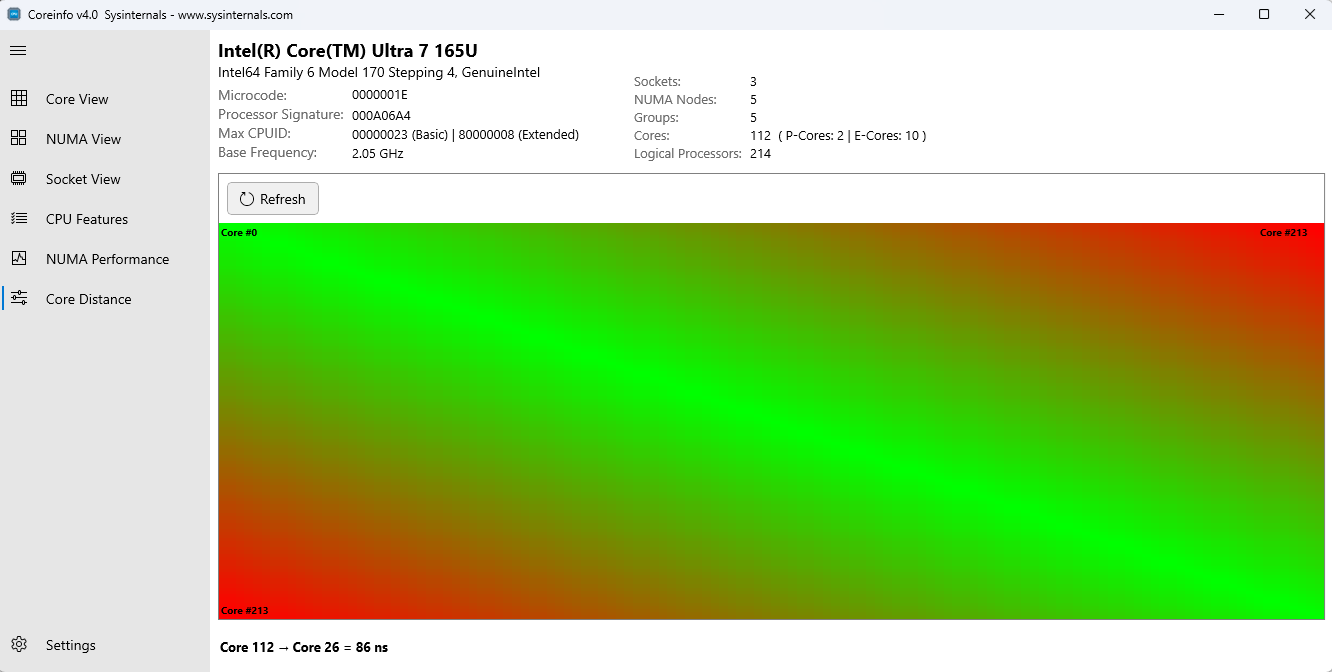

6. Visualizzazione distanza principale

La visualizzazione della distanza centrale mostra una mappa termica dettagliata dei costi di comunicazione tra singoli core della CPU, fornendo informazioni sulla latenza core-to-core e sull'efficienza della comunicazione.

Funzionalità:

-

Mappa termica a livello di core: matrice codificata a colori che mostra le distanze relative tra i core

- Verde/Blu = Bassa latenza (stesso cluster core, cache condivisa)

- Giallo/Arancione = Latenza media (stesso socket, cluster diverso)

- Rosso = Latenza elevata (diverso socket, nodo NUMA)

- Esplorazione interattiva: passare il puntatore sul canvas della griglia per visualizzare informazioni dettagliate sulla distanza

- Analisi granulare: mostra le relazioni core-to-core con la granularità migliore

- Aggiornamento dinamico: usare il pulsante Aggiorna per ottenere in modo dinamico i dati sulla distanza principale aggiornati

Informazioni visualizzate:

- Matrice NxN in cui N = numero di processori logici

- Distanza relativa/latenza dal core di origine (riga) al core di destinazione (colonna)

- Codifica dei colori per la rapida identificazione visiva delle relazioni principali

- Metriche di distanza dettagliate nel riquadro dei dettagli

Mappa termica che mostra i costi di comunicazione da core a core

Mappa termica che mostra i costi di comunicazione da core a core

Informazioni sulla mappa delle distanze:

- Elementi diagonali: sempre zero (core a se stesso)

- Distanza bassa (verde): I core condividono la cache L2 o L3

- Distanza media (gialla): core nello stesso socket ma domini di cache diversi

- Distanza elevata (rosso): core su socket o nodi NUMA diversi

Casi d'uso:

- Ottimizzazione dell'affinità di thread

- Comprendere i domini di coesione della cache

- Identificazione di coppie di core ottimali per la comunicazione dei thread

- Analisi delle prestazioni dell'applicazione multithread

- Pianificazione delle strategie di aggiunta della CPU per applicazioni a bassa latenza

Funzionalità interattive

Selezione e dettagli principali

Facendo clic su un core in qualsiasi visualizzazione (Core, NUMA o Socket) vengono visualizzate informazioni dettagliate nel riquadro dei dettagli inferiore:

- Informazioni processore: numero del processore logico, maschera e affinità

-

Gerarchia cache:

- Cache dati L1 (dimensioni, associatività, dimensioni riga)

- Cache istruzioni L1 (dimensioni, associatività, dimensione riga)

- Cache L2 (dimensioni, associatività, dimensioni riga)

- Cache L3 (dimensioni, associatività, dimensioni riga)

- Informazioni sulla topologia: assegnazioni di nodi, socket e gruppi NUMA

- Tipo di core: P-Core, E-Core o designazione standard di core

Funzionalità di ricerca

La visualizzazione Funzionalità CPU include una barra di ricerca che consente di individuare rapidamente funzionalità del processore specifiche:

- Fare clic sull'icona di ricerca

- Digitare il nome o l'abbreviazione della funzionalità

- L'elenco filtra automaticamente per visualizzare le funzionalità corrispondenti

- Cancellare la ricerca per ripristinare l'elenco completo

Attiva/disattiva mappa cache

In Visualizzazione principale passare da una modalità di visualizzazione all'altra:

- Modalità predefinita: mostra i core nella disposizione logica

- Modalità mappa cache: riorganizza i core per visualizzare le relazioni di condivisione della cache

Spostamento tra visualizzazioni

- Usare il riquadro di spostamento sinistro per passare da una visualizzazione all'altra

- Quando si visualizza un nodo o un socket NUMA specifico, fare di nuovo clic sulla stessa visualizzazione torna alla visualizzazione complessiva

- La visualizzazione corrente è evidenziata nel riquadro di spostamento

Impostazioni e personalizzazione

Accedere alle impostazioni tramite l'opzione Impostazioni nel menu di spostamento.

Impostazioni aspetto

Opzioni tema:

- Chiaro: Schema di colori chiaro ottimizzato per ambienti luminosi

- Scuro: combinazione di colori scura per ridurre l'affaticamento oculare

- Impostazione predefinita sistema: corrisponde automaticamente alle preferenze del tema di Windows

Save To File (Salva nel file)

Esportare i dati della topologia principale:

- Usare l'opzione Salva in per eseguire il dump dei dati della topologia core in un file

- Il formato di output è identico al risultato dello strumento da riga di comando

Informazioni sulla topologia di sistema

Tipi di base (architettura ibrida)

Le CPU moderne possono includere architetture ibride con diversi tipi di core:

- P-Core (prestazioni): core ad alte prestazioni ottimizzati per carichi di lavoro a thread singolo e impegnativi

- E-Cores (Efficienza): I core a risparmio energetico ottimizzati per i carichi di lavoro multithread e le attività in background.

L'interfaccia utente coreinfo identifica e differenzia chiaramente questi tipi di base in tutte le visualizzazioni applicabili.

Architettura NUMA

Che cos'è NUMA? L'accesso non uniforme alla memoria (NUMA) è una progettazione di memoria in cui ogni processore ha memoria locale a cui può accedere rapidamente e memoria remota che richiede la comunicazione tra processori.

Perché è importante:

- L'accesso alla memoria locale è notevolmente più veloce rispetto all'accesso remoto

- Le prestazioni dell'applicazione possono essere notevolmente influenzate dal posizionamento NUMA

- Comprendere la topologia NUMA è fondamentale per l'elaborazione ad alte prestazioni

Uso dell'interfaccia utente Coreinfo per l'ottimizzazione NUMA:

- Usare la visualizzazione NUMA per comprendere la topologia NUMA del sistema

- Controllare la visualizzazione prestazioni NUMA per visualizzare i costi di accesso alla memoria

- Ottimizzare il posizionamento dei thread/processi in base alle assegnazioni di nodi NUMA

- Usare la Visualizzazione Distanza Nucleo per analizzare la comunicazione tra core all'interno e tra nodi NUMA

Gerarchia cache

Livelli di cache:

- Cache L1: più piccola e veloce, suddivisa in cache di dati e istruzioni

- Cache L2: cache unificata più grande, in genere privata a ogni core

- Cache L3: cache unificata più grande, spesso condivisa tra più core

Uso delle informazioni sulla cache:

- Informazioni sui core che condividono le risorse della cache

- Ottimizzare la località dei dati per i core di condivisione della cache

- Usare la modalità Mappa cache in Visualizzazione principale per visualizzare i domini della cache

Uso di Coreinfo dalla riga di comando

Per ogni risorsa viene visualizzata una mappa dei processori visibili al sistema operativo che corrispondono alle risorse specificate, con '*' a rappresentare i processori applicabili. In un sistema a 4 core, ad esempio, verrà visualizzata una riga nell'output della cache con una mappa dei core condivisi 3 e 4.

Utilizzo:

coreinfo [-c][-f][-g][-l][-n][-s][-m][-v]

| Parametro | Descrizione |

|---|---|

| -c | Esegue il dump delle informazioni sui core. |

| -f | Esegue il dump delle informazioni sulle funzionalità di base. |

| -g | Esegue il dump delle informazioni sui gruppi. |

| -l | Esegue il dump delle informazioni sulle cache. |

| -n | Esegue il dump delle informazioni sui nodi NUMA. |

| -s | Esegue il dump delle informazioni sui socket. |

| -m | Esegue il dump dei costi di accesso a NUMA. |

| -v | Esegue il dump solo delle funzionalità correlate alla virtualizzazione, incluso il supporto per la conversione degli indirizzi di secondo livello. È necessario disporre dei diritti amministrativi per i sistemi Intel. |

Tutte le opzioni tranne -v sono selezionate per impostazione predefinita.

Output di Coreinfo:

Coreinfo v4.0 - Dump information on system CPU and memory topology

Copyright © 2008-2025 Mark Russinovich

Sysinternals - www.sysinternals.com

Intel(R) Core(TM) Ultra 7 165U

Intel64 Family 6 Model 170 Stepping 4, GenuineIntel

Microcode signature: 0000001E

Processor signature: 000A06A4

Maximum implemented CPUID leaves: 00000023 (Basic), 80000008 (Extended).

Maximum implemented address width: 48 bits (virtual), 46 bits (physical).

HTT * Hyperthreading enabled

CET * Supports Control Flow Enforcement Technology

Kernel CET - Kernel-mode CET Enabled

User CET * User-mode CET Allowed

X64 * Supports 64-bit mode

SMX - Supports Intel trusted execution

SKINIT - Supports AMD SKINIT

SGX - Supports Intel SGX

NX * Supports no-execute page protection

SMEP * Supports Supervisor Mode Execution Prevention

SMAP * Supports Supervisor Mode Access Prevention

PAGE1GB * Supports 1 GB large pages

PAE * Supports > 32-bit physical addresses

PAT * Supports Page Attribute Table

PSE * Supports 4 MB pages

PSE36 * Supports > 32-bit address 4 MB pages

PGE * Supports global bit in page tables

SS * Supports bus snooping for cache operations

VME * Supports Virtual-8086 mode

RDWRFSGSBASE * Supports direct GS/FS base access

FPU * Implements i387 floating point instructions

MMX * Supports MMX instruction set

MMXEXT - Implements AMD MMX extensions

3DNOW - Supports 3DNow! instructions

3DNOWEXT - Supports 3DNow! extension instructions

SSE * Supports Streaming SIMD Extensions

SSE2 * Supports Streaming SIMD Extensions 2

SSE3 * Supports Streaming SIMD Extensions 3

SSSE3 * Supports Supplemental SIMD Extensions 3

SSE4a - Supports Streaming SIMDR Extensions 4a

SSE4.1 * Supports Streaming SIMD Extensions 4.1

SSE4.2 * Supports Streaming SIMD Extensions 4.2

AES * Supports AES extensions

AVX * Supports AVX instruction extensions

AVX2 * Supports AVX2 instruction extensions

AVX-512-F - Supports AVX-512 Foundation instructions

AVX-512-DQ - Supports AVX-512 double and quadword instructions

AVX-512-IFAMA - Supports AVX-512 integer Fused multiply-add instructions

AVX-512-PF - Supports AVX-512 prefetch instructions

AVX-512-ER - Supports AVX-512 exponential and reciprocal instructions

AVX-512-CD - Supports AVX-512 conflict detection instructions

AVX-512-BW - Supports AVX-512 byte and word instructions

AVX-512-VL - Supports AVX-512 vector length instructions

FMA * Supports FMA extensions using YMM state

MSR * Implements RDMSR/WRMSR instructions

MTRR * Supports Memory Type Range Registers

XSAVE * Supports XSAVE/XRSTOR instructions

OSXSAVE * Supports XSETBV/XGETBV instructions

RDRAND * Supports RDRAND instruction

RDSEED * Supports RDSEED instruction

CMOV * Supports CMOVcc instruction

CLFSH * Supports CLFLUSH instruction

CX8 * Supports compare and exchange 8-byte instructions

CX16 * Supports CMPXCHG16B instruction

BMI1 * Supports bit manipulation extensions 1

BMI2 * Supports bit manipulation extensions 2

ADX * Supports ADCX/ADOX instructions

DCA - Supports prefetch from memory-mapped device

F16C * Supports half-precision instruction

FXSR * Supports FXSAVE/FXSTOR instructions

FFXSR - Supports optimized FXSAVE/FSRSTOR instruction

MONITOR * Supports MONITOR and MWAIT instructions

MOVBE * Supports MOVBE instruction

ERMSB * Supports Enhanced REP MOVSB/STOSB

PCLMULDQ * Supports PCLMULDQ instruction

POPCNT * Supports POPCNT instruction

LZCNT * Supports LZCNT instruction

SEP * Supports fast system call instructions

LAHF-SAHF * Supports LAHF/SAHF instructions in 64-bit mode

HLE - Supports Hardware Lock Elision instructions

RTM - Supports Restricted Transactional Memory instructions

DE * Supports I/O breakpoints including CR4.DE

DTES64 - Can write history of 64-bit branch addresses

DS - Implements memory-resident debug buffer

DS-CPL - Supports Debug Store feature with CPL

PCID * Supports PCIDs and settable CR4.PCIDE

INVPCID * Supports INVPCID instruction

PDCM * Supports Performance Capabilities MSR

RDTSCP * Supports RDTSCP instruction

TSC * Supports RDTSC instruction

TSC-DEADLINE * Local APIC supports one-shot deadline timer

TSC-INVARIANT * TSC runs at constant rate

xTPR * Supports disabling task priority messages

EIST * Supports Enhanced Intel Speedstep

ACPI * Implements MSR for power management

TM * Implements thermal monitor circuitry

TM2 * Implements Thermal Monitor 2 control

APIC * Implements software-accessible local APIC

x2APIC * Supports x2APIC

CNXT-ID - L1 data cache mode adaptive or BIOS

MCE * Supports Machine Check, INT18 and CR4.MCE

MCA * Implements Machine Check Architecture

PBE * Supports use of FERR#/PBE# pin

PSN - Implements 96-bit processor serial number

HTT * Hyperthreading

PREFETCHW * PrefetchW instruction support

HYPERVISOR * Hypervisor is present

VMX - Supports Intel hardware-assisted virtualization

EPT - Supports Intel extended page tables (SLAT)

URG - Supports Intel unrestricted guest

Logical to Physical Processor Map:

**------------ Physical Processor 0 (Hyperthreaded)

--*----------- Physical Processor 1

---*---------- Physical Processor 2

----*--------- Physical Processor 3

-----*-------- Physical Processor 4

------*------- Physical Processor 5

-------*------ Physical Processor 6

--------*----- Physical Processor 7

---------*---- Physical Processor 8

----------**-- Physical Processor 9 (Hyperthreaded)

------------*- Physical Processor 10

-------------* Physical Processor 11

Logical Processor to Socket Map:

************** Socket 0

Logical Processor to NUMA Node Map:

************** NUMA Node 0

No NUMA nodes.

Logical Processor to Cache Map:

**------------ Data Cache 0, Level 1, 48 KB, Assoc 12, LineSize 64

**------------ Instruction Cache 0, Level 1, 64 KB, Assoc 16, LineSize 64

**------------ Unified Cache 0, Level 2, 2 MB, Assoc 16, LineSize 64

************-- Unified Cache 1, Level 3, 12 MB, Assoc 12, LineSize 64

--*----------- Data Cache 1, Level 1, 32 KB, Assoc 8, LineSize 64

--*----------- Instruction Cache 1, Level 1, 64 KB, Assoc 8, LineSize 64

--****-------- Unified Cache 2, Level 2, 2 MB, Assoc 16, LineSize 64

---*---------- Data Cache 2, Level 1, 32 KB, Assoc 8, LineSize 64

---*---------- Instruction Cache 2, Level 1, 64 KB, Assoc 8, LineSize 64

----*--------- Data Cache 3, Level 1, 32 KB, Assoc 8, LineSize 64

----*--------- Instruction Cache 3, Level 1, 64 KB, Assoc 8, LineSize 64

-----*-------- Data Cache 4, Level 1, 32 KB, Assoc 8, LineSize 64

-----*-------- Instruction Cache 4, Level 1, 64 KB, Assoc 8, LineSize 64

------*------- Data Cache 5, Level 1, 32 KB, Assoc 8, LineSize 64

------*------- Instruction Cache 5, Level 1, 64 KB, Assoc 8, LineSize 64

------****---- Unified Cache 3, Level 2, 2 MB, Assoc 16, LineSize 64

-------*------ Data Cache 6, Level 1, 32 KB, Assoc 8, LineSize 64

-------*------ Instruction Cache 6, Level 1, 64 KB, Assoc 8, LineSize 64

--------*----- Data Cache 7, Level 1, 32 KB, Assoc 8, LineSize 64

--------*----- Instruction Cache 7, Level 1, 64 KB, Assoc 8, LineSize 64

---------*---- Data Cache 8, Level 1, 32 KB, Assoc 8, LineSize 64

---------*---- Instruction Cache 8, Level 1, 64 KB, Assoc 8, LineSize 64

----------**-- Data Cache 9, Level 1, 48 KB, Assoc 12, LineSize 64

----------**-- Instruction Cache 9, Level 1, 64 KB, Assoc 16, LineSize 64

----------**-- Unified Cache 4, Level 2, 2 MB, Assoc 16, LineSize 64

------------*- Data Cache 10, Level 1, 32 KB, Assoc 8, LineSize 64

------------*- Instruction Cache 10, Level 1, 64 KB, Assoc 8, LineSize 64

------------** Unified Cache 5, Level 2, 2 MB, Assoc 16, LineSize 64

-------------* Data Cache 11, Level 1, 32 KB, Assoc 8, LineSize 64

-------------* Instruction Cache 11, Level 1, 64 KB, Assoc 8, LineSize 64

Logical Processor to Group Map:

************** Group 0

Scarica Coreinfo(3 MB)Esegui ora da Sysinternals Live.

Scarica Coreinfo(3 MB)Esegui ora da Sysinternals Live.

Viene eseguito in:

- Client: Windows 11 e versioni successive.

- Server: Windows Server 2016 e versioni successive.