Mark Russinovich 제공

게시 날짜: 2025년 12월 16일

Coreinfo 다운로드(3MB)

Coreinfo 다운로드(3MB)

소개

Coreinfo는 논리 프로세서와 물리적 프로세서, NUMA 노드 및 해당 프로세서가 있는 소켓 간의 매핑과 각 논리 프로세서에 할당된 캐시를 보여 주는 유틸리티입니다. 하위 수준 Windows API(사용자 모드 및 커널 모드)를 사용하여 운영 체제에서 직접 자세한 CPU 토폴로지 정보를 검색합니다. 명령줄 버전은 별표(예: ''*)를 사용하여 논리 프로세서에 매핑의 표현을 출력합니다. UI는 논리 및 물리적 코어, NUMA 노드, 소켓, 캐시 계층 구조 및 실시간 성능 메트릭을 포함하여 시스템 CPU 토폴로지의 다양한 측면을 탐색하는 여러 특수 보기를 제공합니다. Coreinfo는 시스템의 프로세서 및 캐시 토폴로지에 대한 인사이트를 얻는 데 유용합니다.

설치

압축 파일을 디렉터리에 추출한 후, 아키텍처에 따라 해당 디렉터리에서 Coreinfo / Coreinfo64 또는 Coreinfo64a을(를) 입력하여 Coreinfo를 실행하십시오. UI 버전용 출시 CoreInfoEx / CoreInfoEx64 / CoreInfoEx64a.

참고: 일부 기능에는 전체 정보 검색을 위한 관리 권한이 필요할 수 있습니다.

사용자 인터페이스 개요

Coreinfo UI는 다음과 같은 몇 가지 주요 구성 요소로 구성됩니다.

주 창 레이아웃

- 위쪽 패널: CPU 이름, 아키텍처 및 코어 수를 포함한 시스템 정보를 표시합니다.

- 탐색 창 (왼쪽): 다양한 보기에 빠르게 액세스할 수 있습니다.

- 콘텐츠 영역 (가운데): 선택한 보기의 데이터 및 시각화를 표시합니다.

- 세부 정보 창 (아래쪽): 코어 또는 셀을 선택할 때 자세한 정보를 표시합니다.

- 설정: 액세스 모양 옵션 및 애플리케이션 기본 설정

전체 UI 레이아웃을 보여 주는 주 창, 어두운 모드

전체 UI 레이아웃을 보여 주는 주 창, 어두운 모드

네비게이션 뷰

왼쪽 탐색 창에서는 다음과 같은 6개의 특수한 보기에 액세스할 수 있습니다.

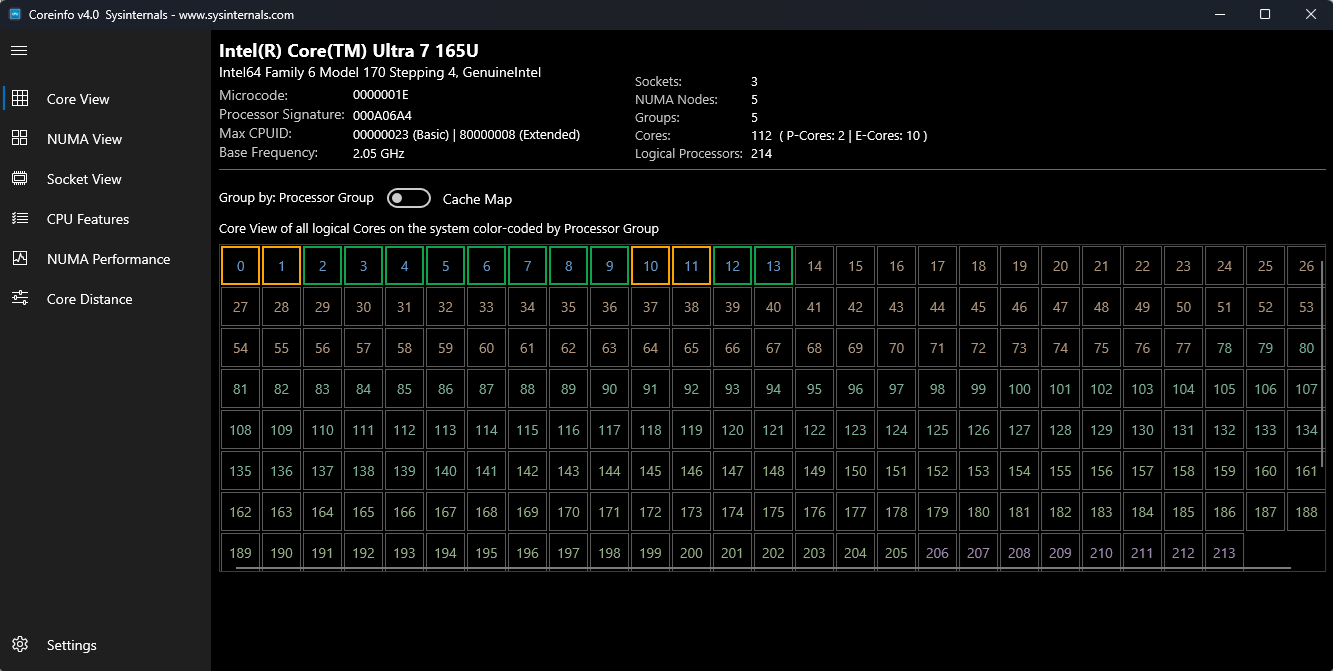

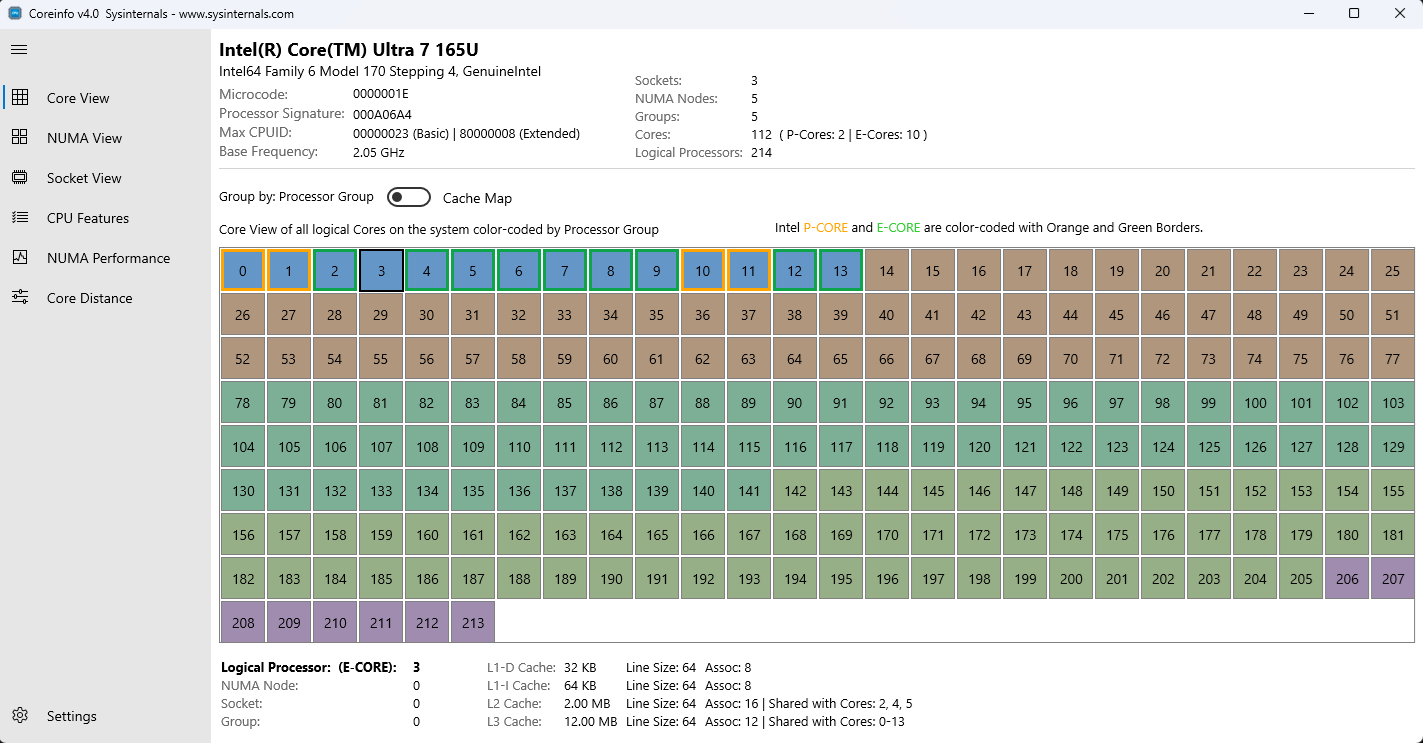

1. 핵심 보기

코어 뷰는 시스템의 모든 논리 프로세서를 그리드 레이아웃으로 표시하여 논리 코어와 해당 물리적 리소스 간의 관계를 보여 줍니다.

기능:

- 그리드 레이아웃: 각 셀은 논리 프로세서를 나타냅니다.

-

핵심 형식 표시기:

- P 코어(성능 코어) - 고유하게 색 지정

- 효율성 코어(E-코어) - 다른 색상으로 지정됨

- 표준 코어 - 기본 색 지정

- 캐시 매핑 토글: 기본 보기와 캐시 계층 구조 보기 간 전환

- 대화형 선택: 코어를 클릭하여 아래쪽 창에서 자세한 정보를 확인합니다.

표시된 정보:

- 논리 프로세서 번호

- 코어 유형(해당하는 경우 P-Core/E-Core)

- 연결된 캐시 수준(L1, L2, L3)

- NUMA 노드 할당

- 소켓 할당

- 그룹 할당

그리드 레이아웃으로 논리 프로세서를 표시하는 코어 뷰

그리드 레이아웃으로 논리 프로세서를 표시하는 코어 뷰

세부 정보 창 정보 (코어가 선택된 경우):

- 프로세서 마스크 및 선호도

- 캐시 계층 구조(데이터 캐시, 명령 캐시, 통합 캐시)

- 캐시 크기 및 연관성

- 캐시 줄 크기

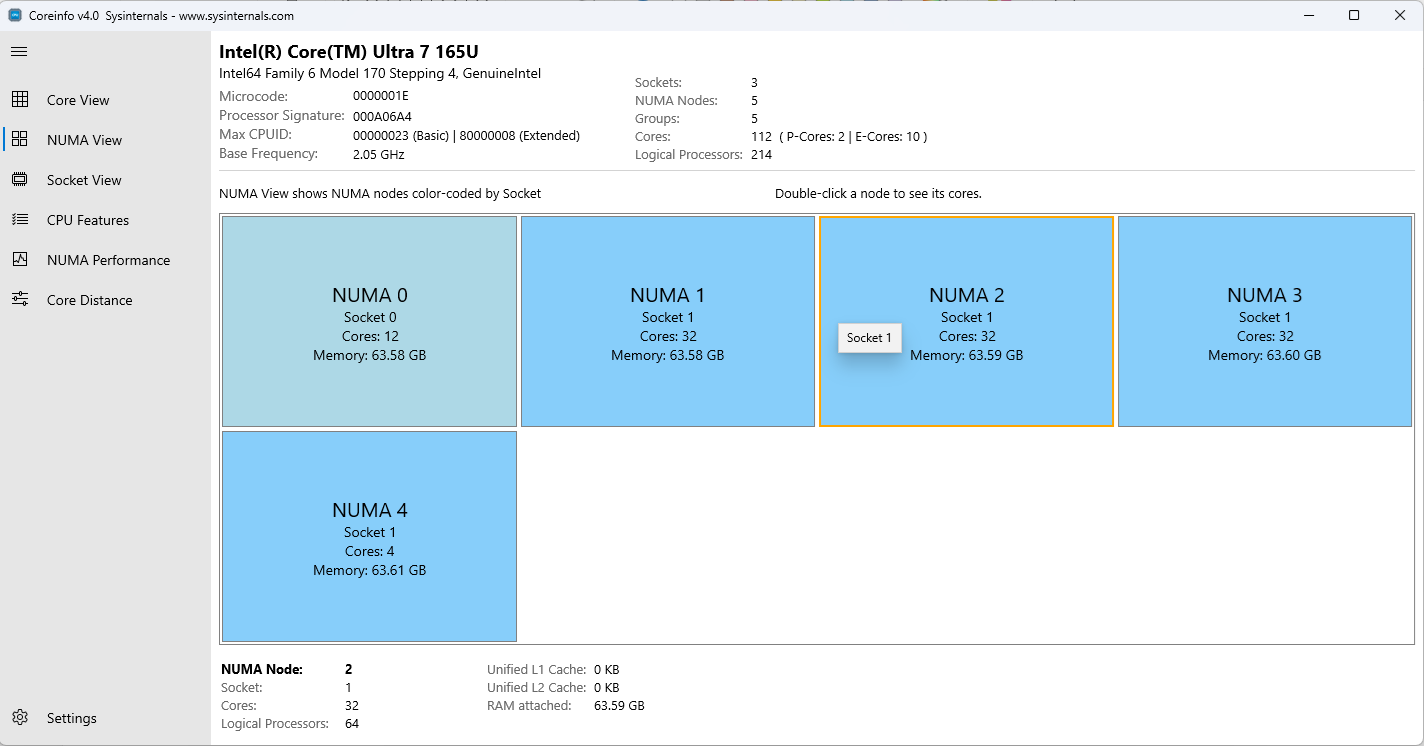

2. NUMA 보기

NUMA(비균일 메모리 액세스) 보기는 NUMA 노드 할당을 통해 코어를 구성하므로 메모리 지역성 및 액세스 패턴을 쉽게 이해할 수 있습니다.

기능:

- Node-Based 조직: NUMA 노드별로 그룹화된 코어

- 물리적 코어 및 논리 코어: 각 노드에 대한 두 개수를 모두 표시합니다.

- 메모리 정보: NUMA 노드당 사용 가능한 메모리 표시

-

대화형 탐색:

- NUMA 노드를 한 번 클릭하여 아래쪽 세부 정보 창에 세부 정보를 표시합니다.

- NUMA 노드를 두 번 클릭하여 선택한 NUMA 노드의 모든 코어를 보여 주는 핵심 보기로 이동합니다.

- 계층적 표시: NUMA 노드와 코어 간의 관계를 표시합니다.

표시된 정보:

- NUMA 노드 수

- NUMA 노드당 코어 수(물리적 및 논리적)

- 노드당 메모리 용량

- 노드 간 코어 분배

- 효율성 코어 수(해당하는 경우)

NUMA 노드로 구성된 코어를 보여주는 NUMA 뷰

NUMA 노드로 구성된 코어를 보여주는 NUMA 뷰

사용 사례:

- 메모리 액세스 패턴 최적화

- NUMA 인식 애플리케이션 성능 이해

- 최적의 성능을 위한 스레드/프로세스 배치 계획

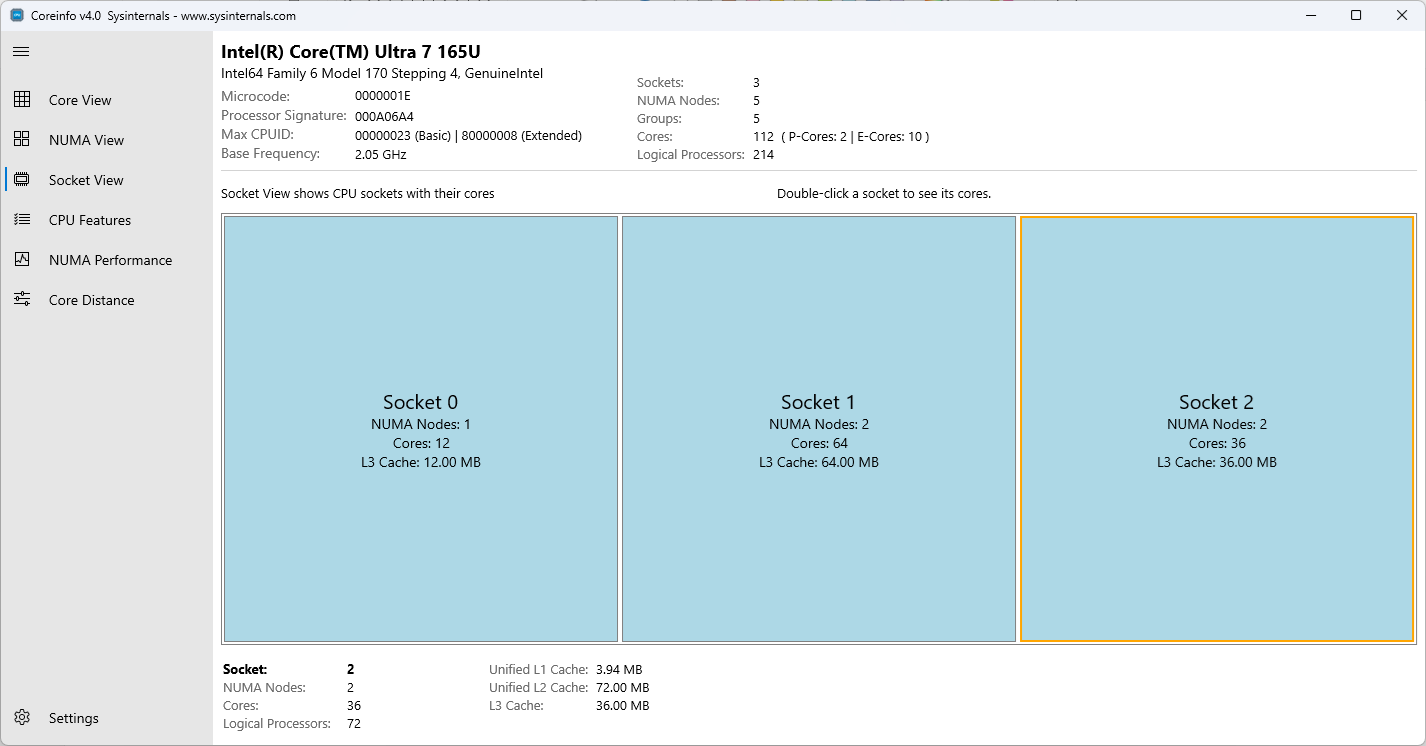

3. 소켓 보기

소켓 보기는 다중 소켓 시스템 및 소켓 수준 리소스 배포를 이해하는 데 유용한 물리적 CPU 소켓으로 구성된 코어를 표시합니다.

기능:

- 소켓 기반 그룹화: 물리적 소켓으로 구성된 코어

- 소켓 정보: 소켓 수 및 코어 배포

-

대화형 탐색:

- 소켓을 한 번 클릭하여 아래쪽 세부 정보 창에 세부 정보를 표시합니다.

- 소켓을 두 번 클릭하여 선택한 소켓의 모든 코어를 표시하는 핵심 보기로 이동합니다.

- 캐시 공유: 소켓 수준 캐시를 공유하는 코어 시각화

표시된 정보:

- 물리적 소켓 수

- 소켓당 코어 수(물리적 및 논리적)

- 소켓 수준 캐시 정보

- 소켓당 NUMA 노드

소켓 보기에서 CPU 소켓으로 구성된 코어를 보여 줍니다

소켓 보기에서 CPU 소켓으로 구성된 코어를 보여 줍니다

사용 사례:

- 다중 소켓 시스템 분석

- 소켓 간 통신 비용 이해

- 다중 소켓 서버에서 워크로드 배포 계획

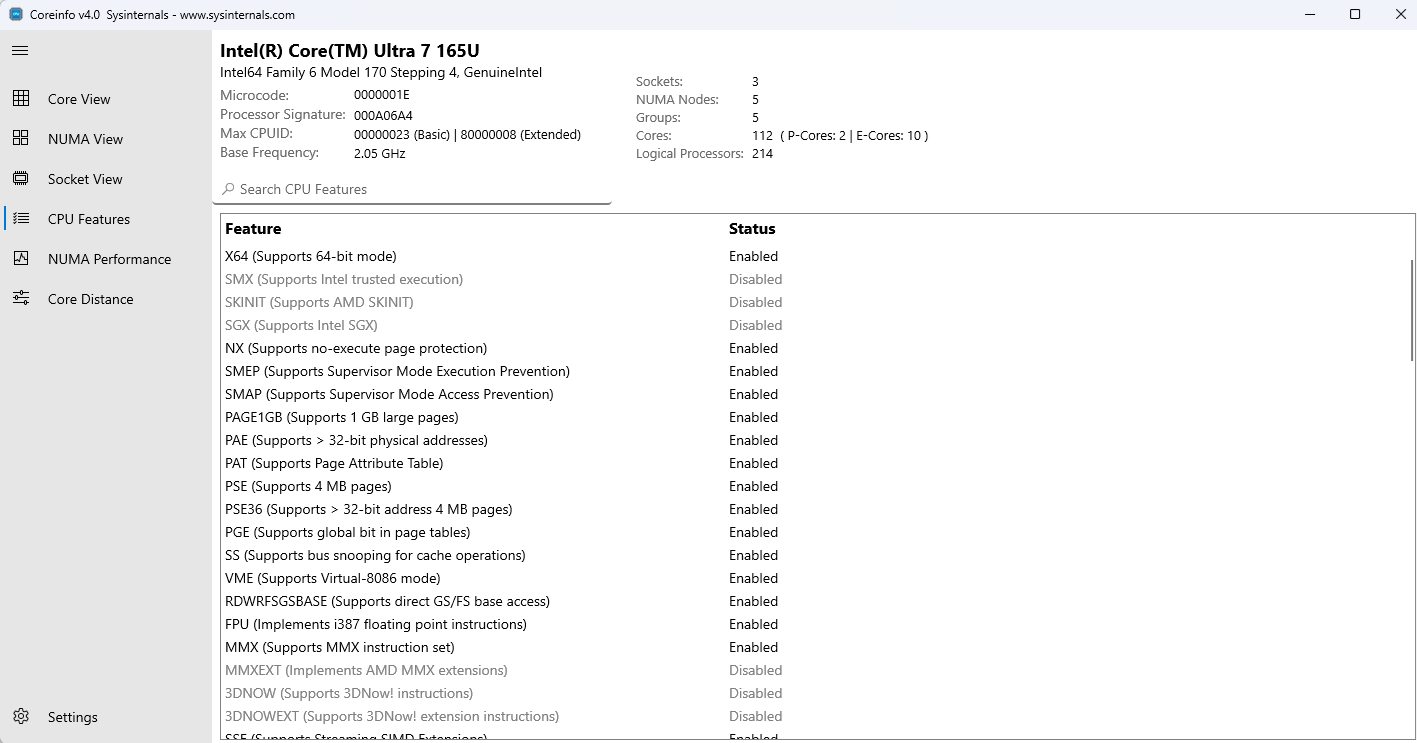

4. CPU 기능 보기

CPU 기능 보기에는 CPU에서 지원하는 프로세서 기능, 명령 집합 확장 및 하드웨어 기능의 포괄적인 목록이 표시됩니다.

기능:

- 검색 가능한 목록: 검색 창을 사용하여 특정 CPU 기능을 빠르게 찾습니다.

-

상태 표시기: 색 코딩을 사용하여 지원 및 비지원 기능을 명확히 시각적으로 표시하기

- 지원되는 기능은 일반 색으로 표시됩니다.

- 지원되지 않는/사용하지 않도록 설정된 기능이 회색으로 표시됨

-

기능 범주:

- 가상화(VMX, SVM, HYPERVISOR)

- 64비트 지원(EM64T, NX)

- 명령 집합(SSE, AVX, AES 등)

- 전원 관리(EIST, ACPI, 열)

- 보안 기능(SMX, SKINIT)

- 메모리 기능(PAE, PAT, PSE)

- 디버그 및 모니터링 기능

표시된 정보:

- 기능 약어

- 기능 상태(지원됨/지원되지 않음)

- 전체 기능 설명(세부 정보 창)

프로세서 기능 목록을 보여 주는 CPU 기능 보기

프로세서 기능 목록을 보여 주는 CPU 기능 보기

참고: 일부 가상화 기능(예: VMX, SVM)은 하이퍼바이저를 활성으로 실행하거나 가상 머신 내에서 실행할 때 사용할 수 없는 것으로 잘못 보고될 수 있습니다. 정확한 결과를 위해 하이퍼바이저가 실행되지 않은 시스템에서 Coreinfo를 실행해야 합니다.

사용 사례:

- 애플리케이션을 배포하기 전에 명령 집합 가용성 확인

- 가상화 지원 확인

- 프로세서 생성 및 기능 이해

- 누락된 CPU 기능과 관련된 성능 문제 디버깅

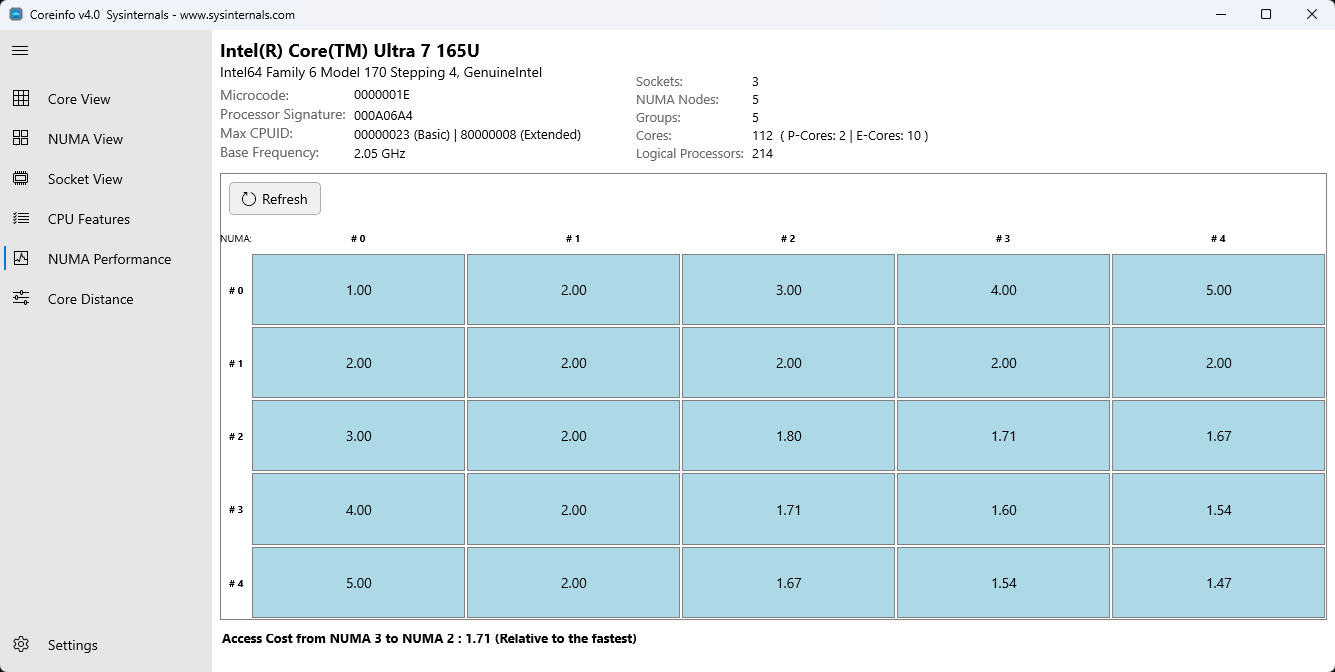

5. NUMA 성능 보기

NUMA 성능 보기는 NUMA 노드 간의 메모리 액세스 비용을 보여 주는 그리드 시각화를 제공하여 NUMA 시스템의 성능 병목 상태를 식별하는 데 도움이 됩니다.

기능:

- 그리드 시각화: NUMA 노드 간의 상대 메모리 액세스 비용을 표시하는 행렬

- 대화형 매트릭스: 셀 위로 마우스를 가져가서 자세한 성능 정보를 확인합니다.

- Real-Time 업데이트: 새로 고침 단추를 선택하여 성능 데이터가 동적으로 업데이트됨

- 상대 비용 표시: 다른 NUMA 노드에서 메모리에 액세스하는 상대적 비용을 표시합니다.

표시된 정보:

- N = NUMA 노드 수인 NxN 행렬

- 원본 NUMA 노드(행)에서 대상 NUMA 노드(열)로의 메모리 액세스 비용

- 상대적 성능 비용을 보여 주는 숫자 값

- 대각선 셀은 로컬 메모리 액세스를 표시합니다(일반적으로 가장 낮은 비용).

메모리 액세스 비용을 보여 주는 NUMA 성능 보기 NUMA 성능 표

메모리 액세스 비용을 보여 주는 NUMA 성능 보기 NUMA 성능 표

그리드 이해:

- 대각선 요소: 로컬 메모리 액세스(자체 메모리에 액세스하는 노드)를 나타냅니다. 일반적으로 가장 낮은 값

- 대각선 외부 요소: 상대적 비용이 높은 원격 메모리 액세스를 나타냅니다.

- 대칭: 액세스 비용이 방향에 따라 달라질 수 있으므로 행렬이 완벽하게 대칭이 아닐 수 있습니다.

사용 사례:

- NUMA 관련 성능 병목 상태 식별

- 메모리 할당 전략 최적화

- NUMA 시스템에 대한 프로세스 및 스레드 핀 고정 계획

- 노드 간 메모리 액세스 페널티 이해

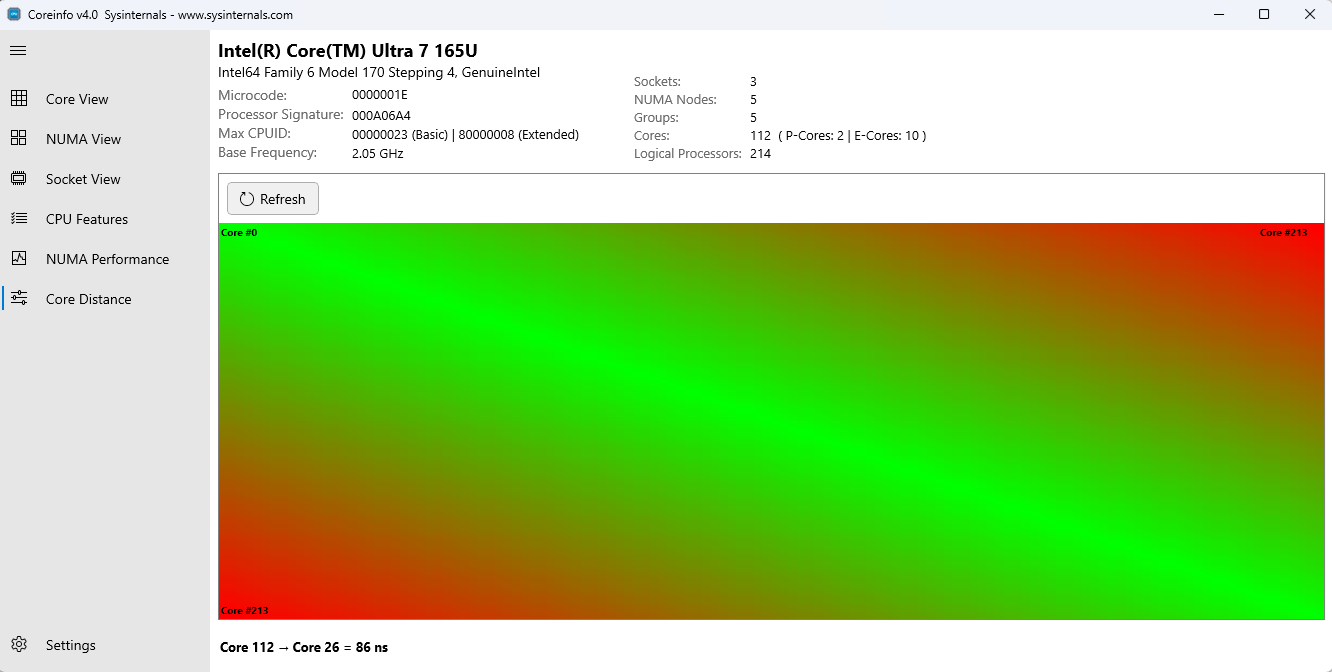

6. 코어 거리 보기

코어 거리 보기는 개별 CPU 코어 간의 통신 비용에 대한 자세한 열 지도를 표시하여 코어 간 대기 시간 및 통신 효율성에 대한 인사이트를 제공합니다.

기능:

-

Core-Level 열 지도: 코어 간의 상대 거리를 보여 주는 색으로 구분된 행렬

- 녹색/파랑 = 짧은 대기 시간(동일한 코어 클러스터, 공유 캐시)

- 노란색/주황색 = 중간 대기 시간(동일한 소켓, 다른 클러스터)

- 빨간색 = 높은 대기 시간(다른 소켓 또는 NUMA 노드)

- 대화형 탐색: 그리드 캔버스를 마우스로 가리키면 자세한 거리 정보를 볼 수 있습니다.

- 세분화된 분석: 코어-코어 관계를 최상의 세분성으로 표시합니다.

- 동적 새로 고침: 새로 고침 단추를 사용하여 업데이트된 코어 거리 데이터를 동적으로 가져옵니다.

표시된 정보:

- N = 논리 프로세서 수인 NxN 행렬

- 원본 코어(행)에서 대상 코어(열)까지의 상대 거리/대기 시간

- 핵심 관계의 빠른 시각적 식별을 위한 색 코딩

- 세부 정보 창의 자세한 거리 메트릭

코어 간 통신 비용을 보여주는 코어 거리 열 지도

코어 간 통신 비용을 보여주는 코어 거리 열 지도

거리 맵 이해:

- 대각선 요소: 항상 0(자체 코어)

- 낮은 거리(녹색): 코어 공유 L2 또는 L3 캐시

- 중간 거리(노란색): 동일한 소켓의 코어이지만 캐시 도메인이 다릅니다.

- 높은 거리(빨간색): 다른 소켓 또는 NUMA 노드의 코어

사용 사례:

- 스레드 선호도 최적화

- 캐시 일관성 도메인 이해

- 스레드 통신을 위한 최적의 코어 쌍 식별

- 다중 스레드 애플리케이션 성능 분석

- 저지연 애플리케이션에 대한 CPU 고정 핀 전략 계획

대화형 기능

핵심 선택 및 세부 정보

모든 보기(코어, NUMA 또는 소켓)에서 코어를 클릭하면 아래쪽 세부 정보 창에 자세한 정보가 표시됩니다.

- 프로세서 정보: 논리 프로세서 번호, 마스크 및 선호도

-

캐시 계층 구조:

- L1 데이터 캐시(크기, 결합성, 줄 크기)

- L1 명령 캐시(크기, 결합성, 줄 크기)

- L2 캐시(크기, 결합성, 줄 크기)

- L3 캐시(크기, 결합성, 줄 크기)

- 토폴로지 정보: NUMA 노드, 소켓 및 그룹 할당

- 코어 유형: P-Core, E-Core 또는 표준 코어 지정

검색 기능

CPU 기능 보기에는 특정 프로세서 기능을 빠르게 찾을 수 있는 검색 창이 포함되어 있습니다.

- 검색 아이콘 클릭

- 기능 이름 또는 약어 입력

- 목록이 자동으로 필터링되어 일치하는 기능을 표시합니다.

- 전체 목록을 복원하려면 검색을 취소합니다.

캐시 지도 전환

핵심 보기에서 두 시각화 모드 간에 전환합니다.

- 기본 모드: 코어를 논리적 배열로 표시

- 캐시 맵 모드: 코어를 재구성하여 캐시 공유 관계 시각화

보기 간 탐색

- 왼쪽 탐색 창을 사용하여 보기 간 전환

- 특정 NUMA 노드 또는 소켓을 볼 때 동일한 보기를 다시 클릭하면 전체 보기로 돌아갑니다.

- 탐색 창에서 현재 보기가 강조 표시됨

설정 및 사용자 지정

탐색 메뉴의 설정 옵션을 통해 설정에 액세스합니다.

모양 설정

테마 옵션:

- 밝게: 밝은 환경에 최적화된 밝은 색 구성표

- 어둡게: 눈의 피로를 줄이기 위한 어두운 색 구성표

- 시스템 기본값: Windows 테마 기본 설정과 자동으로 일치

파일에 저장

핵심 토폴로지 데이터 내보내기:

- 저장 위치 옵션을 사용하여 코어 토폴로지 데이터를 파일에 내보내기

- 출력 형식은 명령줄 도구 출력과 동일합니다.

시스템 토폴로지 이해

핵심 형식(하이브리드 아키텍처)

최신 CPU는 다양한 핵심 형식의 하이브리드 아키텍처를 특징으로 할 수 있습니다.

- P-코어(성능): 단일 스레드 및 까다로운 워크로드에 최적화된 고성능 코어

- E-코어(효율성): 백그라운드 작업 및 다중 스레드 워크로드에 최적화된 에너지 효율적인 코어

Coreinfo UI는 적용 가능한 모든 보기에서 이러한 핵심 형식을 명확하게 식별하고 구분합니다.

NUMA 아키텍처

NUMA란? NUMA(Non-Uniform Memory Access)는 각 프로세서가 빠르게 액세스할 수 있는 로컬 메모리와 프로세서 간 통신이 필요한 원격 메모리가 있는 메모리 디자인입니다.

중요한 이유:

- 로컬 메모리 액세스는 원격 액세스보다 훨씬 빠릅니다.

- 애플리케이션 성능은 NUMA 배치에 의해 크게 영향을 받을 수 있습니다.

- NUMA 토폴로지 이해는 고성능 컴퓨팅에 매우 중요합니다.

NUMA 최적화에 Coreinfo UI 사용:

- NUMA 뷰를 사용하여 시스템의 NUMA 토폴로지 이해

- NUMA 성능 보기를 확인하여 메모리 액세스 비용 확인

- NUMA 노드 할당에 따라 스레드/프로세스 배치 최적화

- 코어 거리 보기를 사용하여 NUMA 노드 내 및 전체 코어 간 통신 이해

캐시 계층 구조

캐시 수준:

- L1 캐시: 가장 작고 빠르며 데이터 및 명령 캐시로 분할

- L2 캐시: 더 큰 통합 캐시, 일반적으로 각 코어에 프라이빗

- L3 캐시: 여러 코어 간에 자주 공유되는 가장 큰 통합 캐시

캐시 정보 사용:

- 캐시 리소스를 공유하는 코어 이해

- 캐시 공유 코어에 대한 데이터 지역성 최적화

- 코어 뷰에서 캐시 맵 모드를 사용하여 캐시 도메인 시각화

명령줄에서 Coreinfo 사용

각 리소스에 대해 지정된 리소스에 해당하는 OS 표시 프로세서의 맵을 표시하며 '*'는 적용 가능한 프로세서를 나타냅니다. 예를 들어, 4코어 시스템에서 코어 3과 4가 공유하는 맵이 있는 캐시 출력의 한 줄이 있습니다.

사용:

coreinfo [-c][-f][-g][-l][-n][-s][-m][-v]

| 매개 변수 | Description |

|---|---|

| -c | 코어에 대한 덤프 정보. |

| -f | 핵심 기능 정보를 덤프합니다. |

| -g | 그룹에 대한 덤프 정보. |

| -l | 캐시에 정보를 덤프합니다. |

| -n | NUMA 노드에 대한 정보를 덤프합니다. |

| -s | 소켓에 대한 정보를 덤프합니다. |

| -m | 덤프 NUMA 액세스 비용. |

| -v | 2단계 주소 변환 지원을 포함하여 가상화 관련 기능만 덤프합니다. (Intel 시스템에 대한 관리 권한 필요). |

제외한 -v 모든 옵션은 기본적으로 선택됩니다.

핵심 정보 출력:

Coreinfo v4.0 - Dump information on system CPU and memory topology

Copyright © 2008-2025 Mark Russinovich

Sysinternals - www.sysinternals.com

Intel(R) Core(TM) Ultra 7 165U

Intel64 Family 6 Model 170 Stepping 4, GenuineIntel

Microcode signature: 0000001E

Processor signature: 000A06A4

Maximum implemented CPUID leaves: 00000023 (Basic), 80000008 (Extended).

Maximum implemented address width: 48 bits (virtual), 46 bits (physical).

HTT * Hyperthreading enabled

CET * Supports Control Flow Enforcement Technology

Kernel CET - Kernel-mode CET Enabled

User CET * User-mode CET Allowed

X64 * Supports 64-bit mode

SMX - Supports Intel trusted execution

SKINIT - Supports AMD SKINIT

SGX - Supports Intel SGX

NX * Supports no-execute page protection

SMEP * Supports Supervisor Mode Execution Prevention

SMAP * Supports Supervisor Mode Access Prevention

PAGE1GB * Supports 1 GB large pages

PAE * Supports > 32-bit physical addresses

PAT * Supports Page Attribute Table

PSE * Supports 4 MB pages

PSE36 * Supports > 32-bit address 4 MB pages

PGE * Supports global bit in page tables

SS * Supports bus snooping for cache operations

VME * Supports Virtual-8086 mode

RDWRFSGSBASE * Supports direct GS/FS base access

FPU * Implements i387 floating point instructions

MMX * Supports MMX instruction set

MMXEXT - Implements AMD MMX extensions

3DNOW - Supports 3DNow! instructions

3DNOWEXT - Supports 3DNow! extension instructions

SSE * Supports Streaming SIMD Extensions

SSE2 * Supports Streaming SIMD Extensions 2

SSE3 * Supports Streaming SIMD Extensions 3

SSSE3 * Supports Supplemental SIMD Extensions 3

SSE4a - Supports Streaming SIMDR Extensions 4a

SSE4.1 * Supports Streaming SIMD Extensions 4.1

SSE4.2 * Supports Streaming SIMD Extensions 4.2

AES * Supports AES extensions

AVX * Supports AVX instruction extensions

AVX2 * Supports AVX2 instruction extensions

AVX-512-F - Supports AVX-512 Foundation instructions

AVX-512-DQ - Supports AVX-512 double and quadword instructions

AVX-512-IFAMA - Supports AVX-512 integer Fused multiply-add instructions

AVX-512-PF - Supports AVX-512 prefetch instructions

AVX-512-ER - Supports AVX-512 exponential and reciprocal instructions

AVX-512-CD - Supports AVX-512 conflict detection instructions

AVX-512-BW - Supports AVX-512 byte and word instructions

AVX-512-VL - Supports AVX-512 vector length instructions

FMA * Supports FMA extensions using YMM state

MSR * Implements RDMSR/WRMSR instructions

MTRR * Supports Memory Type Range Registers

XSAVE * Supports XSAVE/XRSTOR instructions

OSXSAVE * Supports XSETBV/XGETBV instructions

RDRAND * Supports RDRAND instruction

RDSEED * Supports RDSEED instruction

CMOV * Supports CMOVcc instruction

CLFSH * Supports CLFLUSH instruction

CX8 * Supports compare and exchange 8-byte instructions

CX16 * Supports CMPXCHG16B instruction

BMI1 * Supports bit manipulation extensions 1

BMI2 * Supports bit manipulation extensions 2

ADX * Supports ADCX/ADOX instructions

DCA - Supports prefetch from memory-mapped device

F16C * Supports half-precision instruction

FXSR * Supports FXSAVE/FXSTOR instructions

FFXSR - Supports optimized FXSAVE/FSRSTOR instruction

MONITOR * Supports MONITOR and MWAIT instructions

MOVBE * Supports MOVBE instruction

ERMSB * Supports Enhanced REP MOVSB/STOSB

PCLMULDQ * Supports PCLMULDQ instruction

POPCNT * Supports POPCNT instruction

LZCNT * Supports LZCNT instruction

SEP * Supports fast system call instructions

LAHF-SAHF * Supports LAHF/SAHF instructions in 64-bit mode

HLE - Supports Hardware Lock Elision instructions

RTM - Supports Restricted Transactional Memory instructions

DE * Supports I/O breakpoints including CR4.DE

DTES64 - Can write history of 64-bit branch addresses

DS - Implements memory-resident debug buffer

DS-CPL - Supports Debug Store feature with CPL

PCID * Supports PCIDs and settable CR4.PCIDE

INVPCID * Supports INVPCID instruction

PDCM * Supports Performance Capabilities MSR

RDTSCP * Supports RDTSCP instruction

TSC * Supports RDTSC instruction

TSC-DEADLINE * Local APIC supports one-shot deadline timer

TSC-INVARIANT * TSC runs at constant rate

xTPR * Supports disabling task priority messages

EIST * Supports Enhanced Intel Speedstep

ACPI * Implements MSR for power management

TM * Implements thermal monitor circuitry

TM2 * Implements Thermal Monitor 2 control

APIC * Implements software-accessible local APIC

x2APIC * Supports x2APIC

CNXT-ID - L1 data cache mode adaptive or BIOS

MCE * Supports Machine Check, INT18 and CR4.MCE

MCA * Implements Machine Check Architecture

PBE * Supports use of FERR#/PBE# pin

PSN - Implements 96-bit processor serial number

HTT * Hyperthreading

PREFETCHW * PrefetchW instruction support

HYPERVISOR * Hypervisor is present

VMX - Supports Intel hardware-assisted virtualization

EPT - Supports Intel extended page tables (SLAT)

URG - Supports Intel unrestricted guest

Logical to Physical Processor Map:

**------------ Physical Processor 0 (Hyperthreaded)

--*----------- Physical Processor 1

---*---------- Physical Processor 2

----*--------- Physical Processor 3

-----*-------- Physical Processor 4

------*------- Physical Processor 5

-------*------ Physical Processor 6

--------*----- Physical Processor 7

---------*---- Physical Processor 8

----------**-- Physical Processor 9 (Hyperthreaded)

------------*- Physical Processor 10

-------------* Physical Processor 11

Logical Processor to Socket Map:

************** Socket 0

Logical Processor to NUMA Node Map:

************** NUMA Node 0

No NUMA nodes.

Logical Processor to Cache Map:

**------------ Data Cache 0, Level 1, 48 KB, Assoc 12, LineSize 64

**------------ Instruction Cache 0, Level 1, 64 KB, Assoc 16, LineSize 64

**------------ Unified Cache 0, Level 2, 2 MB, Assoc 16, LineSize 64

************-- Unified Cache 1, Level 3, 12 MB, Assoc 12, LineSize 64

--*----------- Data Cache 1, Level 1, 32 KB, Assoc 8, LineSize 64

--*----------- Instruction Cache 1, Level 1, 64 KB, Assoc 8, LineSize 64

--****-------- Unified Cache 2, Level 2, 2 MB, Assoc 16, LineSize 64

---*---------- Data Cache 2, Level 1, 32 KB, Assoc 8, LineSize 64

---*---------- Instruction Cache 2, Level 1, 64 KB, Assoc 8, LineSize 64

----*--------- Data Cache 3, Level 1, 32 KB, Assoc 8, LineSize 64

----*--------- Instruction Cache 3, Level 1, 64 KB, Assoc 8, LineSize 64

-----*-------- Data Cache 4, Level 1, 32 KB, Assoc 8, LineSize 64

-----*-------- Instruction Cache 4, Level 1, 64 KB, Assoc 8, LineSize 64

------*------- Data Cache 5, Level 1, 32 KB, Assoc 8, LineSize 64

------*------- Instruction Cache 5, Level 1, 64 KB, Assoc 8, LineSize 64

------****---- Unified Cache 3, Level 2, 2 MB, Assoc 16, LineSize 64

-------*------ Data Cache 6, Level 1, 32 KB, Assoc 8, LineSize 64

-------*------ Instruction Cache 6, Level 1, 64 KB, Assoc 8, LineSize 64

--------*----- Data Cache 7, Level 1, 32 KB, Assoc 8, LineSize 64

--------*----- Instruction Cache 7, Level 1, 64 KB, Assoc 8, LineSize 64

---------*---- Data Cache 8, Level 1, 32 KB, Assoc 8, LineSize 64

---------*---- Instruction Cache 8, Level 1, 64 KB, Assoc 8, LineSize 64

----------**-- Data Cache 9, Level 1, 48 KB, Assoc 12, LineSize 64

----------**-- Instruction Cache 9, Level 1, 64 KB, Assoc 16, LineSize 64

----------**-- Unified Cache 4, Level 2, 2 MB, Assoc 16, LineSize 64

------------*- Data Cache 10, Level 1, 32 KB, Assoc 8, LineSize 64

------------*- Instruction Cache 10, Level 1, 64 KB, Assoc 8, LineSize 64

------------** Unified Cache 5, Level 2, 2 MB, Assoc 16, LineSize 64

-------------* Data Cache 11, Level 1, 32 KB, Assoc 8, LineSize 64

-------------* Instruction Cache 11, Level 1, 64 KB, Assoc 8, LineSize 64

Logical Processor to Group Map:

************** Group 0

Coreinfo 다운로드(3MB)를 Sysinternals Live에서 지금 실행합니다.

Coreinfo 다운로드(3MB)를 Sysinternals Live에서 지금 실행합니다.

다음에서 실행됩니다.

- 클라이언트: Windows 11 이상.

- 서버: Windows Server 2016 이상.