Virtualizar instruções de CPU

- 8 minutos

O segredo para virtualizar uma CPU está na execução de instruções privilegiadas e não privilegiadas emitidas por processadores virtuais convidados. O conjunto de instruções do processador é documentado e fornecido no ISA. O seguinte vídeo descreve os problemas relacionados à virtualização de um ISA:

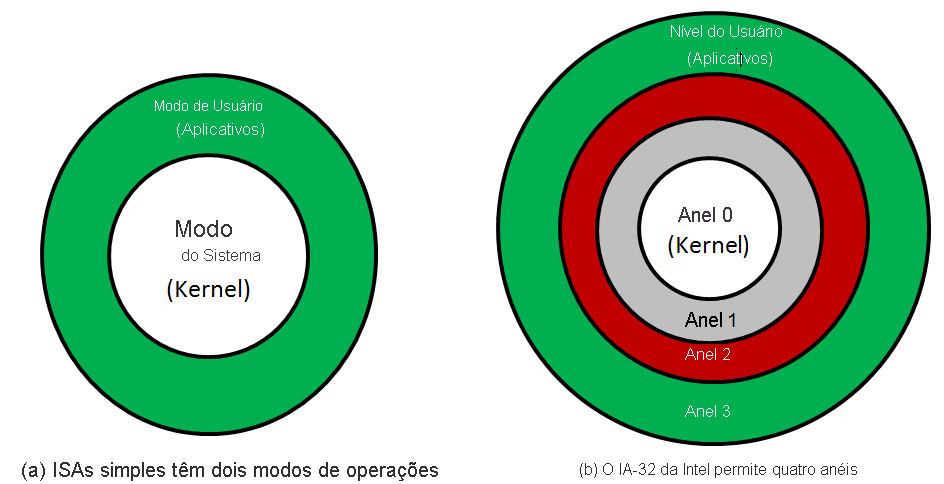

Privilégios especiais para recursos do sistema são permitidos pela definição de modos de operações (ou anéis) no ISA. Cada ISA de CPU geralmente especifica dois modos de operações, um modo do sistema (ou de supervisor/kernel/privilegiado) e o modo de usuário (veja a Figura 1a). O modo de sistema permite uma ampla acessibilidade aos componentes do sistema, enquanto o modo de usuário restringe essa acessibilidade. Em uma tentativa de fornecer isolamentos de segurança e recursos, os SOs em sistemas tradicionais são executados no modo de sistema, enquanto os aplicativos associados são executados no modo de usuário. No entanto, alguns ISAs dão suporte a mais de dois anéis. Por exemplo, o ISA Intel IA-32 dá suporte a quatro anéis (veja a Figura 1b). Em sistemas tradicionais, quando o Linux é implementado em um ISA IA-32, o SO é executado no Anel 0 e os processos de aplicativo são executados no Anel 3.

Figura 1: Modos de sistema de operações (ou anéis)

Uma instrução privilegiada é definida como uma instrução que intercepta no modo de usuário e que não intercepta no modo do sistema. Uma interceptação é uma transferência de controle para o modo de sistema no qual o hipervisor (como na virtualização) ou o SO (como em SOs tradicionais) executa alguma ação antes de alternar o controle de volta para o processo de origem. Interceptações ocorrem como efeitos colaterais da execução de instruções. No geral, as instruções podem ser classificadas em duas categorias diferentes: sensíveis e inócuas. As instruções sensíveis podem ser sensíveis ao controle ou sensíveis ao comportamento. Instruções sensíveis ao controle são aquelas que tentam modificar a configuração de recursos em um sistema, como alterar o modo de operação ou o temporizador da CPU. Um exemplo de instruções sensíveis ao controle é a LPSW (carregar palavra de status do processador) IBM System/370. A LPSW carregará a palavra de status do processador de uma localização na memória se a CPU estiver no modo de sistema; caso contrário, ela interceptará. A LPSW contém bits que determinam o estado da CPU. Por exemplo, um desses bits é o bit P, que especifica se a CPU está no modo de usuário ou no modo de sistema. Se a execução dessa instrução for permitida no modo de usuário, um programa mal-intencionado poderá alterar facilmente o modo de operação para privilegiado e obter controle sobre o sistema. Portanto, para proteger o sistema, essa instrução só pode ser executada no modo de sistema. Instruções sensíveis ao comportamento são aquelas cujos comportamentos são determinados pela configuração atual de recursos em um sistema. Um exemplo de instruções sensíveis ao comportamento é a POPF (Pop Stack into Flags Register) (Intel IA-32). A POPF exibe os registros de sinalizador de uma pilha mantida na memória. Um desses sinalizadores, chamado de sinalizador de habilitação interrupção, pode ser alterado somente no modo de sistema. Se a POPF for executada no modo de usuário por um programa que tenta exibir o sinalizador de habilitação de interrupção, a POPF funcionará como sem op (ou seja, sem operação). Portanto, o comportamento da POPF depende do modo de operação, sendo renderizada como sensível ao comportamento. Finalmente, quando a instrução não é sensível ao controle nem ao comportamento, ela é inócua.

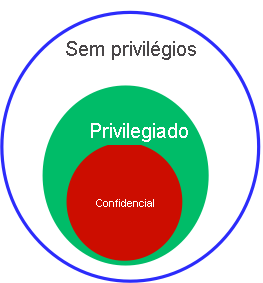

De acordo com Popek e Goldberg (1974), um hipervisor poderá ser construído se obedecer a três propriedades: eficiência, controle de recurso e equivalência. A eficiência envolve a execução de todas as instruções inócuas diretamente no hardware sem nenhuma interferência pelo hipervisor. O controle de recurso sugere que não é possível que nenhum software convidado altere a configuração de recursos em um sistema. A equivalência requer um comportamento idêntico de um programa em execução em uma VM ou em um SO tradicional sem virtualização. Uma exceção é a diferença no desempenho. A proposta (ou teorema) de Popek e Goldberg implica que um hipervisor poderá ser construído somente se o conjunto de instruções sensíveis for um subconjunto do conjunto de instruções privilegiadas. Ou seja, as instruções que interferem no funcionamento correto do sistema (por exemplo, instruções sensíveis, como LPSW) sempre devem interceptar no modo de usuário. A Figura 2 ilustra o teorema de Popek e Goldberg.1

Figura 2: Teorema de Popek e Goldberg

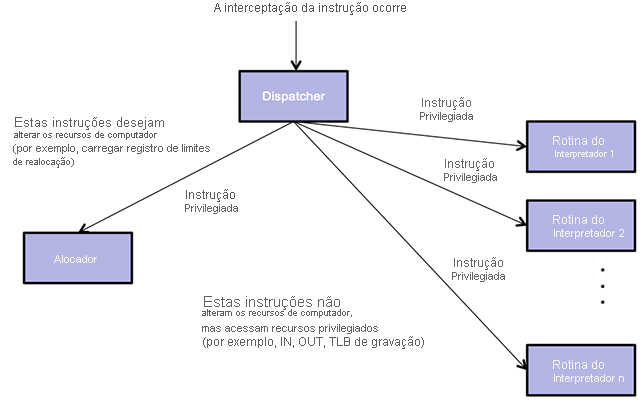

Por fim, vamos discutir como uma interceptação pode ser manipulada em um sistema. Especificamente, descrevemos interceptações no contexto da virtualização da CPU. A Figura 3 demonstra como um hipervisor pode manipular uma interceptação de instrução. As funções de manipulação de interceptações do hipervisor podem ser divididas em três partes principais: dispatcher, alocador e um conjunto de rotinas do interpretador. Primeiro, uma instrução privilegiada intercepta o dispatcher do hipervisor. Se o hipervisor reconhecer que a instrução está tentando alterar os recursos do sistema, ele a direcionará para o alocador; caso contrário, ele a enviará para uma rotina de interpretador correspondente. O alocador decide como os recursos do sistema devem ser alocados de maneira não conflitante e obedece à solicitação da instrução adequadamente. As rotinas do interpretador emulam (mais sobre a emulação em breve) os efeitos da instrução ao operar em recursos virtuais. Quando a instrução é manipulada completamente (por exemplo, concluída), o controle é passado de volta para o software convidado na instrução que vem imediatamente após a que causou a interceptação.

Figura 3: demonstração de uma interceptação para um hipervisor. O hipervisor inclui três componentes principais: o dispatcher, o alocador e as rotinas do interpretador

Referências

- Popek, J., e Goldberg, R. (1974). Requisitos formais para arquiteturas virtualizáveis de terceira geração Commun. ACM, Vol. 17, Nº 7.