Observação

O acesso a essa página exige autorização. Você pode tentar entrar ou alterar diretórios.

O acesso a essa página exige autorização. Você pode tentar alterar os diretórios.

Esta página descreve o modelo IoMmu introduzido no WDDM 2.0. Consulte Isolamento de GPU baseado em IOMMU e remapeamento de DMA do IOMMU para obter atualizações mais recentes do IOMMU.

Visão geral

Uma unidade de gerenciamento de memória de entrada e saída (IOMMU) é um componente de hardware que conecta um barramento de E/S compatível com DMA à memória do sistema. Ele mapeia endereços virtuais visíveis ao dispositivo para endereços físicos, tornando-o útil na virtualização.

No modelo de IoMmu do WDDM 2.0, cada processo tem um único espaço de endereço virtual que é:

- Compartilhado entre a CPU e a GPU.

- Gerenciado pelo gerenciador de memória do sistema operacional.

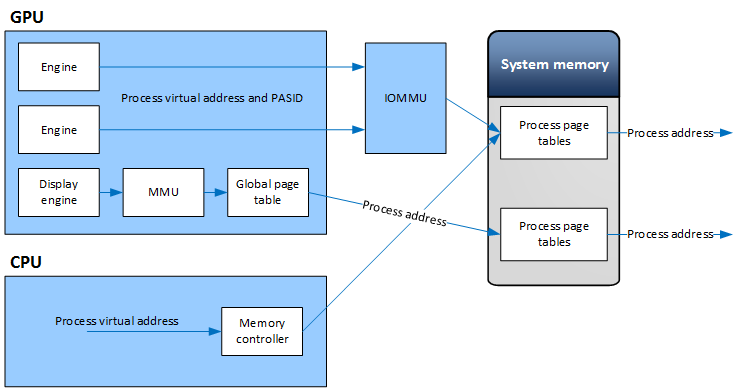

Para acessar a memória, a GPU envia uma solicitação de dados para um IOMMU compatível. A solicitação inclui um endereço virtual compartilhado e um identificador de espaço de endereço do processo (PASID). O IOMMU executa a conversão de endereço usando a tabela de páginas compartilhadas. Esta ação é ilustrada no diagrama a seguir.

Diagrama que mostra a conversão do espaço de endereço do processo IOMMU no WDDM 2.0.

Diagrama que mostra a conversão do espaço de endereço do processo IOMMU no WDDM 2.0.

O driver de exibição no modo kernel (KMD) expressa o suporte ao modelo IoMmu definindo os limites DXGK_VIDMMCAPS::IoMmuSupported. Quando esse sinalizador é definido, o gerenciador de memória de vídeo (VidMm) registra automaticamente qualquer processo usando a GPU com o IOMMU e obtém um PASID para esse espaço de endereço do processo. O PASID é passado para o driver durante a criação do dispositivo.

O VidMm mapeia as alocações primárias no segmento de abertura antes de serem exibidas, garantindo que o controlador de exibição tenha acesso físico a essas alocações.

No modelo de IoMmu, o driver de vídeo do modo de usuário (UMD) continua a alocar memória de vídeo para a GPU usando o serviço Allocate do VidMm. Esse processo permite que o UMD:

- Siga o modelo de residência.

- Dê suporte ao modelo de compartilhamento de recursos do DirectX.

- Certifique-se de que as superfícies primárias estejam visíveis para o kernel e mapeadas na abertura antes de serem exibidas.

O UMD gerencia inteiramente o primeiro nível de conversão (endereço do recurso de bloco para endereço compartilhado da CPU/GPU) no modo de usuário.