Примечание.

Для доступа к этой странице требуется авторизация. Вы можете попробовать войти или изменить каталоги.

Для доступа к этой странице требуется авторизация. Вы можете попробовать изменить каталоги.

Марк Руссинович

Опубликовано: 16 декабря 2025 г.

Coreinfo(3 МБ)

Coreinfo(3 МБ)

Введение

Coreinfo — это служебная программа, показывающая сопоставление между логическими процессорами и физическим процессором, узлом NUMA и сокетом, на котором они находятся, а также назначенным кэшем каждому логическому процессору. Он использует низкоуровневые API Windows (режим пользователя и режим ядра) для получения подробных сведений о топологии ЦП непосредственно из операционной системы. Версия командной строки выводит представление сопоставления с логическим процессором со звездочкой, например "*". Пользовательский интерфейс предоставляет несколько специализированных представлений для изучения различных аспектов топологии ЦП системы, включая логические и физические ядра, узлы NUMA, сокеты, иерархии кэша и метрики производительности в режиме реального времени. Coreinfo полезна для получения сведений о топологии процессора и кэша системы.

Установка

Извлеките архив в каталог, а затем выполните команду Coreinfo из этого каталога Coreinfo / Coreinfo64 или Coreinfo64a, в зависимости от архитектуры. Запустите версию пользовательского интерфейса CoreInfoEx / CoreInfoEx64 / CoreInfoEx64a.

Примечание: Для получения полных сведений некоторые функции могут требовать права администратора.

Обзор пользовательского интерфейса

Пользовательский интерфейс Coreinfo состоит из нескольких ключевых компонентов:

Макет главного окна

- Верхняя панель: отображает сведения о системе, включая имя ЦП, архитектуру и количество ядер

- Область навигации (слева): обеспечивает быстрый доступ к разным представлениям

- Область содержимого (центр): отображаются данные и визуализации выбранного представления

- Панель деталей (внизу): отображает подробные сведения при выборе ядер или ячеек

- Параметры: доступ к параметрам внешнего вида и параметрам приложения

Обзор главного окна, темный режим , полное представление пользовательского интерфейса в темном режиме

, полное представление пользовательского интерфейса в темном режиме

Представления навигации

Левая панель навигации предоставляет доступ к шести специализированным представлениям:

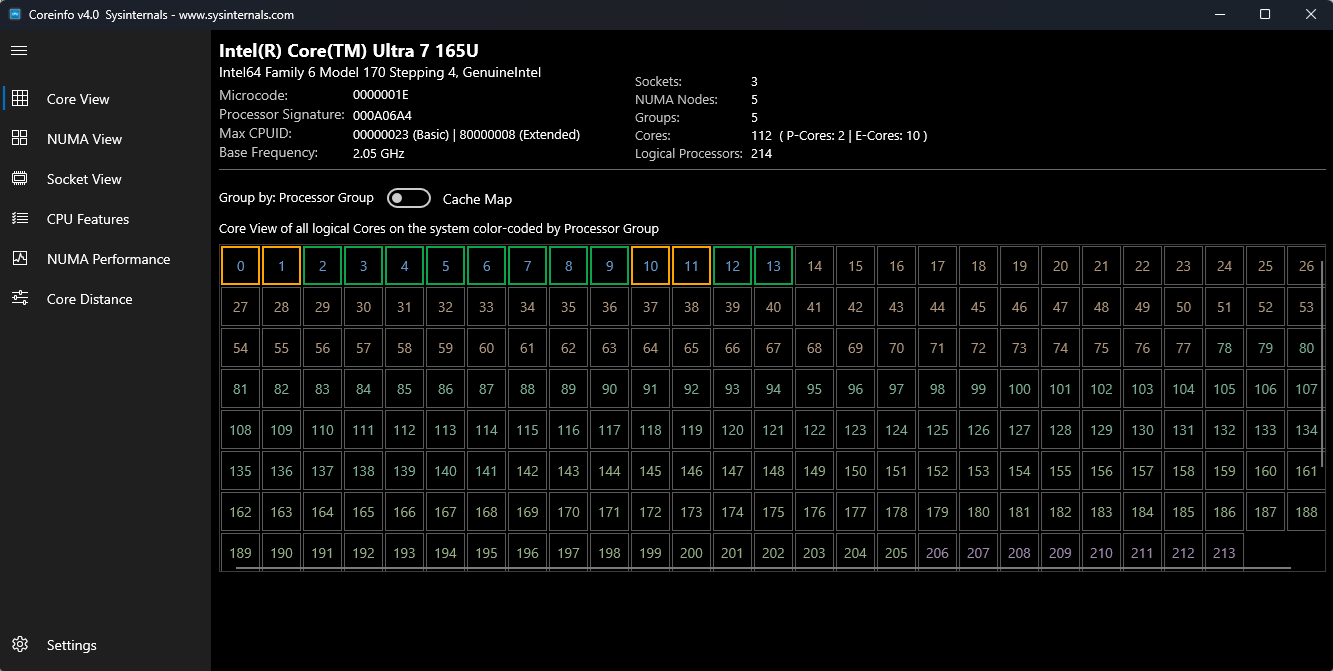

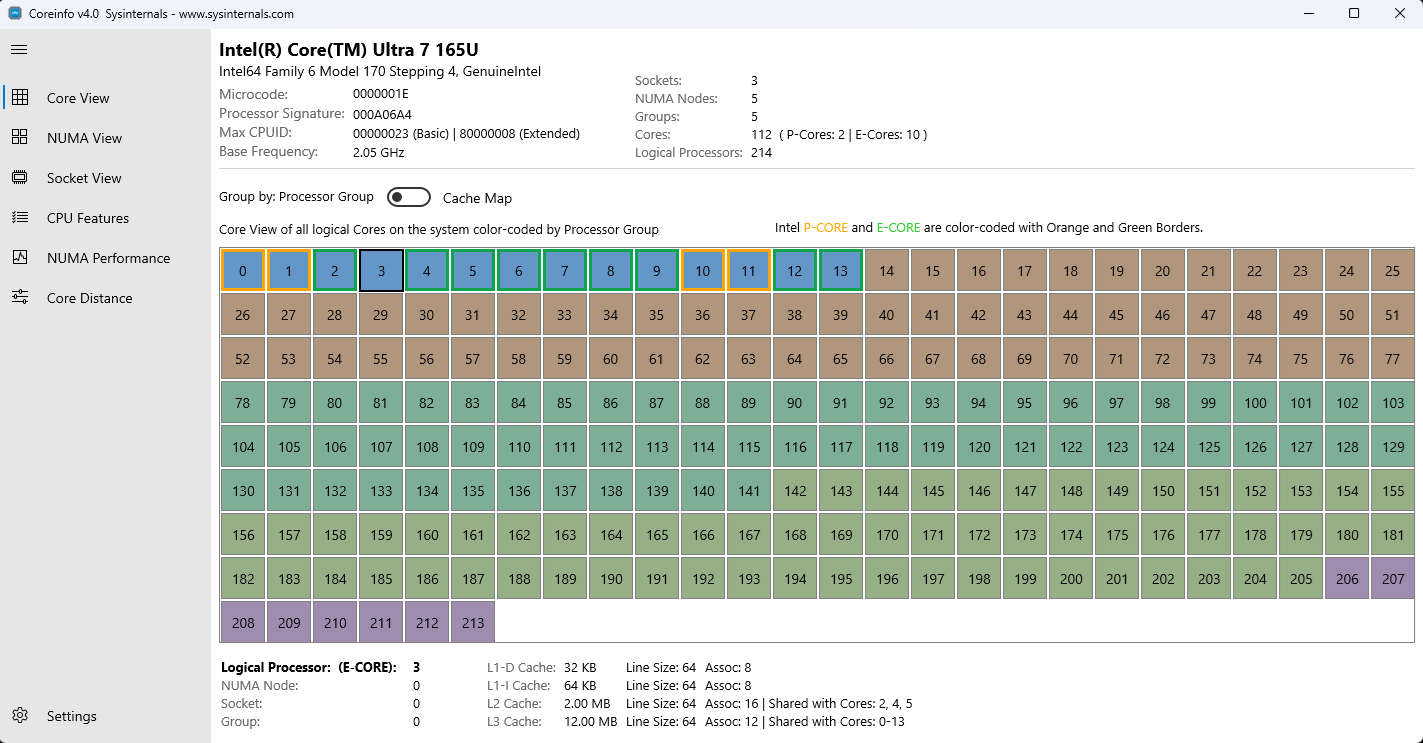

1. Основное представление

В представлении Core отображаются все логические процессоры в системе в макете сетки, показывающие связь между логическими ядрами и их физическими ресурсами.

Функции:

- Макет сетки: каждая ячейка представляет логический процессор

-

Основные индикаторы типов:

- P-Cores (ядра производительности) — выделены цветом

- E-Cores (ядра эффективности) — окрашены по-разному

- Стандартные процессорные ядра — цвет по умолчанию

- Переключатель сопоставления кэша: переключение между представлением по умолчанию и представлением иерархии кэша

- Интерактивный выбор: щелкните любое ядро, чтобы просмотреть подробные сведения на нижней панели

Отображаемые сведения:

- Логический номер процессора

- Тип ядра (P-Core/E-Core, если применимо)

- Связанные уровни кэша (L1, L2, L3)

- Назначение узла NUMA

- Назначение сокета

- Назначение группы

отображает логические процессоры в сеточной компоновке

отображает логические процессоры в сеточной компоновке

Информация об области сведений (при выборе ядра):

- Маска процессорных ядер и привязка

- Иерархия кэша (кэш данных, кэш инструкций, унифицированный кэш)

- Размеры кэша и ассоциативность

- Размеры строк кэша

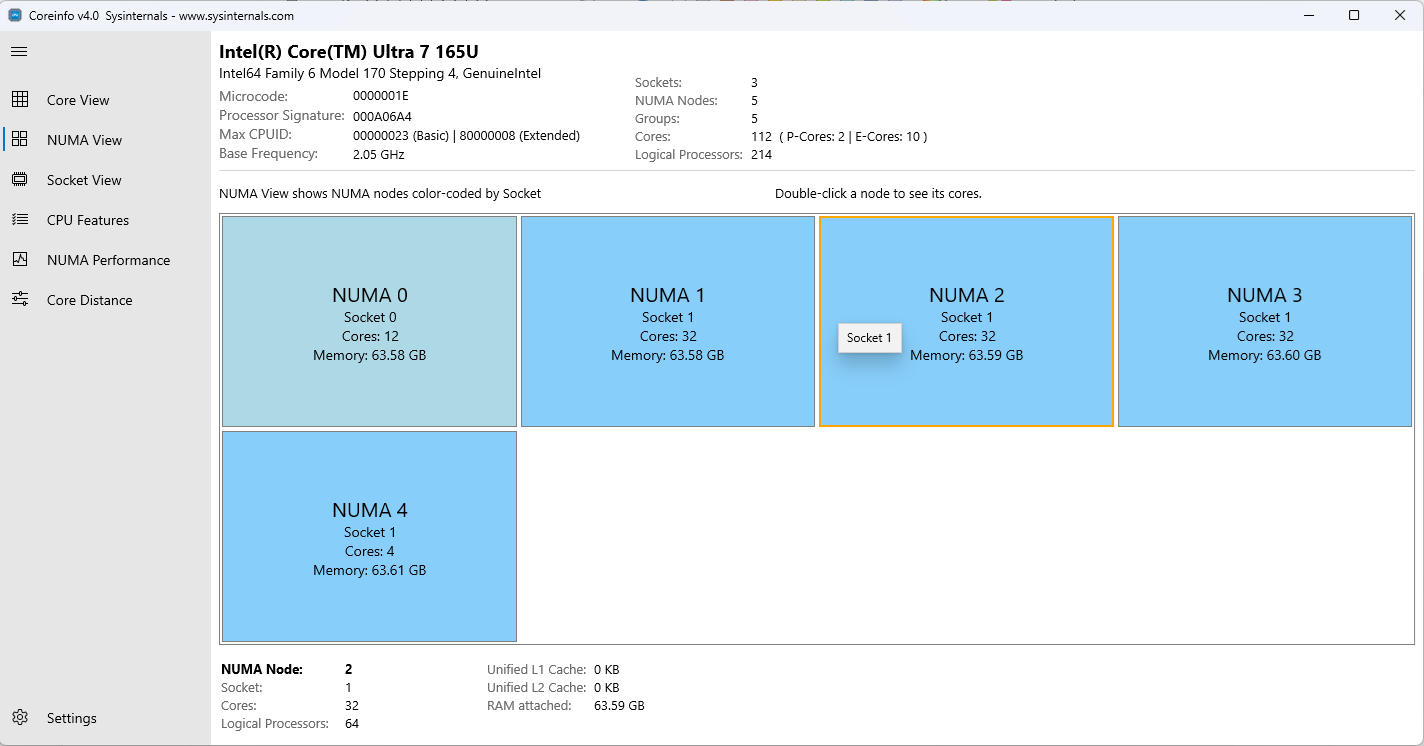

2. Представление NUMA

Представление NUMA (не единообразный доступ к памяти) упорядочивает ядра по назначениям узлов NUMA, что упрощает понимание локальности памяти и шаблонов доступа.

Функции:

- Организация на основе узлов: ядра, сгруппированные по узлам NUMA

- Физические и логические ядра: показывает оба числа для каждого узла.

- Сведения о памяти: отображает доступную память для узла NUMA

-

Интерактивная навигация:

- Щелкните один раз узел NUMA, чтобы отобразить его сведения в нижней панели сведений.

- Дважды щелкните на узле NUMA, чтобы перейти в режим ядра, показывающий все ядра выбранного узла NUMA.

- Иерархическое отображение: показывает связь между узлами NUMA и ядрами

Отображаемые сведения:

- Число узлов NUMA

- Количество ядер (физических и логических) на узел NUMA

- Емкость памяти на узел

- Основное распределение между узлами

- Количество энергоэффективных ядер (если применимо)

NUMA View, показывающий ядра, организованные по узлам NUMA

NUMA View, показывающий ядра, организованные по узлам NUMA

Варианты использования:

- Оптимизация шаблонов доступа к памяти

- Общие сведения о производительности приложения с поддержкой NUMA

- Планирование размещения потоков и процессов для оптимальной производительности

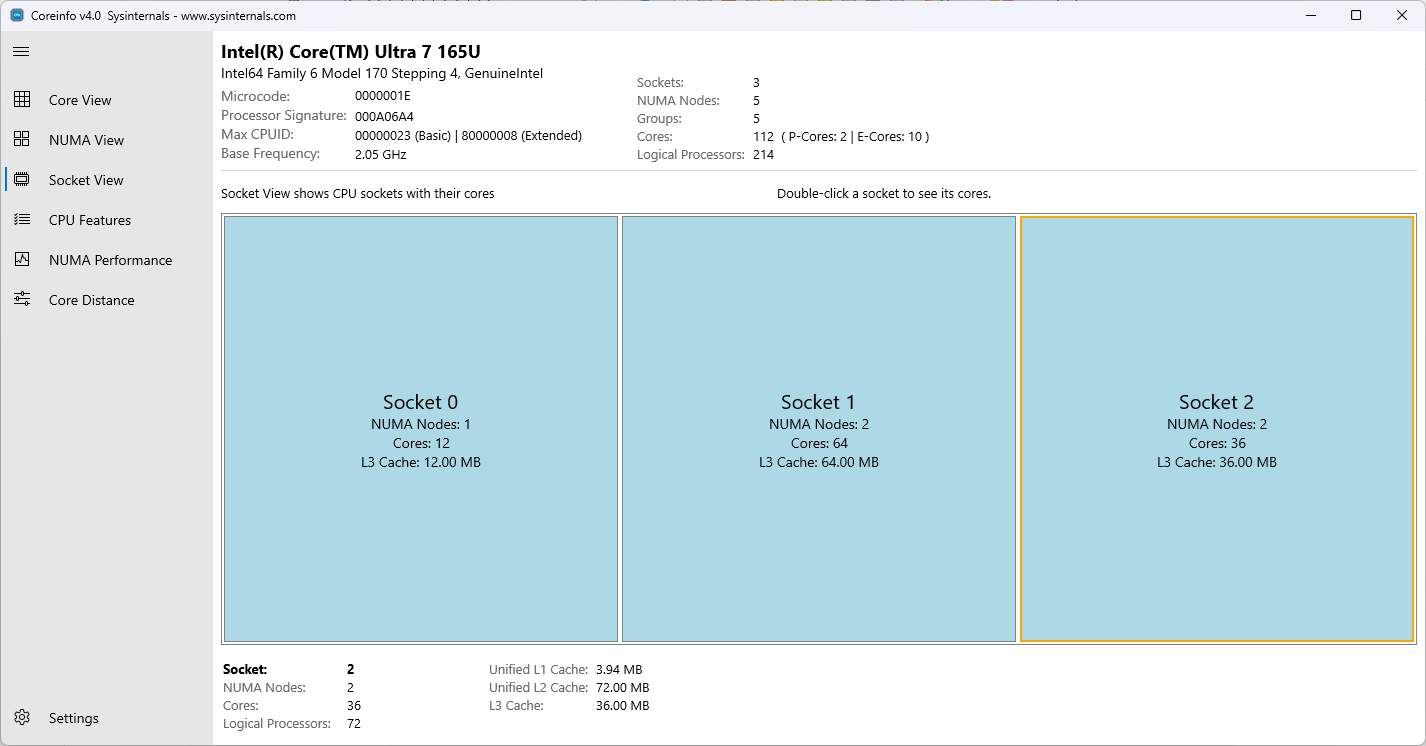

3. Отображение сокета

В представлении сокетов отображаются ядра, упорядоченные по физическому сокету ЦП, полезные для понимания систем с несколькими сокетами и распределения ресурсов на уровне сокетов.

Функции:

- Группирование на основе сокетов: ядра, организованные на основе физических сокетов

- Сведения о сокете: количество сокетов и распределение ядер

-

Интерактивная навигация:

- Щелкните сокет однократным нажатием, чтобы отобразить сведения в нижней панели сведений.

- Дважды щелкните на сокет, чтобы перейти к основному представлению, отображающему все ядра из выбранного сокета.

- Совместное использование кэша: визуализация того, какие ядра делят кэши уровня сокетов

Отображаемые сведения:

- Количество физических сокетов

- Ядра на каждый разъём (физический и логический)

- Сведения о кэше уровня сокета

- NUMA-узлы на каждый сокет

Представление сокета, показывающее ядра, организованные гнездами процессора

Представление сокета, показывающее ядра, организованные гнездами процессора

Варианты использования:

- Анализ системы с несколькими сокетами

- Понимание стоимости межсокетного взаимодействия

- Планирование распределения рабочих нагрузок на серверах с несколькими сокетами

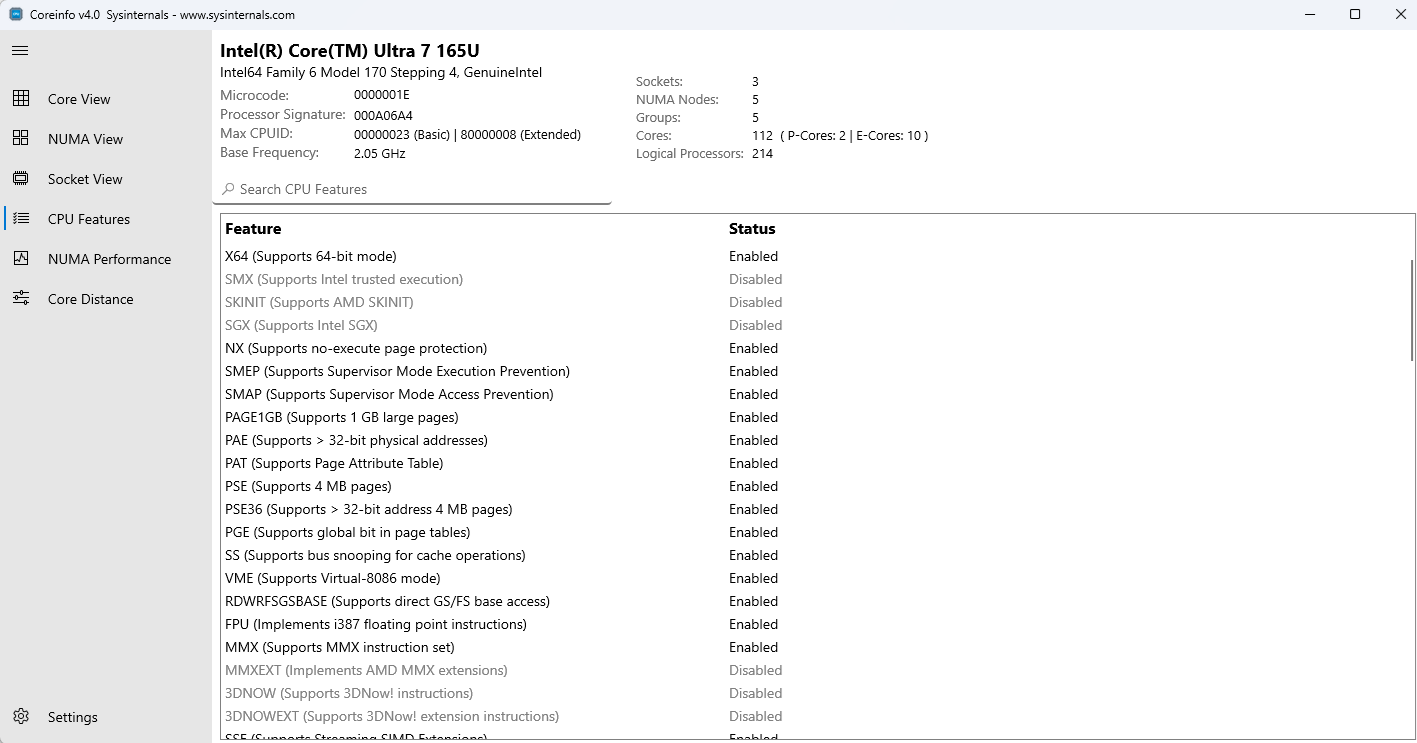

4. Представление функций ЦП

В представлении функций ЦП отображается полный список возможностей процессора, расширений наборов инструкций и аппаратных функций, поддерживаемых ЦП.

Функции:

- Список, доступный для поиска: быстрое поиск определенных функций ЦП с помощью панели поиска

-

Индикаторы состояния: четкое визуальное указание поддерживаемых или неподдерживаемых функций с помощью цветового кодирования

- Поддерживаемые функции отображаются в обычном цвете

- Неподдерживаемые или отключенные функции отображаются серым цветом

-

Категории компонентов:

- Виртуализация (VMX, SVM, ГИПЕРВИЗОР)

- 64-разрядная поддержка (EM64T, NX)

- Наборы инструкций (SSE, AVX, AES и т. д.)

- Управление питанием (EIST, ACPI, термальный менеджмент)

- Функции безопасности (SMX, SKINIT)

- Функции памяти (PAE, PAT, PSE)

- Функции отладки и мониторинга

Отображаемые сведения:

- Сокращение компонента

- Состояние функции (поддерживается или не поддерживается)

- Полное описание функции (в области сведений)

Просмотр функций ЦП, показывающий список возможностей процессора

Просмотр функций ЦП, показывающий список возможностей процессора

Примечание: Некоторые функции виртуализации (например, VMX, SVM) могут быть неправильно сообщены как недоступные при запуске с активным гипервизором или при запуске из виртуальной машины. Coreinfo должен выполняться на системе без гипервизора для получения точных результатов.

Варианты использования:

- Проверка доступности набора инструкций перед развертыванием приложений

- Проверка поддержки виртуализации

- Общие сведения о создании и возможностях процессора

- Отладка проблем с производительностью, связанных с отсутствующими функциями ЦП

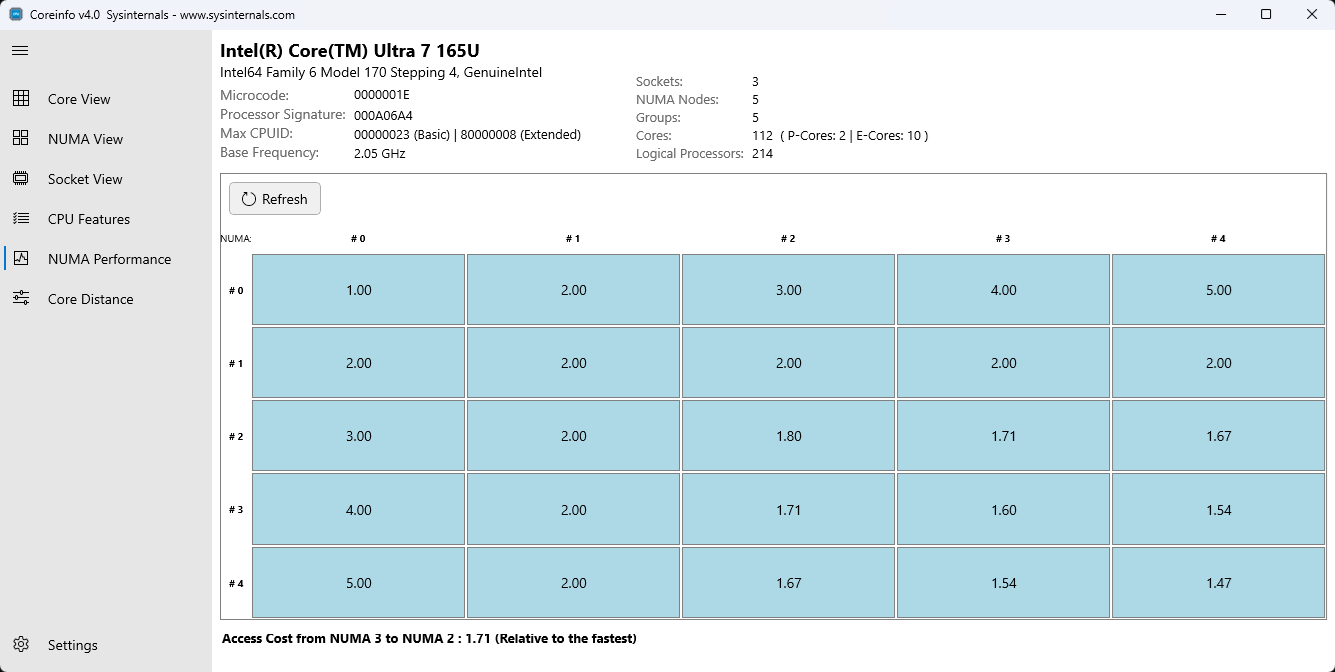

5. Мониторинг производительности NUMA

Представление производительности NUMA предоставляет визуализацию сетки, показывающую затраты на доступ к памяти между узлами NUMA, помогая выявлять узкие места производительности в системах NUMA.

Функции:

- Визуализация сетки: матрица, отображающая относительные затраты на доступ к памяти между узлами NUMA

- Интерактивная матрица: наведите указатель мыши на ячейки, чтобы просмотреть подробные сведения о производительности

- Обновления в реальном времени: данные производительности обновляются динамически при нажатии кнопки "Обновить"

- Отображение относительной стоимости: показывает относительную стоимость доступа к памяти из разных узлов NUMA

Отображаемые сведения:

- Матрица NxN, где N = число узлов NUMA

- Стоимость доступа к памяти из исходного узла NUMA (строка) в целевой узел NUMA (столбец)

- Числовые значения, показывающие относительные затраты на производительность

- Диагональные ячейки показывают локальный доступ к памяти (обычно самая низкая стоимость)

Сетка производительности NUMA, показывающая затраты на доступ к памяти

Сетка производительности NUMA, показывающая затраты на доступ к памяти

Общие сведения о сетке:

- Диагональные элементы: представляют доступ к локальной памяти (узел, обращающийся к собственной памяти) — как правило, самые низкие значения.

- Внедиагональные элементы: представляют доступ к удаленной памяти с более высокими относительными затратами

- Симметрия: матрица может не быть совершенно симметричной, так как затраты на доступ могут отличаться по направлению

Варианты использования:

- Определение узких мест производительности, связанных с NUMA

- Оптимизация стратегий выделения памяти

- Планирование процесса или закрепление потоков для систем NUMA

- Понимание штрафов за доступ к памяти между узлами

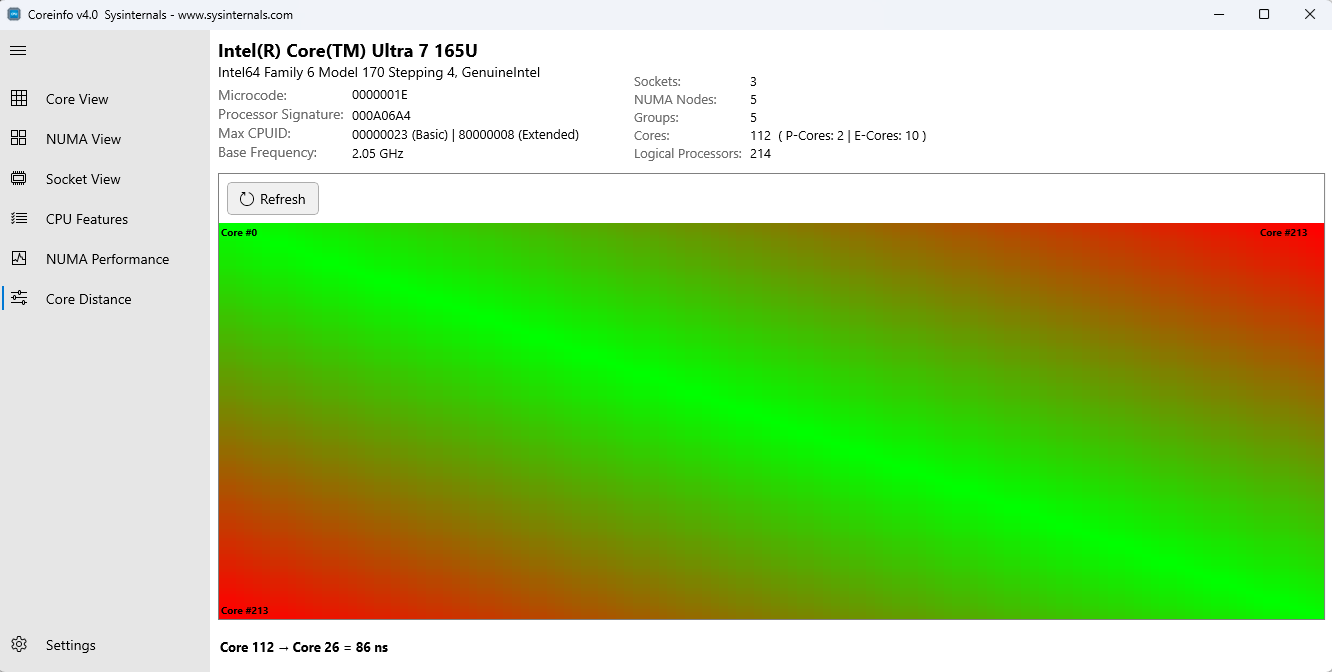

6. Вид ядрового расстояния

Представление "Расстояние между ядрами" отображает подробную тепловую карту затрат на обмен данными между отдельными ядрами ЦП, предоставляя информацию о задержке и эффективности связи между ядрами.

Функции:

-

Ярусная тепловая карта: матрица с цветовым кодированием, показывающая относительные расстояния между ядрами

- Зеленый или синий = низкая задержка (один и тот же основной кластер, общий кэш)

- Желтый или оранжевый = средняя задержка (один сокет, другой кластер)

- Red = высокая задержка (другой сокет или узел NUMA)

- Интерактивное исследование: наведите указатель мыши по сетке для просмотра подробной информации о расстоянии

- Детализированный анализ: Показывает связи ядро-ядро с максимальной детализацией

- Динамическое обновление: используйте кнопку "Обновить", чтобы динамически получать обновленные данные о расстоянии ядра

Отображаемые сведения:

- Матрица NxN, где N = число логических процессоров

- Относительное расстояние или задержка от исходного ядра (строки) к целевому ядру (столбец)

- Цветовая кодировка для быстрой идентификации основных связей

- Подробные показатели расстояния на панели данных

Тепловая карта " ", показывающая затраты на связь между ядрами

", показывающая затраты на связь между ядрами

Общие сведения о карте расстояния:

- Диагональные элементы: всегда ноль (основа самой себя)

- Низкое расстояние (зеленый):Ядра совместно используют кэш L2 или L3

- Среднее расстояние (желтый): ядра в одном сокете, но разные домены кэша

- Большое расстояние (красный): ядра на разных сокетах или узлах NUMA

Варианты использования:

- Оптимизация привязки потоков

- Общие сведения об областях когерентности кеша

- Определение оптимальных пар ядер для взаимодействующих потоков

- Анализ производительности многопоточных приложений

- Планирование стратегий закрепления ЦП для приложений с низкой задержкой

Интерактивные функции

Основной выбор и детали

При нажатии на ядро в любом представлении (Core, NUMA или Socket) отображаются подробные сведения в нижней панели сведений.

- Сведения о обработчике: логический номер процессора, маска и сходство

-

Иерархия кэша:

- Кэш данных L1 (размер, ассоциативность, размер строки)

- Кэш инструкций L1 (размер, ассоциативность, размер строки)

- Кэш L2 (размер, ассоциативность, размер строки)

- Кэш L3 (размер, ассоциативность, размер строки)

- Сведения о топологии: узлы NUMA, сокеты и назначения групп

- Тип ядра: P-Core, E-Core или стандартное назначение ядра

Функции поиска

Представление функций ЦП включает панель поиска, которая позволяет быстро находить определенные функции процессора:

- Щелкните значок поиска

- Введите имя или сокращенное имя функции

- Список автоматически фильтруется для отображения соответствующих функций

- Очистка поиска для восстановления полного списка

Переключатель карты кэша

В основном представлении переключайте между двумя режимами визуализации.

- Режим по умолчанию: отображение ядер в их логическом расположении

- Режим картирования кэша: перестраивает ядра для наглядного отображения связей общего доступа к кэшу

Навигация между видами

- Переключение между представлениями с помощью области навигации слева

- При просмотре конкретного узла или сокета NUMA, повторное нажатие на тот же вид возвращает к общему представлению.

- Текущее представление выделено в области навигации

Параметры и настройка

Доступ к параметрам с помощью параметра "Параметры" в меню навигации.

Параметры внешнего вида

Параметры темы:

- Свет: цветовая схема, оптимизированная для ярких сред

- Темная: темная цветовая схема для уменьшения нагрузки глаз

- Системное значение по умолчанию: автоматически соответствует предпочтениям темы Windows

Save To File (Сохранить в файл)

Экспорт основных данных топологии:

- Использование параметра Save To для дампа основных данных топологии в файл

- Формат выходных данных идентичен выходным данным средства командной строки

Общие сведения о топологии системы

Основные типы (гибридная архитектура)

Современные ЦП могут включать гибридные архитектуры с различными типами ядер:

- P-Cores (производительность): высокопроизводительные ядра, оптимизированные для однопоточных и требовательных рабочих нагрузок

- E-Cores (эффективность): энергоэффективные ядра, оптимизированные для фоновых задач и многопоточных рабочих нагрузок

Пользовательский интерфейс Coreinfo четко идентифицирует и дифференцирует эти основные типы во всех применимых представлениях.

Архитектура NUMA

Что такое NUMA? Доступ к памяти с неоднородным временем доступа (NUMA) — это архитектура памяти, где у каждого процессора имеется локальная память, к которой он может быстро получить доступ, и удаленная память, доступ к которой требует взаимодействия между процессорами.

Почему это важно:

- Локальный доступ к памяти значительно быстрее, чем удаленный доступ

- Производительность приложения может значительно зависеть от размещения NUMA.

- Основные сведения о топологии NUMA критически важны для высокопроизводительных вычислений

Использование пользовательского интерфейса Coreinfo для оптимизации NUMA:

- Используйте представление NUMA для понимания топологии системы NUMA

- Проверьте представление производительности NUMA , чтобы просмотреть затраты на доступ к памяти

- Оптимизация размещения потоков и процессов на основе назначений узлов NUMA

- Используйте Представление Основного Расстояния для понимания взаимодействия между ядрами в пределах и между узлами NUMA.

Иерархия кэша

Уровни кэша:

- Кэш L1: наименьший и быстрый, разделенный на кэши данных и инструкций

- Кэш L2: более крупный унифицированный кэш, обычно закрытый для каждого ядра

- Кэш L3: самый большой унифицированный кэш, часто общий для нескольких ядер

Использование сведений кэша:

- Понять, какие ядра разделяют ресурсы кэша

- Оптимизация локальности данных для ядер совместного использования кэша

- Использование режима карты кэша в режиме core для визуализации доменов кэша

Использование Coreinfo из командной строки

Для каждого ресурса отображается карта видимых ОС процессоров, соответствующих указанным ресурсам, с "*", представляющей применимые процессоры. Например, в 4-ядерной системе строка в выходных данных кэша с картой общих ядер 3 и 4.

Использование.

coreinfo [-c][-f][-g][-l][-n][-s][-m][-v]

| Параметр | Описание |

|---|---|

| -c | Сведения о ядрах дампа. |

| -f | Сведения о основных функциях дампа. |

| -g | Дамп сведений о группах. |

| -l | Дамп сведений о кэшах. |

| -n | Дамп сведений о узлах NUMA. |

| -s | Дамп сведений о сокетах. |

| -m | Стоимость доступа NUMA дампа. |

| -v | Дампа только функции, связанные с виртуализацией, включая поддержку перевода адресов второго уровня. (требуются права администратора в системах Intel). |

Все опции, кроме -v, выбраны по умолчанию.

Выходные данные Coreinfo:

Coreinfo v4.0 - Dump information on system CPU and memory topology

Copyright © 2008-2025 Mark Russinovich

Sysinternals - www.sysinternals.com

Intel(R) Core(TM) Ultra 7 165U

Intel64 Family 6 Model 170 Stepping 4, GenuineIntel

Microcode signature: 0000001E

Processor signature: 000A06A4

Maximum implemented CPUID leaves: 00000023 (Basic), 80000008 (Extended).

Maximum implemented address width: 48 bits (virtual), 46 bits (physical).

HTT * Hyperthreading enabled

CET * Supports Control Flow Enforcement Technology

Kernel CET - Kernel-mode CET Enabled

User CET * User-mode CET Allowed

X64 * Supports 64-bit mode

SMX - Supports Intel trusted execution

SKINIT - Supports AMD SKINIT

SGX - Supports Intel SGX

NX * Supports no-execute page protection

SMEP * Supports Supervisor Mode Execution Prevention

SMAP * Supports Supervisor Mode Access Prevention

PAGE1GB * Supports 1 GB large pages

PAE * Supports > 32-bit physical addresses

PAT * Supports Page Attribute Table

PSE * Supports 4 MB pages

PSE36 * Supports > 32-bit address 4 MB pages

PGE * Supports global bit in page tables

SS * Supports bus snooping for cache operations

VME * Supports Virtual-8086 mode

RDWRFSGSBASE * Supports direct GS/FS base access

FPU * Implements i387 floating point instructions

MMX * Supports MMX instruction set

MMXEXT - Implements AMD MMX extensions

3DNOW - Supports 3DNow! instructions

3DNOWEXT - Supports 3DNow! extension instructions

SSE * Supports Streaming SIMD Extensions

SSE2 * Supports Streaming SIMD Extensions 2

SSE3 * Supports Streaming SIMD Extensions 3

SSSE3 * Supports Supplemental SIMD Extensions 3

SSE4a - Supports Streaming SIMDR Extensions 4a

SSE4.1 * Supports Streaming SIMD Extensions 4.1

SSE4.2 * Supports Streaming SIMD Extensions 4.2

AES * Supports AES extensions

AVX * Supports AVX instruction extensions

AVX2 * Supports AVX2 instruction extensions

AVX-512-F - Supports AVX-512 Foundation instructions

AVX-512-DQ - Supports AVX-512 double and quadword instructions

AVX-512-IFAMA - Supports AVX-512 integer Fused multiply-add instructions

AVX-512-PF - Supports AVX-512 prefetch instructions

AVX-512-ER - Supports AVX-512 exponential and reciprocal instructions

AVX-512-CD - Supports AVX-512 conflict detection instructions

AVX-512-BW - Supports AVX-512 byte and word instructions

AVX-512-VL - Supports AVX-512 vector length instructions

FMA * Supports FMA extensions using YMM state

MSR * Implements RDMSR/WRMSR instructions

MTRR * Supports Memory Type Range Registers

XSAVE * Supports XSAVE/XRSTOR instructions

OSXSAVE * Supports XSETBV/XGETBV instructions

RDRAND * Supports RDRAND instruction

RDSEED * Supports RDSEED instruction

CMOV * Supports CMOVcc instruction

CLFSH * Supports CLFLUSH instruction

CX8 * Supports compare and exchange 8-byte instructions

CX16 * Supports CMPXCHG16B instruction

BMI1 * Supports bit manipulation extensions 1

BMI2 * Supports bit manipulation extensions 2

ADX * Supports ADCX/ADOX instructions

DCA - Supports prefetch from memory-mapped device

F16C * Supports half-precision instruction

FXSR * Supports FXSAVE/FXSTOR instructions

FFXSR - Supports optimized FXSAVE/FSRSTOR instruction

MONITOR * Supports MONITOR and MWAIT instructions

MOVBE * Supports MOVBE instruction

ERMSB * Supports Enhanced REP MOVSB/STOSB

PCLMULDQ * Supports PCLMULDQ instruction

POPCNT * Supports POPCNT instruction

LZCNT * Supports LZCNT instruction

SEP * Supports fast system call instructions

LAHF-SAHF * Supports LAHF/SAHF instructions in 64-bit mode

HLE - Supports Hardware Lock Elision instructions

RTM - Supports Restricted Transactional Memory instructions

DE * Supports I/O breakpoints including CR4.DE

DTES64 - Can write history of 64-bit branch addresses

DS - Implements memory-resident debug buffer

DS-CPL - Supports Debug Store feature with CPL

PCID * Supports PCIDs and settable CR4.PCIDE

INVPCID * Supports INVPCID instruction

PDCM * Supports Performance Capabilities MSR

RDTSCP * Supports RDTSCP instruction

TSC * Supports RDTSC instruction

TSC-DEADLINE * Local APIC supports one-shot deadline timer

TSC-INVARIANT * TSC runs at constant rate

xTPR * Supports disabling task priority messages

EIST * Supports Enhanced Intel Speedstep

ACPI * Implements MSR for power management

TM * Implements thermal monitor circuitry

TM2 * Implements Thermal Monitor 2 control

APIC * Implements software-accessible local APIC

x2APIC * Supports x2APIC

CNXT-ID - L1 data cache mode adaptive or BIOS

MCE * Supports Machine Check, INT18 and CR4.MCE

MCA * Implements Machine Check Architecture

PBE * Supports use of FERR#/PBE# pin

PSN - Implements 96-bit processor serial number

HTT * Hyperthreading

PREFETCHW * PrefetchW instruction support

HYPERVISOR * Hypervisor is present

VMX - Supports Intel hardware-assisted virtualization

EPT - Supports Intel extended page tables (SLAT)

URG - Supports Intel unrestricted guest

Logical to Physical Processor Map:

**------------ Physical Processor 0 (Hyperthreaded)

--*----------- Physical Processor 1

---*---------- Physical Processor 2

----*--------- Physical Processor 3

-----*-------- Physical Processor 4

------*------- Physical Processor 5

-------*------ Physical Processor 6

--------*----- Physical Processor 7

---------*---- Physical Processor 8

----------**-- Physical Processor 9 (Hyperthreaded)

------------*- Physical Processor 10

-------------* Physical Processor 11

Logical Processor to Socket Map:

************** Socket 0

Logical Processor to NUMA Node Map:

************** NUMA Node 0

No NUMA nodes.

Logical Processor to Cache Map:

**------------ Data Cache 0, Level 1, 48 KB, Assoc 12, LineSize 64

**------------ Instruction Cache 0, Level 1, 64 KB, Assoc 16, LineSize 64

**------------ Unified Cache 0, Level 2, 2 MB, Assoc 16, LineSize 64

************-- Unified Cache 1, Level 3, 12 MB, Assoc 12, LineSize 64

--*----------- Data Cache 1, Level 1, 32 KB, Assoc 8, LineSize 64

--*----------- Instruction Cache 1, Level 1, 64 KB, Assoc 8, LineSize 64

--****-------- Unified Cache 2, Level 2, 2 MB, Assoc 16, LineSize 64

---*---------- Data Cache 2, Level 1, 32 KB, Assoc 8, LineSize 64

---*---------- Instruction Cache 2, Level 1, 64 KB, Assoc 8, LineSize 64

----*--------- Data Cache 3, Level 1, 32 KB, Assoc 8, LineSize 64

----*--------- Instruction Cache 3, Level 1, 64 KB, Assoc 8, LineSize 64

-----*-------- Data Cache 4, Level 1, 32 KB, Assoc 8, LineSize 64

-----*-------- Instruction Cache 4, Level 1, 64 KB, Assoc 8, LineSize 64

------*------- Data Cache 5, Level 1, 32 KB, Assoc 8, LineSize 64

------*------- Instruction Cache 5, Level 1, 64 KB, Assoc 8, LineSize 64

------****---- Unified Cache 3, Level 2, 2 MB, Assoc 16, LineSize 64

-------*------ Data Cache 6, Level 1, 32 KB, Assoc 8, LineSize 64

-------*------ Instruction Cache 6, Level 1, 64 KB, Assoc 8, LineSize 64

--------*----- Data Cache 7, Level 1, 32 KB, Assoc 8, LineSize 64

--------*----- Instruction Cache 7, Level 1, 64 KB, Assoc 8, LineSize 64

---------*---- Data Cache 8, Level 1, 32 KB, Assoc 8, LineSize 64

---------*---- Instruction Cache 8, Level 1, 64 KB, Assoc 8, LineSize 64

----------**-- Data Cache 9, Level 1, 48 KB, Assoc 12, LineSize 64

----------**-- Instruction Cache 9, Level 1, 64 KB, Assoc 16, LineSize 64

----------**-- Unified Cache 4, Level 2, 2 MB, Assoc 16, LineSize 64

------------*- Data Cache 10, Level 1, 32 KB, Assoc 8, LineSize 64

------------*- Instruction Cache 10, Level 1, 64 KB, Assoc 8, LineSize 64

------------** Unified Cache 5, Level 2, 2 MB, Assoc 16, LineSize 64

-------------* Data Cache 11, Level 1, 32 KB, Assoc 8, LineSize 64

-------------* Instruction Cache 11, Level 1, 64 KB, Assoc 8, LineSize 64

Logical Processor to Group Map:

************** Group 0

Coreinfo(3 МБ)Запустите сейчас из Sysinternals Live.

Coreinfo(3 МБ)Запустите сейчас из Sysinternals Live.

Выполняется:

- Клиент: Windows 11 и более поздние версии.

- Сервер: Windows Server 2016 и выше.