Not

Bu sayfaya erişim yetkilendirme gerektiriyor. Oturum açmayı veya dizinleri değiştirmeyi deneyebilirsiniz.

Bu sayfaya erişim yetkilendirme gerektiriyor. Dizinleri değiştirmeyi deneyebilirsiniz.

Tarafından Mark Russinovich

Yayımlanma Tarihi: 16 Aralık 2025

Coreinfo(3 MB)

Coreinfo(3 MB)

Giriş

Coreinfo, mantıksal işlemciler ile üzerinde bulundukları fiziksel işlemci, NUMA düğümü ve yuva arasındaki eşlemeyi ve ayrıca önbelleğin her mantıksal işlemciye atandığını gösteren bir yardımcı programdır. Ayrıntılı CPU topolojisi bilgilerini doğrudan işletim sisteminden almak için alt düzey Windows API'lerini (kullanıcı modu ve çekirdek modu) kullanır. Komut satırı sürümü, eşlemenin bir mantıksal işlemciye gösterimini yıldız işaretiyle (örneğin'*) oluşturur. Kullanıcı arabirimi, mantıksal ve fiziksel çekirdekler, NUMA düğümleri, yuvalar, önbellek hiyerarşileri ve gerçek zamanlı performans ölçümleri gibi sisteminizin CPU topolojisinin farklı yönlerini keşfetmek için birden çok özel görünüm sağlar. Coreinfo, sistemin işlemci ve önbellek topolojisi hakkında içgörü elde etmek için kullanışlıdır.

Yükleme

Arşivi bir dizine ayıklayın ve ardından mimariye bağlı olarak bu dizinden Coreinfo / Coreinfo64 veya Coreinfo64ayazarak Coreinfo'yı çalıştırın. Kullanıcı arabirimi sürümü için başlatınCoreInfoEx / CoreInfoEx64 / CoreInfoEx64a.

Not: Bazı özellikler, tam bilgi almak için yönetici ayrıcalıkları gerektirebilir.

Kullanıcı Arabirimine Genel Bakış

Coreinfo kullanıcı arabirimi birkaç temel bileşenden oluşur:

Ana Pencere Düzeni

- Üst Panel: CPU adı, mimari ve çekirdek sayıları dahil olmak üzere sistem bilgilerini görüntüler

- Gezinti Bölmesi (Sol): Farklı görünümlere hızlı erişim sağlar

- İçerik Alanı (Orta): Seçili görünümün verilerini ve görselleştirmelerini gösterir

- Ayrıntılar Bölmesi (Alt): Çekirdekler veya hücreler seçildiğinde ayrıntılı bilgileri görüntüler

- Ayarlar: Görünüm seçeneklerine ve uygulama tercihlerine erişme

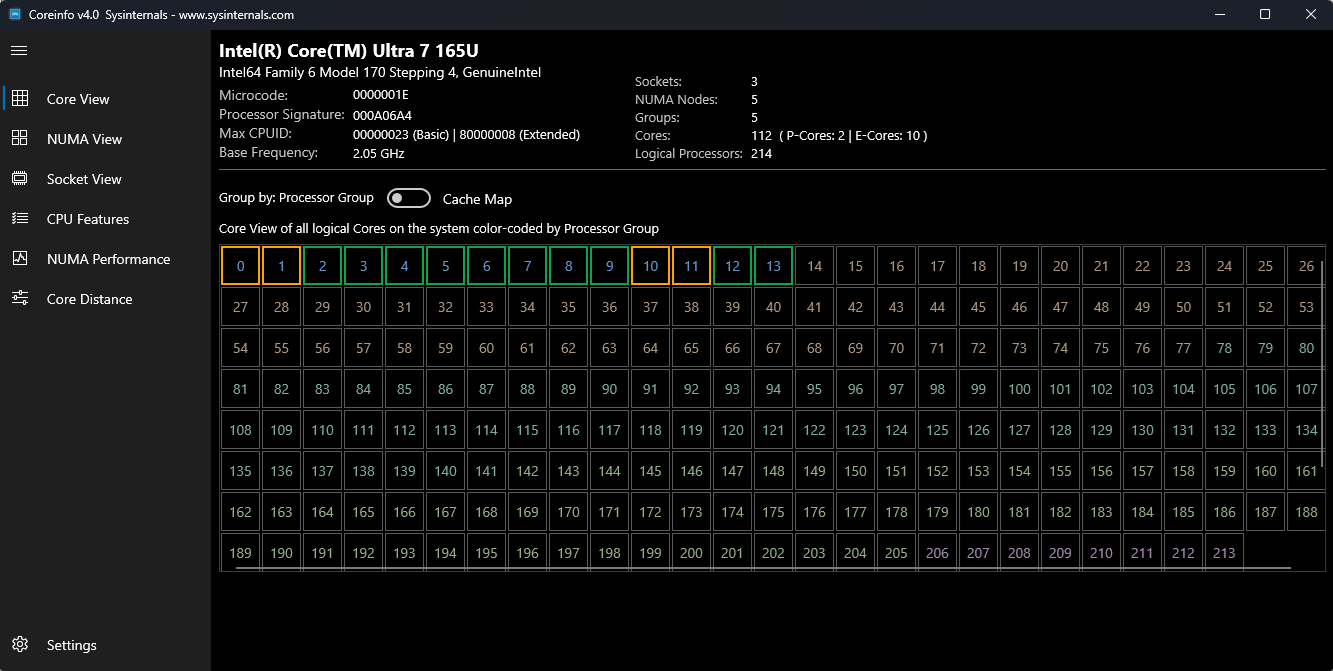

Tam kullanıcı arabirimi düzenini gösteren ana pencere, koyu mod

Tam kullanıcı arabirimi düzenini gösteren ana pencere, koyu mod

Navigasyon Görünümleri

Sol gezinti bölmesi altı özelleştirilmiş görünüme erişim sağlar:

1. Çekirdek Görünümü

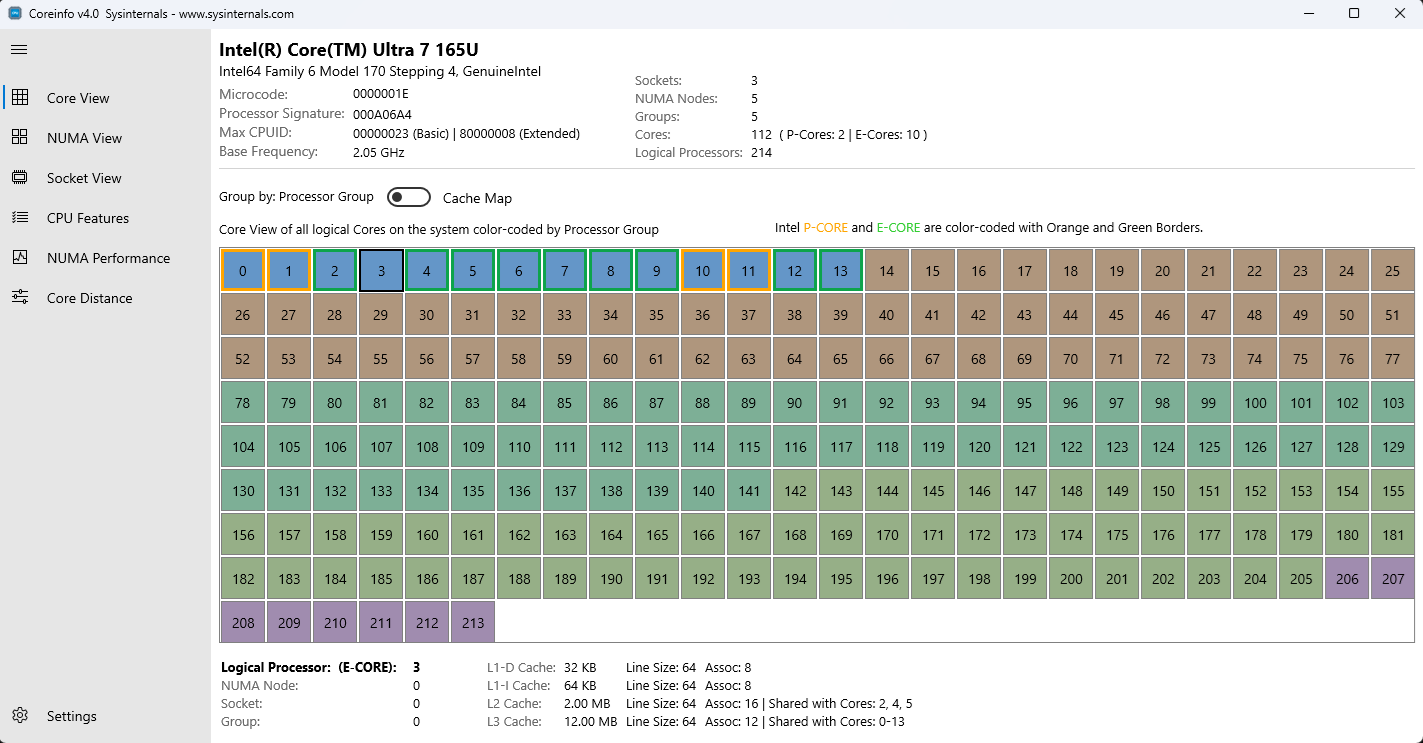

Çekirdek Görünümü, sisteminizdeki tüm mantıksal işlemcileri bir kılavuz düzeninde görüntüler ve mantıksal çekirdeklerle fiziksel kaynakları arasındaki ilişkiyi gösterir.

Özellikler:

- Kılavuz Düzeni: Her hücre bir mantıksal işlemciyi temsil eder

-

Çekirdek Tür Göstergeleri:

- P Çekirdekleri (Performans çekirdekleri) - farklı renklerde

- E-Çekirdekler (Verimlilik çekirdekleri) - farklı renkte

- Standart çekirdekler - varsayılan renklendirme

- Önbellek Eşleme geçiş düğmesi: Varsayılan görünüm ile önbellek hiyerarşisi görünümü arasında geçiş yapma

- Etkileşimli Seçim: Alt bölmede ayrıntılı bilgileri görüntülemek için herhangi bir çekirdeğe tıklayın

Görüntülenen Bilgiler:

- Mantıksal işlemci numarası

- Çekirdek türü (varsa P-Core/E-Core)

- İlişkili önbellek düzeyleri (L1, L2, L3)

- NUMA düğüm ataması

- Soket ataması

- Grup ataması

Kılavuz düzeninde mantıksal işlemcileri gösterir

Kılavuz düzeninde mantıksal işlemcileri gösterir

Detaylar Bölmesi Bilgisi (bir çekirdek seçildiğinde):

- İşlemci maskesi ve bağlılık

- Önbellek hiyerarşisi (Veri Önbelleği, Yönerge Önbelleği, Birleşik Önbellek)

- Önbellek boyutları ve ilişkilendirme

- Önbellek satırı boyutları

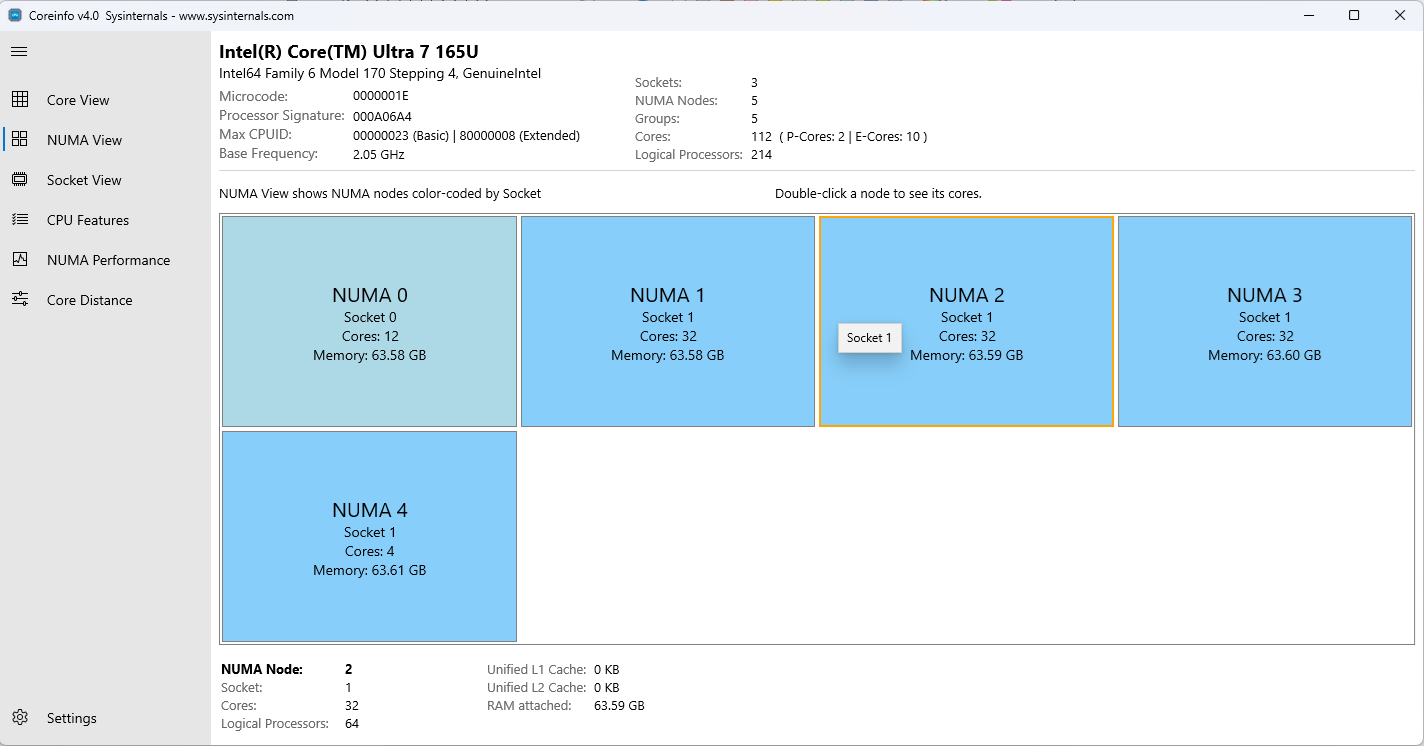

2. NUMA Görünümü

NUMA (Tekdüzen Olmayan Bellek Erişimi) Görünümü, çekirdekleri NUMA düğüm atamalarına göre düzenleyerek bellek yerelliğini ve erişim desenlerini anlamayı kolaylaştırır.

Özellikler:

- Düğüm Tabanlı Organizasyon: NUMA düğümlerine göre gruplandırılmış çekirdekler

- Fiziksel ve Mantıksal Çekirdekler: Her düğüm için her iki sayıyı gösterir

- Bellek Bilgileri: NUMA düğümü başına kullanılabilir belleği görüntüler

-

Etkileşimli Gezinti:

- Bir NUMA düğümüne tek tıklayarak ayrıntılarını alttaki ayrıntılar bölmesinde görüntüleyin

- Seçili NUMA düğümündeki tüm çekirdekleri gösteren Çekirdek Görünümü'ne gitmek için bir NUMA düğümüne çift tıklayın

- Hiyerarşik Görüntü: NUMA düğümleri ile çekirdekler arasındaki ilişkiyi gösterir

Görüntülenen Bilgiler:

- NUMA düğümlerinin sayısı

- NUMA düğümü başına çekirdek sayısı (fiziksel ve mantıksal)

- Düğüm başına bellek kapasitesi

- Düğümler arasında çekirdek dağıtımı

- Verimlilik çekirdek sayısı (varsa)

Çekirdekleri NUMA düğümlerine göre düzenlenmiş şekilde gösteren NUMA Görünümü

Çekirdekleri NUMA düğümlerine göre düzenlenmiş şekilde gösteren NUMA Görünümü

Kullanım Örnekleri:

- Bellek erişim desenlerini iyileştirme

- NUMA kullanan uygulama performansını anlama

- En iyi performans için iş parçacığı/süreç yerleşimini planlama

3. Yuva Görünümü

Yuva Görünümü, çekirdekleri fiziksel CPU yuvalarına göre düzenlenmiş olarak görüntüler; çok yuvalı sistemleri ve yuva düzeyinde kaynak dağıtımını anlamak için kullanışlıdır.

Özellikler:

- Yuvaya Dayalı Gruplandırma: Fiziksel sokete göre düzenlenmiş çekirdekler

- Yuva Bilgileri: Yuva sayısı ve çekirdek dağıtımı

-

Etkileşimli Gezinti:

- Bir yuvaya tek tıklayarak ayrıntılarını alttaki ayrıntılar bölmesinde görüntüleyin

- Seçili yuvadaki tüm çekirdekleri gösteren Çekirdek Görünümü'ne gitmek için bir yuvaya çift tıklayın

- Önbellek Paylaşımı: Hangi çekirdeklerin yuva düzeyinde önbellekleri paylaştığını görselleştirme

Görüntülenen Bilgiler:

- Fiziksel yuva sayısı

- Yuva başına çekirdek sayısı (fiziksel ve mantıksal)

- Yuva düzeyinde önbellek bilgileri

- Yuva başına NUMA düğümleri

CPU yuvalarına göre düzenlenmiş çekirdekleri gösteren Yuva Görünümü

CPU yuvalarına göre düzenlenmiş çekirdekleri gösteren Yuva Görünümü

Kullanım Örnekleri:

- Çok yuvalı sistem analizi

- Soketler arası iletişim maliyetlerini anlama

- Çok yuvalı sunucularda iş yükü dağıtımlarını planlama

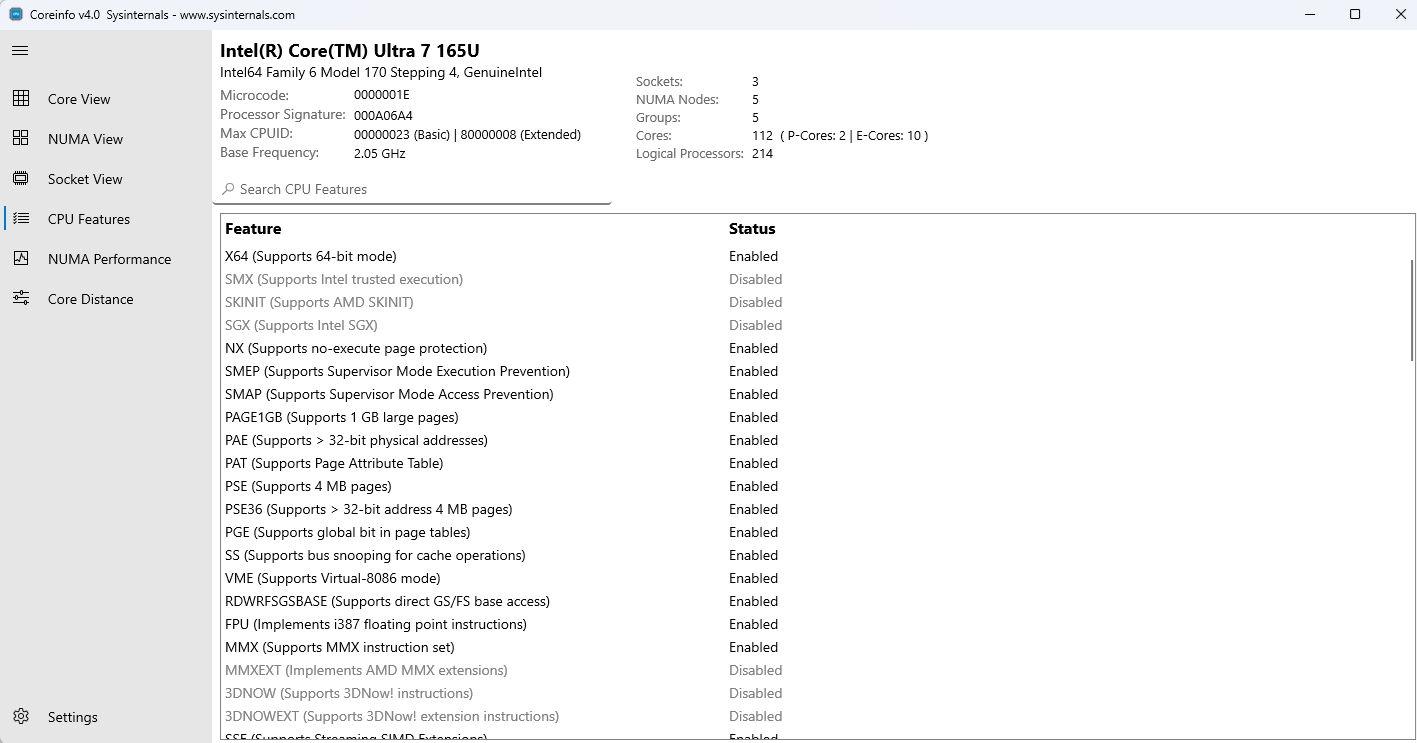

4. CPU Özellikleri Görünümü

CPU Özellikleri Görünümü işlemci özelliklerinin, yönerge kümesi uzantılarının ve CPU'nuzun desteklediği donanım özelliklerinin kapsamlı bir listesini görüntüler.

Özellikler:

- Aranabilir Liste: Arama çubuğunu kullanarak belirli CPU özelliklerini hızla bulma

-

Durum Göstergeleri: Renk kodlama kullanarak desteklenen/desteklenmeyen özelliklerin görsel göstergesini temizleyin

- Desteklenen özellikler normal renkte görüntülenir

- Desteklenmeyen/devre dışı bırakılan özellikler gri gösteriliyor

-

Özellik Kategorileri:

- Sanallaştırma (VMX, SVM, HYPERVISOR)

- 64 bit destek (EM64T, NX)

- Yönerge Kümeleri (SSE, AVX, AES vb.)

- Güç Yönetimi (EIST, ACPI, Termal)

- Güvenlik özellikleri (SMX, SKINIT)

- Bellek özellikleri (PAE, PAT, PSE)

- Hata ayıklama ve izleme özellikleri

Görüntülenen Bilgiler:

- Özellik kısaltması

- Özellik durumu (desteklenir/desteklenmez)

- Tam özellik açıklaması (ayrıntılar bölmesinde)

CPU özelliklerinin listesini gösteren CPU Özellikleri Görünümü

CPU özelliklerinin listesini gösteren CPU Özellikleri Görünümü

Not: Bazı sanallaştırma özellikleri (VMX, SVM gibi) bir hiper yönetici etkin olduğunda veya bir sanal makine içinden çalıştırıldığında yanlış şekilde kullanılamaz olarak rapor edilebilir. Coreinfo, kesin sonuçlar elde etmek için hipervizör çalışmayan bir sistemde yürütülmelidir.

Kullanım Örnekleri:

- Uygulamaları dağıtmadan önce yönerge kümesi kullanılabilirliğini doğrulama

- Sanallaştırma desteğini denetleme

- İşlemci oluşturma ve özelliklerini anlama

- Eksik CPU özellikleriyle ilgili performans sorunlarını ayıklama

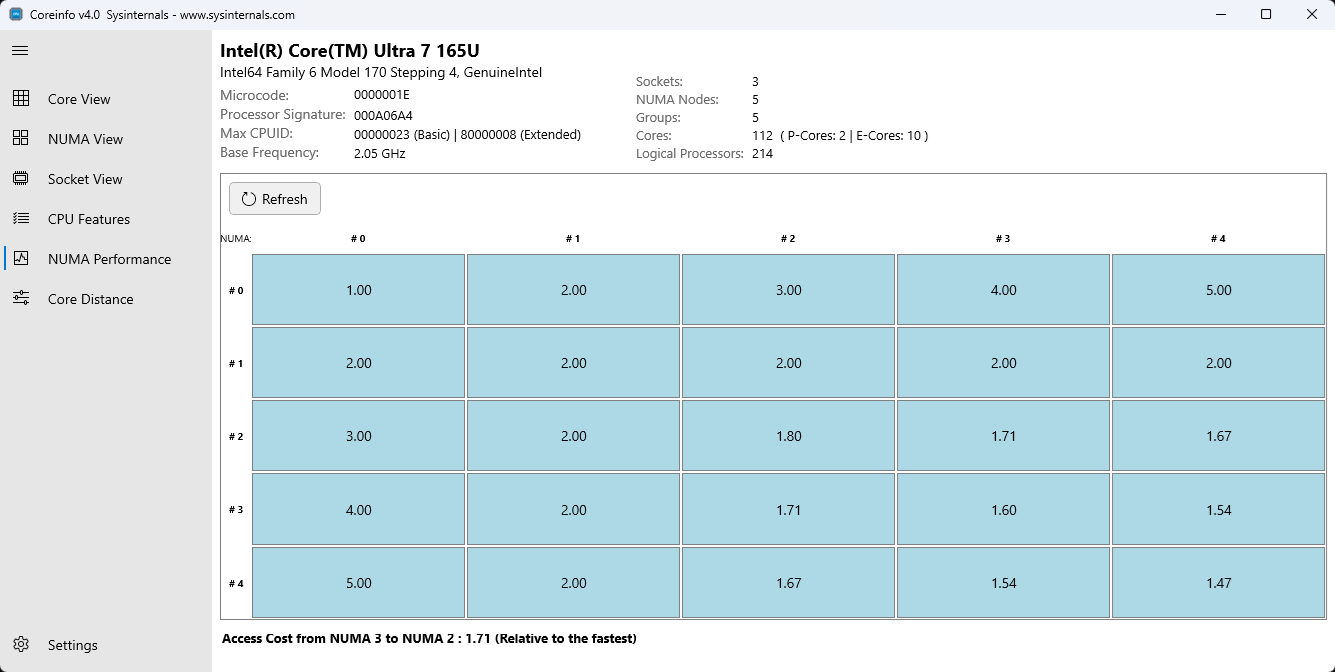

5. NUMA Performans Görünümü

NUMA Performans Görünümü, NUMA düğümleri arasındaki bellek erişim maliyetlerini gösteren bir kılavuz görselleştirmesi sağlayarak NUMA sistemlerinde performans sorunlarının belirlenmesine yardımcı olur.

Özellikler:

- Kılavuz Görselleştirmesi: NUMA düğümleri arasındaki göreli bellek erişim maliyetlerini gösteren matris

- Etkileşimli Matris: Ayrıntılı performans bilgilerini görmek için hücrelerin üzerine gelin

- Real-Time Güncelleştirmeleri: Yenile düğmesini seçerek performans verileri dinamik olarak güncelleştirilir

- Göreli Maliyet Görünümü: Farklı NUMA düğümlerinden belleğe erişmenin göreli maliyetini gösterir

Görüntülenen Bilgiler:

- N = NUMA düğümlerinin sayısı olan NxN matrisi

- Kaynak NUMA düğümünden (satır) hedef NUMA düğümüne (sütun) bellek erişim maliyeti

- Göreli performans maliyetlerini gösteren sayısal değerler

- Çapraz hücreler yerel bellek erişimini gösterir (genellikle en düşük maliyet)

Bellek erişim maliyetlerini gösteren NUMA Performans ızgarası

Bellek erişim maliyetlerini gösteren NUMA Performans ızgarası

Kılavuzu Anlama:

- Çapraz öğeler: Yerel bellek erişimini temsil eder (kendi belleğine erişen düğüm) - genellikle en düşük değerler

- Çapraz olmayan öğeler: Daha yüksek göreli maliyetlerle uzak bellek erişimini temsil eder

- Simetri: Matris mükemmel simetrik olmayabilir, erişim maliyetleri yöne göre farklılık gösterebilir

Kullanım Örnekleri:

- NUMA ile ilgili performans sorunlarını tanımlama

- Bellek ayırma stratejilerini iyileştirme

- NUMA sistemleri için işlem/iş parçacığı sabitleme planlaması

- Düğümler arası bellek erişim cezalarını anlama

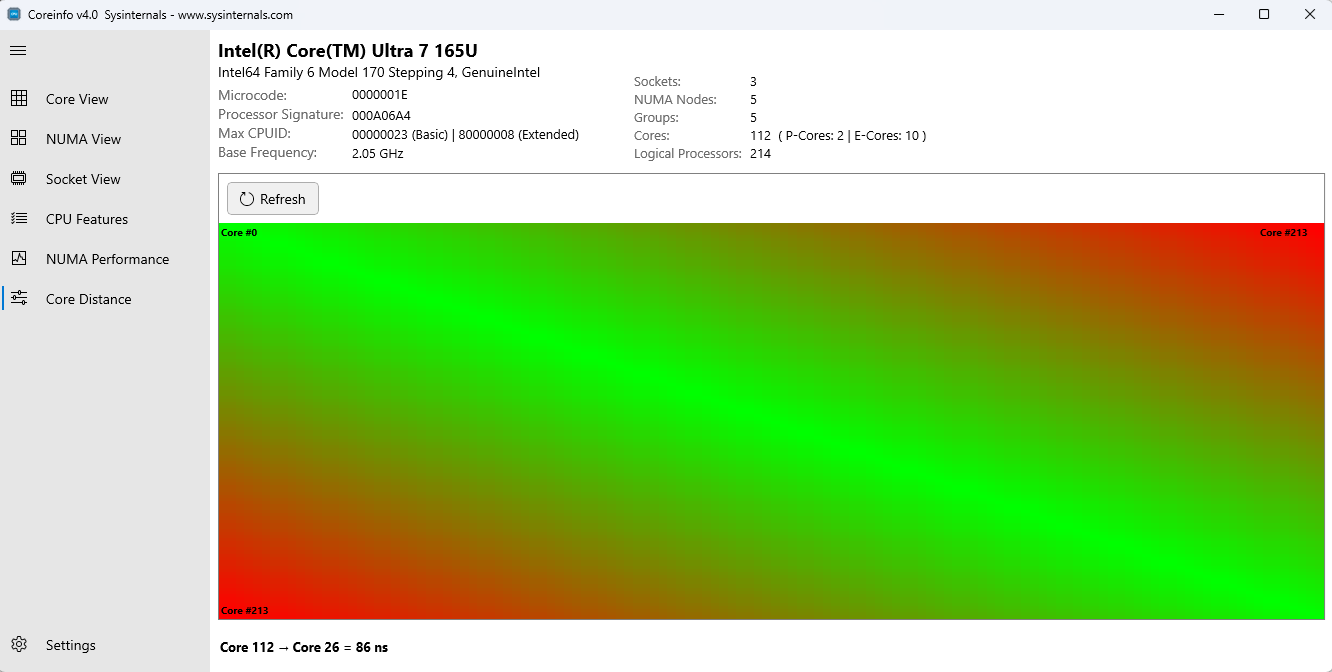

6. Çekirdek Uzaklık Görünümü

Çekirdek Uzaklık Görünümü, tek tek CPU çekirdekleri arasındaki iletişim maliyetlerinin ayrıntılı bir ısı haritasını görüntüleyerek çekirdek-çekirdek gecikme süresi ve iletişim verimliliği hakkında içgörüler sağlar.

Özellikler:

-

Core-Level Isı Haritası: Çekirdekler arasındaki göreli uzaklıkları gösteren renk kodlu matris

- Yeşil/Mavi = Düşük gecikme süresi (aynı çekirdek küme, paylaşılan önbellek)

- Sarı/Turuncu = Orta gecikme süresi (aynı yuva, farklı küme)

- Kırmızı = Yüksek gecikme süresi (farklı yuva veya NUMA düğümü)

- Etkileşimli Keşif: Ayrıntılı uzaklık bilgilerini görüntülemek için kılavuz tuvalinin üzerine gelin

- Ayrıntılı Analiz: Çekirdek-çekirdek ilişkilerini en ince ayrıntı düzeyinde gösterir

- Dinamik Yenileme: Güncelleştirilmiş çekirdek uzaklık verilerini dinamik olarak almak için Yenile düğmesini kullanın

Görüntülenen Bilgiler:

- N = mantıksal işlemci sayısı olan NxN matrisi

- Kaynak çekirdekten (satır) hedef çekirdeğe (sütun) göreli uzaklık/gecikme süresi

- Çekirdek ilişkilerin hızlı görsel tanımlaması için renk kodlama

- Ayrıntılar bölmesindeki ayrıntılı uzaklık ölçümleri

Çekirdek Uzaklık ısı haritası çekirdek-çekirdek iletişim maliyetlerini gösterir

Çekirdek Uzaklık ısı haritası çekirdek-çekirdek iletişim maliyetlerini gösterir

Uzaklık Haritasını Anlama:

- Çapraz elemanlar: Her zaman sıfır (çekirdek ile kendisi)

- Düşük mesafe (yeşil): Çekirdekler L2 veya L3 önbelleğini paylaşır

- Orta uzaklık (sarı): Aynı yuvadaki çekirdekler ancak farklı önbellek etki alanları

- Yüksek uzaklık (kırmızı): Farklı yuvalardaki veya NUMA düğümlerindeki çekirdekler

Kullanım Örnekleri:

- İş parçacığı bağımlılığı optimizasyonu

- Önbellek tutarlılığı etki alanlarını anlama

- İş parçacıklarını iletmek için en uygun çekirdek çiftlerini belirleme

- Çoklu iş parçacıklı uygulama performansının analiz edilmesi

- Düşük gecikmeli uygulamalar için CPU sabitleme stratejilerini planlama

Etkileşimli Özellikler

Çekirdek Seçimi ve Ayrıntılar

Herhangi bir görünümde (Çekirdek, NUMA veya Soket) bir çekirdeğe tıkladığınızda, ayrıntılı bilgiler alt konumdaki ayrıntı panelinde görüntülenir.

- İşlemci Bilgileri: Mantıksal işlemci numarası, maske ve ilişki

-

Önbellek Hiyerarşisi:

- L1 Veri Önbelleği (boyut, ilişkilendirme, satır boyutu)

- L1 Yönerge Önbelleği (boyut, ilişkilendirme, satır boyutu)

- L2 Önbelleği (boyut, ilişkilendirme, satır boyutu)

- L3 Önbelleği (boyut, ilişkilendirme, satır boyutu)

- Topoloji Bilgileri: NUMA düğümü, yuva ve grup atamaları

- Çekirdek Türü: P-Core, E-Core veya standart çekirdek ataması

Arama İşlevselliği

CPU Özellikleri görünümü, belirli işlemci özelliklerini hızla bulmanıza olanak tanıyan bir arama çubuğu içerir:

- Arama simgesine tıklayın

- Özellik adını veya kısaltmasını yazın

- Liste, eşleşen özellikleri gösterecek şekilde otomatik olarak filtrelenir

- Tam listeyi geri yüklemek için aramayı temizleyin

Önbellek Haritası Anahtarı

Çekirdek Görünüm'de iki görselleştirme modu arasında geçiş yapın:

- Varsayılan Mod: Çekirdekleri mantıksal düzenlerinde gösterir

- Önbellek Eşleme Modu: Önbellek paylaşımı ilişkilerini görselleştirmek için çekirdekleri yeniden düzenler

Görünümler Arasında Gezinti

- Görünümler arasında geçiş yapmak için sol gezinti bölmesini kullanma

- Belirli bir NUMA düğümünü veya yuvasını görüntülerken, aynı görünüme yeniden tıklandığında genel görünüme geri döner

- Geçerli görünüm gezinti bölmesinde vurgulanmış

Ayarlar ve Özelleştirme

Gezinti menüsündeki Ayarlar seçeneği aracılığıyla ayarlara erişin.

Görünüm Ayarları

Tema Seçenekleri:

- Açık: Parlak ortamlar için iyileştirilmiş açık renk düzeni

- Koyu: Göz yorgunluğunu azaltmak için koyu renk düzeni

- Sistem Varsayılanı: Windows tema tercihinizle otomatik olarak eşleşir

Dosyaya Kaydet

Çekirdek Topoloji Verilerini Dışarı Aktar:

- Çekirdek topoloji verilerini bir dosyaya döküm etmek için Kaydet seçeneğini kullanın

- Çıkış biçimi, komut satırı aracı çıkışıyla aynıdır

Sistem Topolojinizi Anlama

Çekirdek Türleri (Karma Mimari)

Modern CPU'lar farklı çekirdek türlerine sahip hibrit mimariler içerebilir:

- P Çekirdekleri (Performans): Tek iş parçacıklı ve zorlu iş yükleri için iyileştirilmiş yüksek performanslı çekirdekler

- E-Çekirdekler (Verimlilik): Arka plan görevleri ve çok iş parçacıklı iş yükleri için optimize edilmiş enerji açısından verimli çekirdekler

Coreinfo kullanıcı arabirimi bu temel türleri tüm geçerli görünümlerde net bir şekilde tanımlar ve ayırt eder.

NUMA Mimarisi

NUMA nedir? Tekdüzen Olmayan Bellek Erişimi (NUMA), her işlemcinin hızla erişebileceği yerel belleğe ve işlemciler arası iletişim gerektiren uzak belleğe sahip olduğu bir bellek tasarımıdır.

Neden önemli:

- Yerel bellek erişimi uzaktan erişimden önemli ölçüde daha hızlıdır

- Uygulama performansı NUMA yerleştirmeden önemli ölçüde etkilenebilir

- NUMA topolojisini anlamak yüksek performanslı bilgi işlem için kritik öneme sahiptir

NUMA İyileştirmesi için Coreinfo kullanıcı arabirimini kullanma:

- Sisteminizin NUMA topolojisini anlamak için NUMA Görünümünü kullanma

- Bellek erişim maliyetlerini görmek için NUMA Performans Görünümü'nü denetleyin

- NUMA düğüm atamalarına göre iş parçacığı/işlem yerleşimini iyileştirme

- NUMA düğümleri içinde ve genelinde çekirdek-çekirdek arasındaki iletişimi anlamak için Çekirdek Uzaklık Görünümü'nü kullanma

Önbellek Hiyerarşisi

Önbellek Düzeyleri:

- L1 Önbelleği: En küçük ve en hızlı, veri ve yönerge önbelleklerine bölünür

- L2 Önbelleği: Genellikle her çekirdek için özel olan daha büyük birleşik önbellek

- L3 Önbelleği: Çoğu zaman birden çok çekirdek arasında paylaşılan en büyük birleşik önbellek

Önbellek Bilgilerini Kullanma:

- Hangi çekirdeklerin önbellek kaynaklarını paylaştığını anlama

- Önbellek paylaşım çekirdekleri için veri yerelliğini iyileştirme

- Önbellek etki alanlarını görselleştirmek için Çekirdek Görünüm'de Önbellek Eşleme modunu kullanma

Komut satırından Coreinfo kullanma

Her kaynak için, geçerli işlemcileri temsil eden '*' ile belirtilen kaynaklara karşılık gelen işletim sistemi görünür işlemcilerinin bir haritasını gösterir. Örneğin, 4 çekirdekli bir sistemde, önbellek çıkışında 3 ve 4 çekirdekleri tarafından paylaşılan bir harita içeren bir satır.

Kullanım:

coreinfo [-c][-f][-g][-l][-n][-s][-m][-v]

| Parametre | Açıklama |

|---|---|

| -c | Çekirdeklerle ilgili bilgi dökümü. |

| -f | Çekirdek özellik bilgilerini döküm edin. |

| -g | Gruplardaki bilgi dökümü. |

| -l | Önbelleklere bilgi dökümü. |

| -n | NUMA düğümlerinde bilgi dökümü. |

| -s | Yuvalara bilgi dökümü. |

| -m | NUMA erişim maliyetini döküm edin. |

| -v | İkinci düzey adres çevirisi desteği de dahil olmak üzere yalnızca sanallaştırmayla ilgili özelliklerin dökümünü alın. (Intel sistemlerinde yönetim hakları gerektirir). |

Dışındaki -v tüm seçenekler varsayılan olarak seçilidir.

Coreinfo Çıktısı:

Coreinfo v4.0 - Dump information on system CPU and memory topology

Copyright © 2008-2025 Mark Russinovich

Sysinternals - www.sysinternals.com

Intel(R) Core(TM) Ultra 7 165U

Intel64 Family 6 Model 170 Stepping 4, GenuineIntel

Microcode signature: 0000001E

Processor signature: 000A06A4

Maximum implemented CPUID leaves: 00000023 (Basic), 80000008 (Extended).

Maximum implemented address width: 48 bits (virtual), 46 bits (physical).

HTT * Hyperthreading enabled

CET * Supports Control Flow Enforcement Technology

Kernel CET - Kernel-mode CET Enabled

User CET * User-mode CET Allowed

X64 * Supports 64-bit mode

SMX - Supports Intel trusted execution

SKINIT - Supports AMD SKINIT

SGX - Supports Intel SGX

NX * Supports no-execute page protection

SMEP * Supports Supervisor Mode Execution Prevention

SMAP * Supports Supervisor Mode Access Prevention

PAGE1GB * Supports 1 GB large pages

PAE * Supports > 32-bit physical addresses

PAT * Supports Page Attribute Table

PSE * Supports 4 MB pages

PSE36 * Supports > 32-bit address 4 MB pages

PGE * Supports global bit in page tables

SS * Supports bus snooping for cache operations

VME * Supports Virtual-8086 mode

RDWRFSGSBASE * Supports direct GS/FS base access

FPU * Implements i387 floating point instructions

MMX * Supports MMX instruction set

MMXEXT - Implements AMD MMX extensions

3DNOW - Supports 3DNow! instructions

3DNOWEXT - Supports 3DNow! extension instructions

SSE * Supports Streaming SIMD Extensions

SSE2 * Supports Streaming SIMD Extensions 2

SSE3 * Supports Streaming SIMD Extensions 3

SSSE3 * Supports Supplemental SIMD Extensions 3

SSE4a - Supports Streaming SIMDR Extensions 4a

SSE4.1 * Supports Streaming SIMD Extensions 4.1

SSE4.2 * Supports Streaming SIMD Extensions 4.2

AES * Supports AES extensions

AVX * Supports AVX instruction extensions

AVX2 * Supports AVX2 instruction extensions

AVX-512-F - Supports AVX-512 Foundation instructions

AVX-512-DQ - Supports AVX-512 double and quadword instructions

AVX-512-IFAMA - Supports AVX-512 integer Fused multiply-add instructions

AVX-512-PF - Supports AVX-512 prefetch instructions

AVX-512-ER - Supports AVX-512 exponential and reciprocal instructions

AVX-512-CD - Supports AVX-512 conflict detection instructions

AVX-512-BW - Supports AVX-512 byte and word instructions

AVX-512-VL - Supports AVX-512 vector length instructions

FMA * Supports FMA extensions using YMM state

MSR * Implements RDMSR/WRMSR instructions

MTRR * Supports Memory Type Range Registers

XSAVE * Supports XSAVE/XRSTOR instructions

OSXSAVE * Supports XSETBV/XGETBV instructions

RDRAND * Supports RDRAND instruction

RDSEED * Supports RDSEED instruction

CMOV * Supports CMOVcc instruction

CLFSH * Supports CLFLUSH instruction

CX8 * Supports compare and exchange 8-byte instructions

CX16 * Supports CMPXCHG16B instruction

BMI1 * Supports bit manipulation extensions 1

BMI2 * Supports bit manipulation extensions 2

ADX * Supports ADCX/ADOX instructions

DCA - Supports prefetch from memory-mapped device

F16C * Supports half-precision instruction

FXSR * Supports FXSAVE/FXSTOR instructions

FFXSR - Supports optimized FXSAVE/FSRSTOR instruction

MONITOR * Supports MONITOR and MWAIT instructions

MOVBE * Supports MOVBE instruction

ERMSB * Supports Enhanced REP MOVSB/STOSB

PCLMULDQ * Supports PCLMULDQ instruction

POPCNT * Supports POPCNT instruction

LZCNT * Supports LZCNT instruction

SEP * Supports fast system call instructions

LAHF-SAHF * Supports LAHF/SAHF instructions in 64-bit mode

HLE - Supports Hardware Lock Elision instructions

RTM - Supports Restricted Transactional Memory instructions

DE * Supports I/O breakpoints including CR4.DE

DTES64 - Can write history of 64-bit branch addresses

DS - Implements memory-resident debug buffer

DS-CPL - Supports Debug Store feature with CPL

PCID * Supports PCIDs and settable CR4.PCIDE

INVPCID * Supports INVPCID instruction

PDCM * Supports Performance Capabilities MSR

RDTSCP * Supports RDTSCP instruction

TSC * Supports RDTSC instruction

TSC-DEADLINE * Local APIC supports one-shot deadline timer

TSC-INVARIANT * TSC runs at constant rate

xTPR * Supports disabling task priority messages

EIST * Supports Enhanced Intel Speedstep

ACPI * Implements MSR for power management

TM * Implements thermal monitor circuitry

TM2 * Implements Thermal Monitor 2 control

APIC * Implements software-accessible local APIC

x2APIC * Supports x2APIC

CNXT-ID - L1 data cache mode adaptive or BIOS

MCE * Supports Machine Check, INT18 and CR4.MCE

MCA * Implements Machine Check Architecture

PBE * Supports use of FERR#/PBE# pin

PSN - Implements 96-bit processor serial number

HTT * Hyperthreading

PREFETCHW * PrefetchW instruction support

HYPERVISOR * Hypervisor is present

VMX - Supports Intel hardware-assisted virtualization

EPT - Supports Intel extended page tables (SLAT)

URG - Supports Intel unrestricted guest

Logical to Physical Processor Map:

**------------ Physical Processor 0 (Hyperthreaded)

--*----------- Physical Processor 1

---*---------- Physical Processor 2

----*--------- Physical Processor 3

-----*-------- Physical Processor 4

------*------- Physical Processor 5

-------*------ Physical Processor 6

--------*----- Physical Processor 7

---------*---- Physical Processor 8

----------**-- Physical Processor 9 (Hyperthreaded)

------------*- Physical Processor 10

-------------* Physical Processor 11

Logical Processor to Socket Map:

************** Socket 0

Logical Processor to NUMA Node Map:

************** NUMA Node 0

No NUMA nodes.

Logical Processor to Cache Map:

**------------ Data Cache 0, Level 1, 48 KB, Assoc 12, LineSize 64

**------------ Instruction Cache 0, Level 1, 64 KB, Assoc 16, LineSize 64

**------------ Unified Cache 0, Level 2, 2 MB, Assoc 16, LineSize 64

************-- Unified Cache 1, Level 3, 12 MB, Assoc 12, LineSize 64

--*----------- Data Cache 1, Level 1, 32 KB, Assoc 8, LineSize 64

--*----------- Instruction Cache 1, Level 1, 64 KB, Assoc 8, LineSize 64

--****-------- Unified Cache 2, Level 2, 2 MB, Assoc 16, LineSize 64

---*---------- Data Cache 2, Level 1, 32 KB, Assoc 8, LineSize 64

---*---------- Instruction Cache 2, Level 1, 64 KB, Assoc 8, LineSize 64

----*--------- Data Cache 3, Level 1, 32 KB, Assoc 8, LineSize 64

----*--------- Instruction Cache 3, Level 1, 64 KB, Assoc 8, LineSize 64

-----*-------- Data Cache 4, Level 1, 32 KB, Assoc 8, LineSize 64

-----*-------- Instruction Cache 4, Level 1, 64 KB, Assoc 8, LineSize 64

------*------- Data Cache 5, Level 1, 32 KB, Assoc 8, LineSize 64

------*------- Instruction Cache 5, Level 1, 64 KB, Assoc 8, LineSize 64

------****---- Unified Cache 3, Level 2, 2 MB, Assoc 16, LineSize 64

-------*------ Data Cache 6, Level 1, 32 KB, Assoc 8, LineSize 64

-------*------ Instruction Cache 6, Level 1, 64 KB, Assoc 8, LineSize 64

--------*----- Data Cache 7, Level 1, 32 KB, Assoc 8, LineSize 64

--------*----- Instruction Cache 7, Level 1, 64 KB, Assoc 8, LineSize 64

---------*---- Data Cache 8, Level 1, 32 KB, Assoc 8, LineSize 64

---------*---- Instruction Cache 8, Level 1, 64 KB, Assoc 8, LineSize 64

----------**-- Data Cache 9, Level 1, 48 KB, Assoc 12, LineSize 64

----------**-- Instruction Cache 9, Level 1, 64 KB, Assoc 16, LineSize 64

----------**-- Unified Cache 4, Level 2, 2 MB, Assoc 16, LineSize 64

------------*- Data Cache 10, Level 1, 32 KB, Assoc 8, LineSize 64

------------*- Instruction Cache 10, Level 1, 64 KB, Assoc 8, LineSize 64

------------** Unified Cache 5, Level 2, 2 MB, Assoc 16, LineSize 64

-------------* Data Cache 11, Level 1, 32 KB, Assoc 8, LineSize 64

-------------* Instruction Cache 11, Level 1, 64 KB, Assoc 8, LineSize 64

Logical Processor to Group Map:

************** Group 0

Coreinfo(3 MB)Şimdi Sysinternals Live'dançalıştırın.

Coreinfo(3 MB)Şimdi Sysinternals Live'dançalıştırın.

Çalıştığı yer:

- İstemci: Windows 11 ve üzeri.

- Sunucu: Windows Server 2016 ve üzeri.