Cursos

Módulo

Manage drivers and device peripherals - Training

This module introduces device drivers. Student will learn how drivers work and the tools used to manage common peripheral devices such as printers.

Este explorador ya no se admite.

Actualice a Microsoft Edge para aprovechar las características y actualizaciones de seguridad más recientes, y disponer de soporte técnico.

A partir de Windows 8, la extensión de marco GPIO (GpioClx) simplifica la tarea de escribir un controlador para un dispositivo de controlador GPIO. Además, GpioClx proporciona soporte para controladores de dispositivos periféricos que se conectan a pines GPIO. GpioClx, que es una extensión proporcionada por el sistema al marco de controladores en modo kernel (KMDF), realiza tareas de procesamiento que son comunes a los miembros de la clase de dispositivo GPIO.

En esta introducción se describen los siguientes artículos:

Los proveedores de hardware suministran controladores para controlar sus controladores GPIO. Un controlador de controlador GPIO es un controlador KMDF que administra todas las operaciones específicas del hardware para un controlador GPIO. El controlador del controlador GPIO colabora con GpioClx para controlar las solicitudes de E/S para grupos de patillas GPIO configuradas como entradas de datos y salidas de datos. Además, este controlador colabora con GpioClx para controlar las solicitudes de interrupción de los pines GPIO configurados como entradas de interrupción.

Un dispositivo de controlador GPIO tiene cierto número de pines GPIO. Estos pines se pueden conectar físicamente a dispositivos periféricos. Los pines GPIO se pueden configurar como entradas de datos, salidas de datos o entradas de solicitud de interrupción. Normalmente, un pin GPIO se dedica a un dispositivo periférico y no lo comparten dos o más dispositivos. Las conexiones entre patillas GPIO y dispositivos periféricos son fijas y el usuario no puede cambiarlas (por ejemplo, quitando un dispositivo periférico y reemplazando por otro dispositivo). Por lo tanto, la asignación de pines GPIO a dispositivos periféricos se puede describir en el firmware de la plataforma.

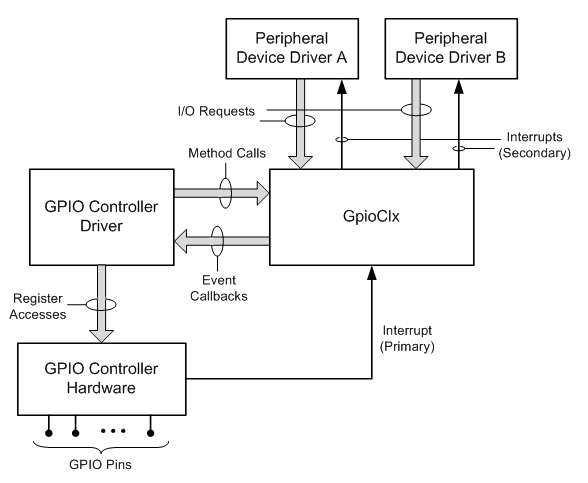

En el diagrama siguiente se muestra el controlador del controlador GPIO y GpioClx.

El controlador GPIO y GpioClx se comunican entre sí a través de la interfaz de controlador de dispositivo (DDI) de GpioClx. El controlador GPIO invoca los métodos de soporte del controlador que son implementados por GpioClx. GpioClx llama a funciones de devolución de llamada de eventos que implementa el controlador GPIO.

El controlador del controlador GPIO accede directamente a los registros de hardware del dispositivo del controlador GPIO.

GpioClx controla las solicitudes de E/S de los controladores de los dispositivos periféricos que se conectan físicamente a pines GPIO. GpioClx traduce estas solicitudes de E/S en operaciones de hardware simples, que realiza llamando a las funciones de devolución de llamada de eventos implementadas por el controlador GPIO. Por ejemplo, para leer o escribir datos en un conjunto de pines GPIO, GpioClx llama a funciones de devolución de llamada de eventos como CLIENT_ReadGpioPins y CLIENT_WriteGpioPins. GpioClx administra las colas de E/S para el controlador GPIO y, por tanto, libera al controlador GPIO de esta tarea.

Además, GpioClx controla las interrupciones principales del dispositivo del controlador GPIO y asigna estas interrupciones a las interrupciones secundarias, que se controlan mediante controladores de dispositivos periféricos. Las interrupciones principales son interrupciones generadas por dispositivos de hardware. El sistema operativo genera interrupciones secundarias en respuesta a determinadas interrupciones principales. Las interrupciones principales y secundarias se identifican mediante interrupciones del sistema global (GSIs). El firmware ACPI de la plataforma de hardware asigna GSIs a interrupciones principales y, en tiempo de ejecución, el sistema operativo asigna GSIs a interrupciones secundarias.

Por ejemplo, el firmware asigna un GSI a la interrupción de hardware del controlador GPIO y el sistema operativo asigna un GSI a un pin GPIO configurado como entrada de interrupción.

GpioClx implementa un ISR que controla las interrupciones principales generadas por hardware del dispositivo del controlador GPIO. Cuando un dispositivo periférico provoca una interrupción en un pin GPIO y las interrupciones de este pin están habilitadas y desenmascaradas, el controlador GPIO interrumpe el procesador. En respuesta, el controlador de interceptaciones del kernel programa que el ISR GpioClx se ejecute. Para identificar el pin GPIO que provocó la interrupción, el ISR GpioClx llama a la función de devolución de llamada de evento CLIENT_QueryActiveInterrupts, que implementa el controlador GPIO. A continuación, el ISR gpioClx busca el GSI asignado a este pin y pasa este GSI a la capa de abstracción de hardware (HAL). El HAL genera una interrupción secundaria llamando al ISR registrado para este GSI. Este ISR pertenece al controlador del dispositivo periférico que aseró originalmente la interrupción.

Para obtener más información sobre las interrupciones principales y secundarias, consulte Interrupciones GPIO.

En el inicio, el administrador de Plug and Play (PnP) enumera los dispositivos PnP y los dispositivos que no son PnP. En el caso de dispositivos que no son PnP con conexiones fijas a patillas GPIO, el administrador de PnP consulta el firmware de la plataforma para determinar qué patillas GPIO se asignan como recursos de hardware administrados por el sistema a estos dispositivos.

El controlador KMDF de un dispositivo periférico recibe los recursos de hardware asignados durante un callback de EvtDevicePrepareHardware. Estos recursos pueden incluir pines GPIO configurados como salidas de datos, entradas de datos o entradas para solicitud de interrupción.

Un recurso de E/S de GPIO es un nuevo tipo de recurso de Windows en Windows 8. Este recurso consta de un conjunto de pines GPIO que se pueden usar como entradas o salidas de datos. Si un controlador de dispositivo periférico abre un recurso de E/S de GPIO para lecturas, el controlador usa todas las patillas del recurso como entradas de datos. Si un controlador abre un recurso de E/S de GPIO para operaciones de escritura, el controlador utiliza todos los pines de ese recurso como salidas de datos. Para ver ejemplos de código que muestran cómo un controlador de dispositivo periférico abre una conexión lógica a un conjunto de patillas de E/S de GPIO, consulte los temas siguientes:

Conectar un controlador de KMDF a pines de E/S GPIO

Un pin GPIO configurado como entrada de interrupción se asigna a un controlador como un recurso de interrupción normal de Windows. La abstracción de recursos de interrupción oculta el hecho de que una interrupción se pueda implementar mediante un pin GPIO en lugar de, por ejemplo, un controlador de interrupción programable. Por lo tanto, el controlador puede tratar un recurso de interrupción basado en GPIO igual que cualquier otro recurso de interrupción.

Para acceder a los pines GPIO en un recurso de E/S de GPIO, un controlador de dispositivo periférico debe establecer una conexión lógica a los pines. Un controlador KMDF llama al método WdfIoTargetOpen para abrir la conexión. A través de esta conexión, el controlador puede enviar solicitudes de E/S a las patillas GPIO. El controlador envía IOCTL_GPIO_READ_PINS solicitudes para leer datos de estos pines (si son patillas de entrada) o IOCTL_GPIO_WRITE_PINS solicitudes para escribir datos en ellos (si son patillas de salida).

Para recibir interrupciones del pin GPIO en un recurso de interrupción, un controlador de dispositivo periférico debe registrar su rutina de servicio de interrupción (ISR) para recibir interrupciones del recurso de interrupción implementado por este pin. Un controlador KMDF llama al método WdfInterruptCreate para conectar un ISR a la interrupción.

Cursos

Módulo

Manage drivers and device peripherals - Training

This module introduces device drivers. Student will learn how drivers work and the tools used to manage common peripheral devices such as printers.