Megjegyzés

Az oldalhoz való hozzáféréshez engedély szükséges. Megpróbálhat bejelentkezni vagy módosítani a címtárat.

Az oldalhoz való hozzáféréshez engedély szükséges. Megpróbálhatja módosítani a címtárat.

Készítette: Mark Russinovich

Közzétéve: 2025. december 16.

Coreinfo letöltése(3 MB)

Coreinfo letöltése(3 MB)

Bevezetés

A Coreinfo egy segédprogram, amely bemutatja a logikai processzorok és a fizikai processzor, a NUMA-csomópont és a szoftvercsatornák közötti leképezést, valamint az egyes logikai processzorokhoz rendelt gyorsítótárakat. Alacsony szintű Windows API-kat használ (felhasználói mód és kernel mód) a részletes CPU-topológiaadatok közvetlenül az operációs rendszerből való lekéréséhez. A parancssori verzió egy csillaggal (például ""* ) rendelkező logikai processzorra való leképezés ábrázolását adja ki. A felhasználói felület több speciális nézetet biztosít a rendszer CPU-topológiájának különböző aspektusainak megismeréséhez, beleértve a logikai és fizikai magokat, a NUMA-csomópontokat, a szoftvercsatornákat, a gyorsítótár-hierarchiákat és a valós idejű teljesítménymetrikát. A Coreinfo hasznos a rendszer processzor- és gyorsítótár-topológiájának megismeréséhez.

Telepítés

Bontsa ki az archívumot egy könyvtárba, majd futtassa a Coreinfo-t az adott könyvtárból Coreinfo / Coreinfo64 vagy Coreinfo64aaz architektúrától függően. Indítsa el CoreInfoEx / CoreInfoEx64 / CoreInfoEx64a a felhasználói felület verzióját.

Megjegyzés: Egyes funkciókhoz rendszergazdai jogosultságokra lehet szükség a teljes információlekéréshez.

Felhasználói felület áttekintése

A Coreinfo felhasználói felülete több fő összetevőből áll:

Főablak elrendezése

- Felső panel: Megjeleníti a rendszerinformációkat, beleértve a processzor nevét, architektúráját és magszámát

- Navigációs ablak (balra): Gyors hozzáférést biztosít a különböző nézetekhez

- Tartalomterület (Központ): A kijelölt nézet adatainak és vizualizációinak megjelenítése

- Részletek panel (alul): Részletes információkat jelenít meg a magok vagy cellák kijelölésekor

- Beállítások: Hozzáférési megjelenési beállítások és alkalmazásbeállítások

A teljes felhasználói felület elrendezését megjelenítő főablak, sötét mód

A teljes felhasználói felület elrendezését megjelenítő főablak, sötét mód

Navigációs nézetek

A bal oldali navigációs ablak hat speciális nézethez biztosít hozzáférést:

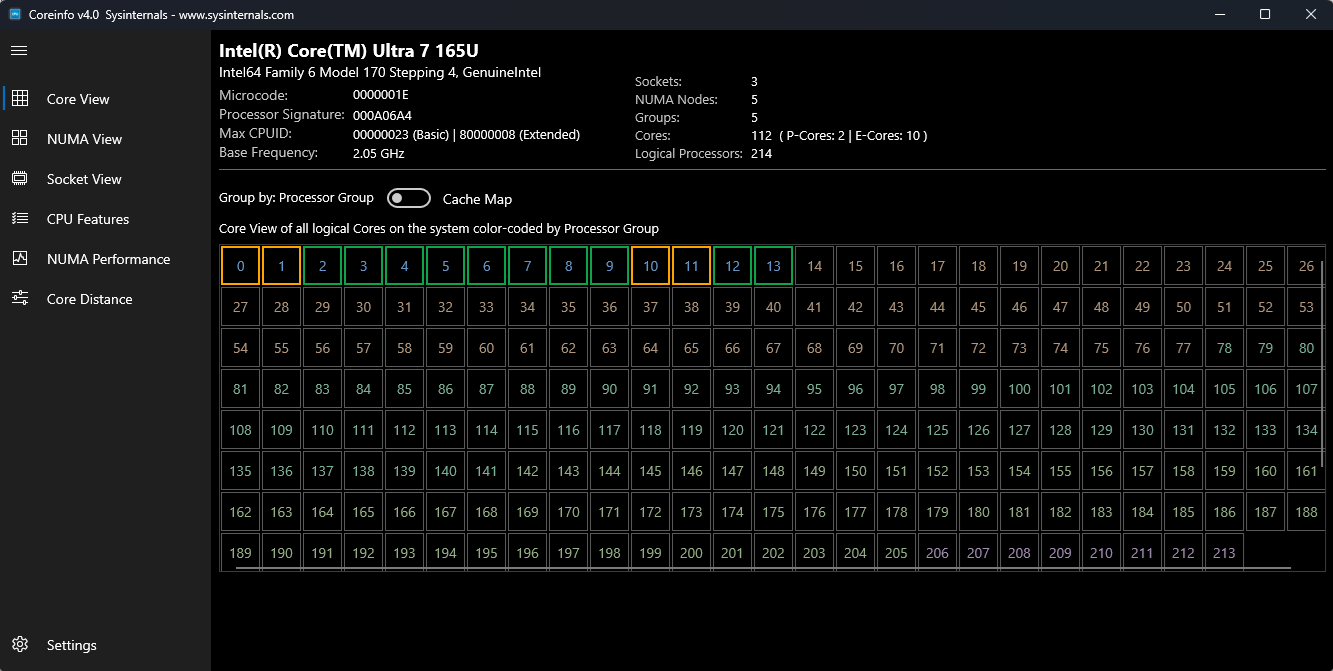

1. Alapnézet

A Core Nézet rácsos elrendezésben jeleníti meg a rendszer összes logikai processzorát, és megjeleníti a logikai magok és a fizikai erőforrások közötti kapcsolatot.

Funkciók:

- Rács elrendezése: Minden cella logikai processzort jelöl

-

Alapvető típusjelzők:

- P-Cores (Teljesítménymagok) – eltérő színekkel jelölt

- E-Magok (Hatékonysági magok) – másképp színezve

- Standard proceszor-magok – alapértelmezett színbeállítás

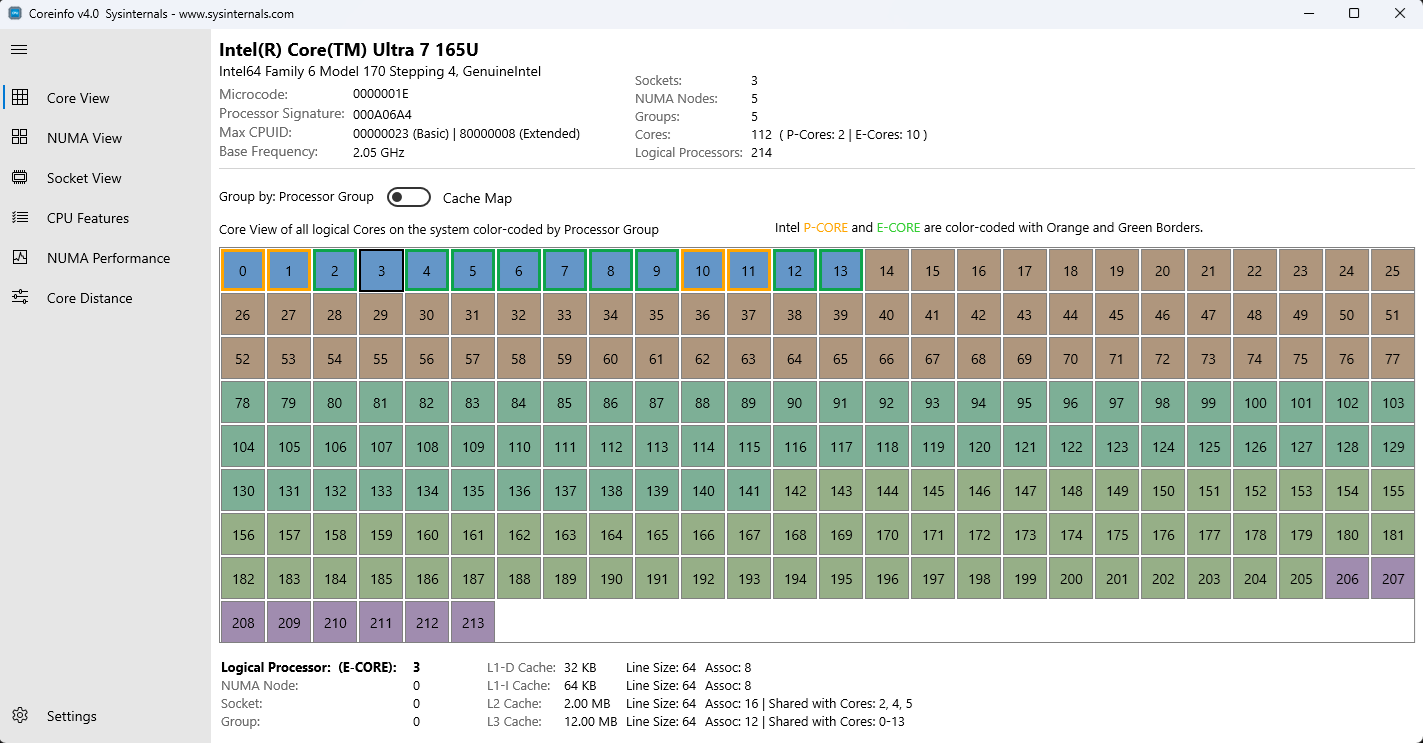

- Gyorsítótár-leképezés kapcsolója: Váltás az alapértelmezett nézet és a gyorsítótárhierarchia nézet között

- Interaktív kijelölés: Kattintson bármelyik magra a részletes információk megtekintéséhez az alsó panelen

Megjelenített információk:

- Logikai processzor száma

- Magtípus (P-Core/E-Core, ha van)

- Cache szintek társítása (L1, L2, L3)

- NUMA-csomópont hozzárendelése

- Szoftvercsatorna-hozzárendelés

- Csoport-hozzárendelés

Core View– logikai processzorok rácselrendezésben

Core View– logikai processzorok rácselrendezésben

Részletek panel információi (ha egy magot választottak ki):

- Processzormaszk és affinitás

- Gyorsítótár-hierarchia (adatgyorsítótár, utasítás-gyorsítótár, egyesített gyorsítótár)

- Gyorsítótár méretei és asszociativitása

- Gyorsítótár sorhosszai

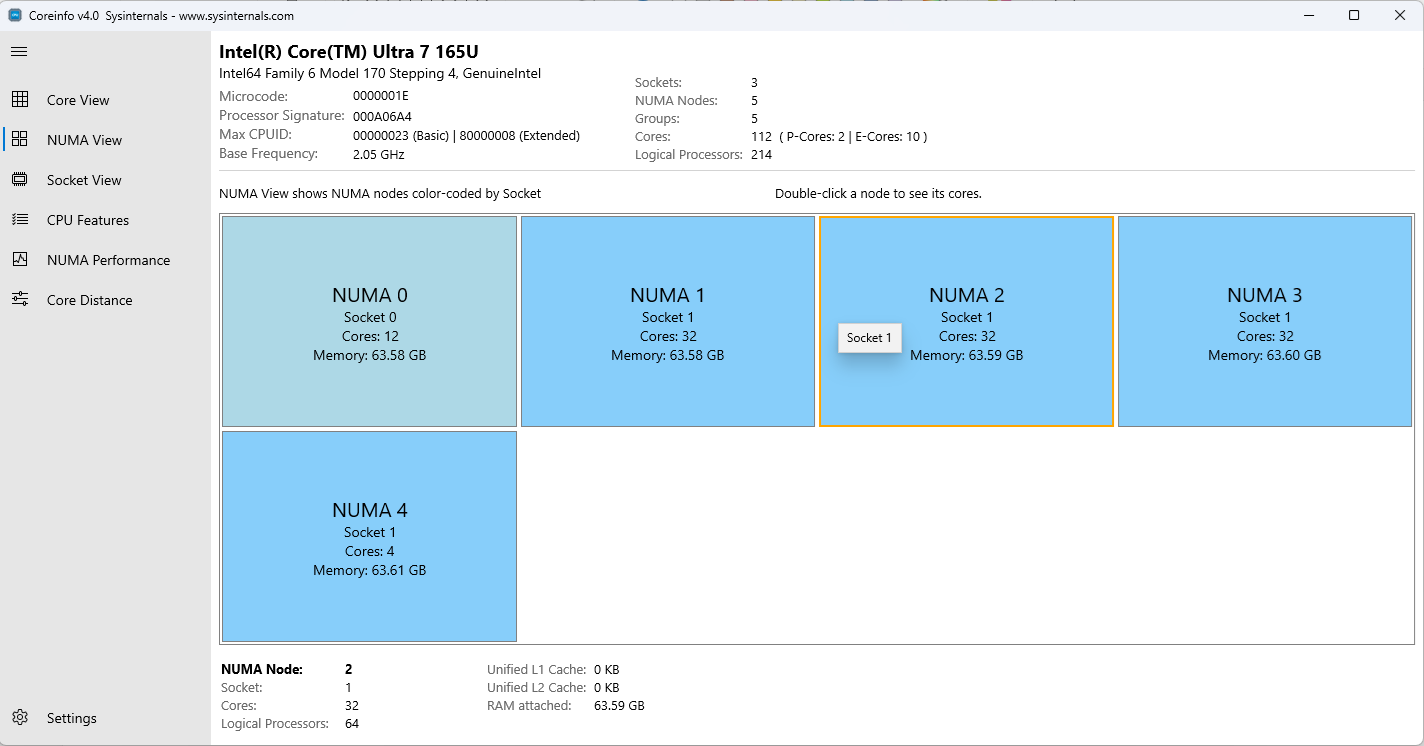

2. NUMA nézet

A NUMA (nem egységes memóriahozzáférés) nézet a magokat A NUMA-csomópont-hozzárendelések alapján rendszerezi, így könnyen érthetővé válik a memória helyének és a hozzáférési mintáknak a megértése.

Funkciók:

- Csomópont-Alapú Rendszer: Magok csoportosítása NUMA-csomópontok szerint

- Fizikai és logikai magok: Az egyes csomópontok mindkét számát megjeleníti

- Memóriaadatok: A rendelkezésre álló memória megjelenítése NUMA-csomópontonként

-

Interaktív navigáció:

- Egy NUMA-csomópontra kattintva megjelenítheti a részleteket az alsó részletek panelen

- Kattintson duplán egy NUMA-csomópontra a kiválasztott NUMA-csomópont összes magját megjelenítő Core nézethez

- Hierarchikus megjelenítés: A NUMA-csomópontok és magok közötti kapcsolatot jeleníti meg

Megjelenített információk:

- NUMA-csomópontok száma

- Magok NUMA-csomópontonként (fizikai és logikai)

- Memóriakapacitás csomópontonként

- Mageloszlás csomópontok között

- Hatékonysági magok száma (ha van)

NUMA Nézet, amely megmutatja a NUMA csomópontok szerint szervezett magokat

NUMA Nézet, amely megmutatja a NUMA csomópontok szerint szervezett magokat

Használati esetek:

- Memóriahozzáférési minták optimalizálása

- A NUMA-ra vonatkozó alkalmazásteljesítmény ismertetése

- Szál/folyamat elhelyezésének megtervezése az optimális teljesítmény érdekében

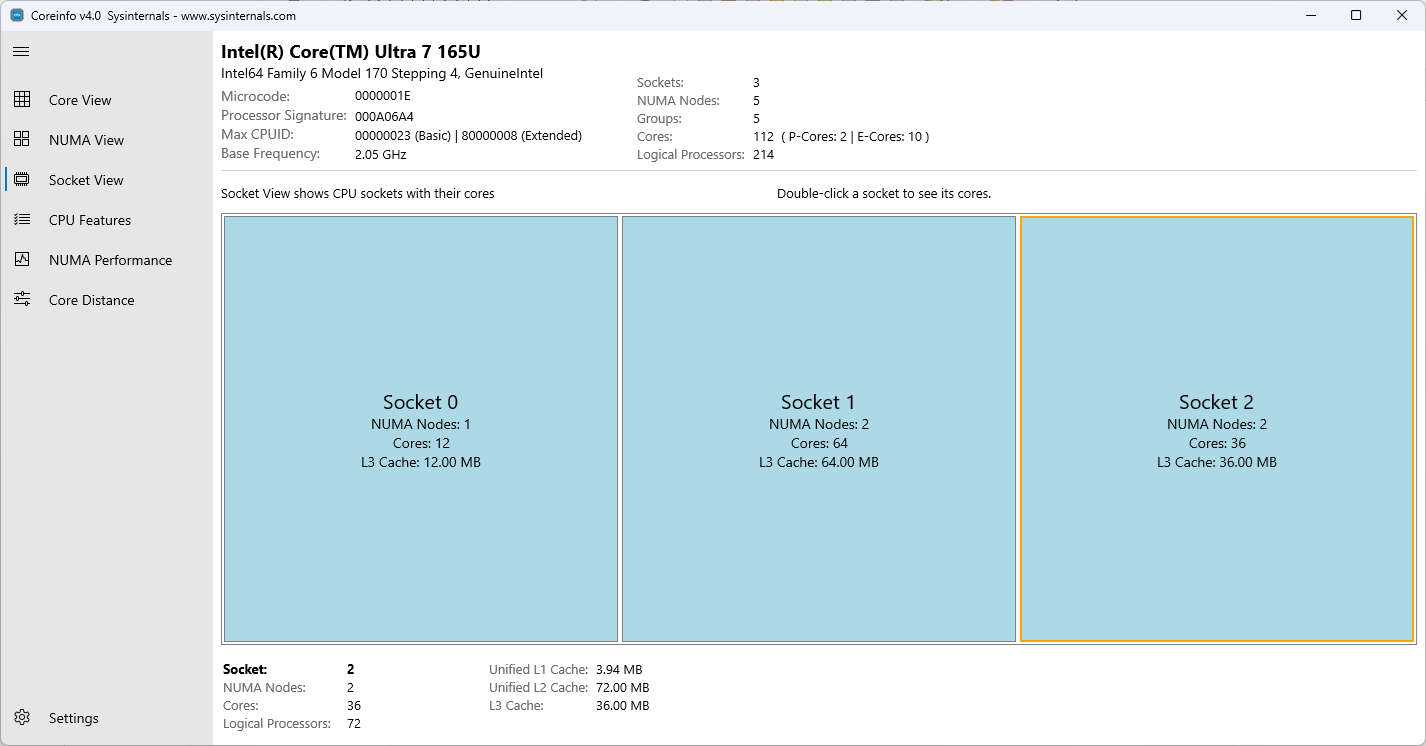

3. Csatlakozó Nézet

A Szoftvercsatorna nézet a fizikai CPU-szoftvercsatornájuk szerint rendszerezett magokat jelenít meg, amelyek hasznosak a többcsatornás rendszerek és a szoftvercsatornák szintű erőforrás-elosztás megértéséhez.

Funkciók:

- Socket-Based Csoportosítás: Fizikai foglalatok szerint rendszerezett magok

- Csatlakozó információk: Csatlakozók száma és mageloszlás

-

Interaktív navigáció:

- Kattintson egy csatlakozóra a részletek megjelenítéséhez az alsó panelen

- Kattintson duplán egy foglalatra a Core Nézetre való navigálásért, amely megjeleníti a kiválasztott foglalat minden magját.

- Gyorsítótár-megosztás: Vizualizálja, melyik magok osztanak meg foglalatszintű gyorsítótárakat

Megjelenített információk:

- Fizikai foglalatok száma

- Magok foglalatonként (fizikai és logikai)

- Szoftvercsatornaszintű gyorsítótár információi

- NUMA-csomópontok foglalatonként

Foglalat nézet, amely a CPU foglalatok szerint rendezett magokat mutatja

Foglalat nézet, amely a CPU foglalatok szerint rendezett magokat mutatja

Használati esetek:

- Többfoglalatú rendszerelemzés

- A szoketektől eltérő kommunikációs költségek megértése

- Számítási feladatok elosztásának tervezése többcsatornás kiszolgálókon

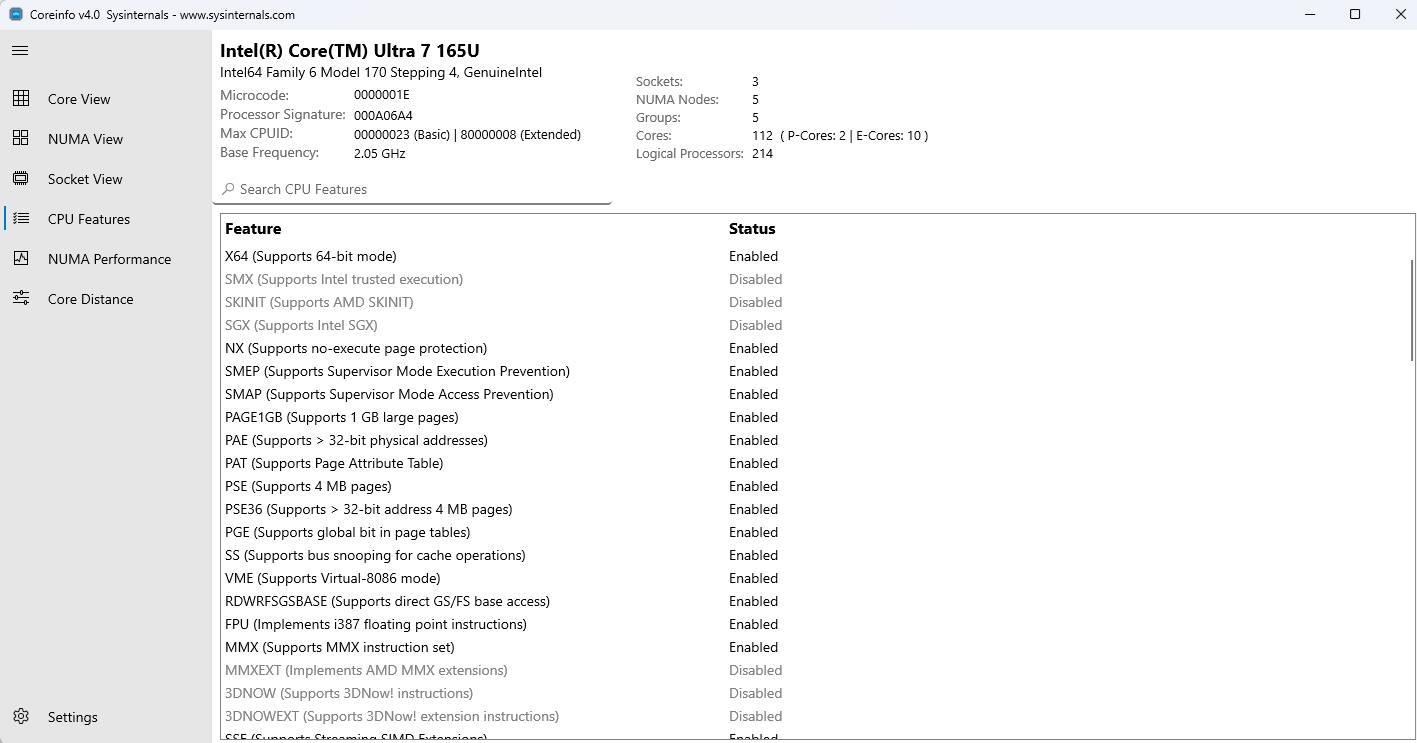

4. CPU-funkciók nézet

A CPU-funkciók nézet a processzor képességeinek, az utasításkészlet bővítményeinek és a processzor által támogatott hardverfunkcióknak átfogó listáját jeleníti meg.

Funkciók:

- Kereshető lista: Adott CPU-funkciók gyors megkeresése a keresősáv használatával

-

Állapotjelzők: A támogatott/nem támogatott funkciók vizuális jelzésének törlése színkódolással

- A támogatott funkciók normál színben jelennek meg

- A nem támogatott/letiltott funkciók szürkére vannak szürkítve

-

Szolgáltatáskategóriák:

- Virtualizálás (VMX, SVM, HYPERVISOR)

- 64 bites támogatás (EM64T, NX)

- Utasításkészletek (SSE, AVX, AES stb.)

- Energiagazdálkodás (EIST, ACPI, Thermal)

- Biztonsági funkciók (SMX, SKINIT)

- Memóriafunkciók (PAE, PAT, PSE)

- Hibakeresési és monitorozási funkciók

Megjelenített információk:

- Funkció rövidítése

- Funkció állapota (támogatott/nem támogatott)

- Teljes funkcióleírás (a részletek panelen)

A processzorfunkciók nézet a processzor képességeinek listáját jeleníti meg

A processzorfunkciók nézet a processzor képességeinek listáját jeleníti meg

Megjegyzés: Egyes virtualizálási funkciók (például VMX, SVM) helytelenül jelenthetők úgy, hogy nem érhetők el aktív hipervizorral vagy virtuális gépről való futtatáskor. A Coreinfo-t olyan rendszeren kell végrehajtani, amely nem futtat hipervizort a pontos eredmények érdekében.

Használati esetek:

- Az utasítások rendelkezésre állásának ellenőrzése az alkalmazások üzembe helyezése előtt

- Virtualizálási támogatás ellenőrzése

- A processzorok létrehozásának és képességeinek ismertetése

- Hiányzó CPU-funkciókkal kapcsolatos teljesítményproblémák hibakeresése

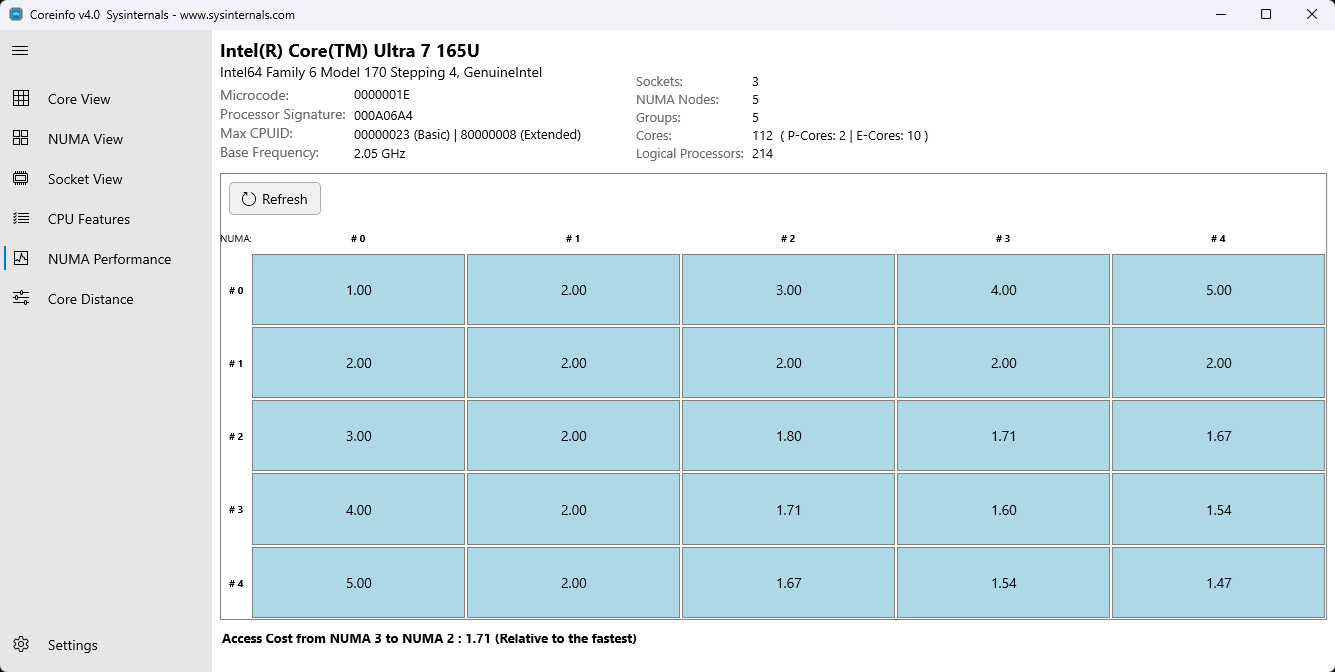

5. NUMA teljesítménynézet

A NUMA teljesítménynézete a NUMA-csomópontok közötti memória-hozzáférési költségeket ábrázoló rácsos vizualizációt biztosít, amely segít azonosítani a NUMA-rendszerek teljesítménybeli szűk keresztmetszeteit.

Funkciók:

- Rácsos vizualizáció: Relatív memóriaelérési költségeket megjelenítő mátrix a NUMA-csomópontok között

- Interaktív mátrix: Vigye az egérmutatót a cellák fölé a részletes teljesítményinformációk megtekintéséhez

- Real-Time Frissítések: A teljesítményadatok dinamikus frissítése a Frissítés gombra kattintva

- Relatív költség megjelenítése: A különböző NUMA-csomópontokból származó memóriához való hozzáférés relatív költségét jeleníti meg

Megjelenített információk:

- NxN-mátrix, ahol N = NUMA-csomópontok száma

- Memóriahasználati költség a forrás NUMA-csomóponttól (sortól) a cél NUMA-csomópontig (oszlop)

- Relatív teljesítményköltségeket megjelenítő numerikus értékek

- Az átlós cellák helyi memóriahozzáférést mutatnak (általában a legalacsonyabb költség)

NUMA teljesítményrács a memóriahozzáférési költségekkel

NUMA teljesítményrács a memóriahozzáférési költségekkel

A rács ismertetése:

- Átlós elemek: A helyi memóriahozzáférés (a saját memóriáját elérő csomópont) ábrázolása – általában a legalacsonyabb értékek

- Nem átlós elemek: A távoli memóriahozzáférést magasabb relatív költség jellemzi

- Szimmetria: A mátrix nem feltétlenül szimmetrikus, mivel a hozzáférési költségek irányonként eltérőek lehetnek

Használati esetek:

- A NUMA-ra vonatkozó teljesítmény szűk keresztmetszeteinek azonosítása

- Memóriafoglalási stratégiák optimalizálása

- Folyamat/szál rögzítése NUMA-rendszerekhez

- A csomópontok közötti memóriahozzáférési szankciók ismertetése

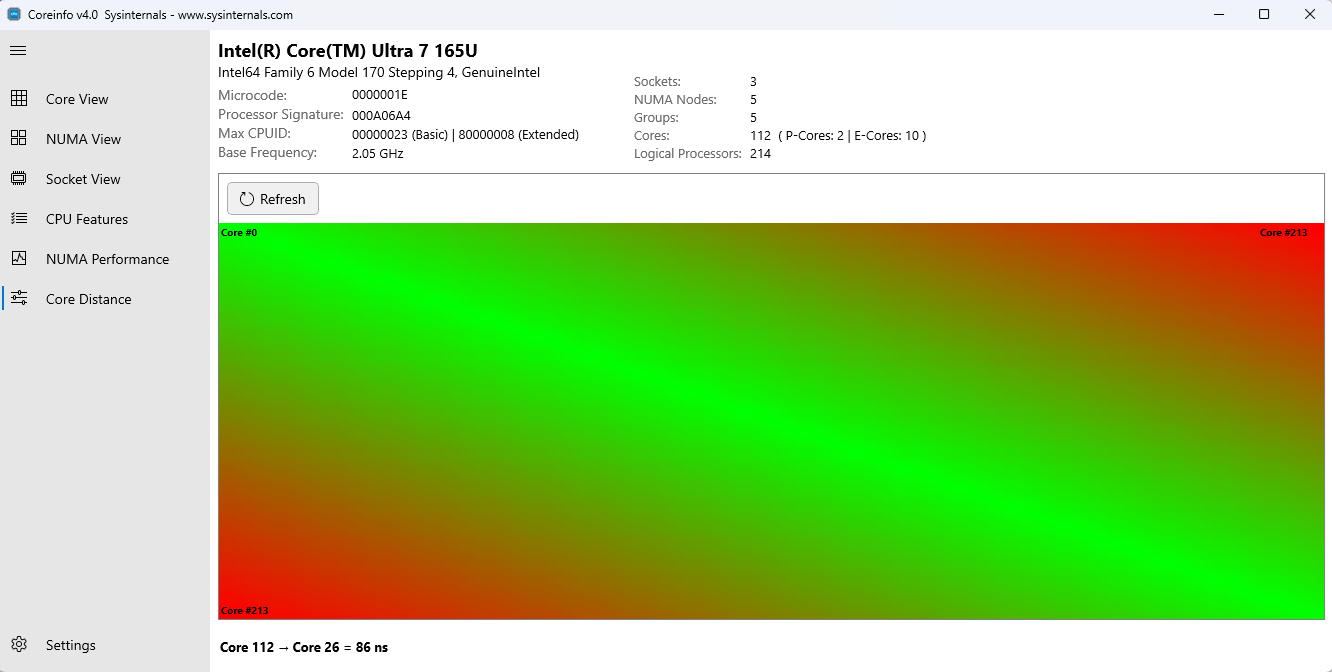

6. Magtávolság Nézet

A Core Distance View részletes hőtérképet jelenít meg az egyes CPU-magok közötti kommunikációs költségekről, és betekintést nyújt a magok közötti késésbe és a kommunikációs hatékonyságba.

Funkciók:

-

Core-Level Hőtérkép: A magok közötti relatív távolságokat megjelenítő színkódolt mátrix

- Zöld/kék = Alacsony késés (ugyanaz a magfürt, megosztott gyorsítótár)

- Sárga/narancssárga = Közepes késés (ugyanaz a foglalat, különböző klaszter)

- Vörös = Magas latencia (eltérő foglalat vagy NUMA-csomópont)

- Interaktív feltárás: Vigye az egérmutatót a rácsvászonra a részletes távolságadatok megtekintéséhez

- Részletes elemzés: A mag és a mag közötti kapcsolatokat a legapróbb részletességgel jeleníti meg

- Dinamikus frissítés: A Frissítés gombbal dinamikusan szerezheti be a frissített mag távolságadatait

Megjelenített információk:

- NxN-mátrix, ahol N = logikai processzorok száma

- Relatív távolság/késés a forrásmagtól (sortól) a célmagig (oszlop)

- Színkódolás az alapvető kapcsolatok gyors vizuális azonosításához

- Részletes távolságmetrikák a részletek panelen

Mag-távolság hőtérkép, amely a magok közötti kommunikációs költségeket mutatja

Mag-távolság hőtérkép, amely a magok közötti kommunikációs költségeket mutatja

A távolsági térkép ismertetése:

- Átlós elemek: Mindig nulla (önmagával való kapcsolat)

- Kis távolság (zöld): A magok L2 vagy L3 gyorsítótárat használnak

- Közepes távolság (sárga): Magok ugyanazon a foglalaton, de különböző gyorsítótár-területekben

- Nagy távolság (piros): Magok különböző foglalatokon vagy NUMA-csomópontokon

Használati esetek:

- Szál affinitás optimalizálása

- A gyorsítótár-koherenciatartományok ismertetése

- A szálak kommunikációjának optimális magpárjainak azonosítása

- Többszálas alkalmazás teljesítményének elemzése

- Cpu-rögzítési stratégiák tervezése alacsony késésű alkalmazásokhoz

Interaktív funkciók

Alapvető kijelölés és részletek

Ha bármelyik nézetben (Core, NUMA vagy Socket) rákattint egy magra, részletes információk jelennek meg a részletek panel alsó részén.

- Processzoradatok: Logikai processzorszám, maszk és affinitás

-

Gyorsítótár-hierarchia:

- L1 Adat Cache (méret, asszociativitás, vonalméret)

- L1 Utasítás-gyorsítótár (méret, asszociativitás, vonalméret)

- L2 Cache (méret, asszociativitás, vonalméret)

- L3 Cache (méret, asszociativitás, vonalméret)

- Topológiainformáció: NUMA csomópont, foglalat és csoport-hozzárendelés.

- Alaptípus: P-Core, E-Core vagy standard magjelölés

Keresési funkciók

A CPU-szolgáltatások nézet tartalmaz egy keresősávot, amely lehetővé teszi bizonyos processzorfunkciók gyors megkeresését:

- Kattintson a keresés ikonra

- Írja be a szolgáltatás nevét vagy rövidítését

- A lista automatikusan szűr az egyező funkciók megjelenítésére

- A keresés törlése a teljes lista visszaállításához

Gyorsítótár-térkép kapcsoló

Core nézetben váltson két vizualizációs mód között:

- Alapértelmezett mód: A magok logikai elrendezésben való megjelenítése

- Gyorsítótár-leképezési mód: A magok átrendezése a gyorsítótármegosztási kapcsolatok vizualizációja érdekében

Navigálás nézetek között

- Váltás a nézetek között a bal oldali navigációs panelen

- Ha egy adott NUMA-csomópontot vagy foglalatot tekint meg, ugyanarra a nézetre kattintva ismét visszatér a teljes nézethez.

- Az aktuális nézet ki van emelve a navigációs panelen

Beállítások és testreszabás

A beállítások elérése a navigációs menü Beállítások lehetőségével.

Megjelenési beállítások

Témabeállítások:

- Világos: Világos színséma fényes környezetekhez optimalizálva

- Sötét: Sötét színséma a szem terhelésének csökkentéséhez

- Alapértelmezett rendszer: Automatikusan megfelel a Windows-téma beállításainak

Mentés fájlba

Alapvető topológiaadatok exportálása:

- Használja a Mentés ide opciót az alapvető topológiaadatok fájlba való mentéséhez.

- A kimeneti formátum megegyezik a parancssori eszköz kimenetével

A rendszertopológia ismertetése

Alapvető típusok (hibrid architektúra)

A modern CPU-k különböző magtípusokkal rendelkező hibrid architektúrákat tartalmazhatnak:

- P-Cores (Performance): Nagy teljesítményű magok, amelyek egyszálas és igényes számítási feladatokhoz optimalizálva

- E-Magok (Hatékonyság): Háttérfeladatokhoz és többszálas számítási feladatokhoz optimalizált energiatakarékos magok

A Coreinfo felhasználói felülete egyértelműen azonosítja és megkülönbözteti ezeket az alapvető típusokat minden alkalmazható nézetben.

NUMA-architektúra

Mi az a NUMA? A nem egységes memóriahozzáférés (NUMA) egy olyan memóriaterv, amelyben minden processzor helyi memóriával rendelkezik, amely gyorsan elérhető, és a távoli memóriához processzorközi kommunikáció szükséges.

Miért fontos:

- A helyi memóriahozzáférés jelentősen gyorsabb, mint a távelérés

- Az alkalmazás teljesítményét jelentősen befolyásolhatja a NUMA elhelyezése

- A NUMA-topológia megértése kritikus fontosságú a nagy teljesítményű számítástechnika szempontjából

A Coreinfo felhasználói felületének használata a NUMA-optimalizáláshoz:

- A NUMA nézet használata a rendszer NUMA-topológiájának megismeréséhez

- Ellenőrizze a NUMA teljesítménynézetét a memóriahozzáférési költségek megtekintéséhez

- Szál-/folyamatelhelyezés optimalizálása NUMA-csomópont-hozzárendelések alapján

- A Core Distance View használatával megismerheti a magok közötti kommunikációt a NUMA-csomópontokon belül és azok között

Gyorsítótár-hierarchia

Gyorsítótár szintjei:

- L1 Gyorsítótár: Legkisebb és leggyorsabb, adat- és utasítás-gyorsítótárakra felosztva

- L2 Cache: Nagyobb egységes gyorsítótár, általában privát az egyes magok számára

- L3 Cache: A legnagyobb egységes gyorsítótár, gyakran több mag között megosztva

Gyorsítótáradatok használata:

- Annak megismerése, hogy mely magok osztják meg a gyorsítótár erőforrásait

- Adat helyének optimalizálása gyorsítótár-megosztó magokhoz

- Gyorsítótár-leképezési mód használata a Core nézetben a gyorsítótár-tartományok vizualizációja érdekében

A Coreinfo használata a parancssorból

Minden erőforrás esetében megjeleníti az operációs rendszer által látható processzorok térképét, amelyek megfelelnek a megadott erőforrásoknak, és a megfelelő processzorokat "*" jelöli. Például egy 4 magos rendszeren a gyorsítótár kimenetének egy sora a 3. és a 4. magok által megosztott térképpel.

Használat:

coreinfo [-c][-f][-g][-l][-n][-s][-m][-v]

| Paraméter | Leírás |

|---|---|

| -c | Magok memóriaképe. |

| -f | Alapvető funkcióinformációk memóriaképe. |

| -g | A csoportokra vonatkozó memóriaképadatok. |

| -l | Gyorsítótárak adatainak memóriaképe. |

| -n | A NUMA-csomópontok adatainak memóriaképe. |

| -s | Szoftvercsatornák memóriaképe. |

| -m | A NUMA hozzáférési költségeinek memóriaképe. |

| -v | Csak virtualizálással kapcsolatos funkciók memóriaképe, beleértve a második szintű címfordítás támogatását is. (rendszergazdai jogokat igényel az Intel-rendszereken). |

Alapértelmezés szerint minden beállítás ki van választva, kivéve -v.

Coreinfo kimenet:

Coreinfo v4.0 - Dump information on system CPU and memory topology

Copyright © 2008-2025 Mark Russinovich

Sysinternals - www.sysinternals.com

Intel(R) Core(TM) Ultra 7 165U

Intel64 Family 6 Model 170 Stepping 4, GenuineIntel

Microcode signature: 0000001E

Processor signature: 000A06A4

Maximum implemented CPUID leaves: 00000023 (Basic), 80000008 (Extended).

Maximum implemented address width: 48 bits (virtual), 46 bits (physical).

HTT * Hyperthreading enabled

CET * Supports Control Flow Enforcement Technology

Kernel CET - Kernel-mode CET Enabled

User CET * User-mode CET Allowed

X64 * Supports 64-bit mode

SMX - Supports Intel trusted execution

SKINIT - Supports AMD SKINIT

SGX - Supports Intel SGX

NX * Supports no-execute page protection

SMEP * Supports Supervisor Mode Execution Prevention

SMAP * Supports Supervisor Mode Access Prevention

PAGE1GB * Supports 1 GB large pages

PAE * Supports > 32-bit physical addresses

PAT * Supports Page Attribute Table

PSE * Supports 4 MB pages

PSE36 * Supports > 32-bit address 4 MB pages

PGE * Supports global bit in page tables

SS * Supports bus snooping for cache operations

VME * Supports Virtual-8086 mode

RDWRFSGSBASE * Supports direct GS/FS base access

FPU * Implements i387 floating point instructions

MMX * Supports MMX instruction set

MMXEXT - Implements AMD MMX extensions

3DNOW - Supports 3DNow! instructions

3DNOWEXT - Supports 3DNow! extension instructions

SSE * Supports Streaming SIMD Extensions

SSE2 * Supports Streaming SIMD Extensions 2

SSE3 * Supports Streaming SIMD Extensions 3

SSSE3 * Supports Supplemental SIMD Extensions 3

SSE4a - Supports Streaming SIMDR Extensions 4a

SSE4.1 * Supports Streaming SIMD Extensions 4.1

SSE4.2 * Supports Streaming SIMD Extensions 4.2

AES * Supports AES extensions

AVX * Supports AVX instruction extensions

AVX2 * Supports AVX2 instruction extensions

AVX-512-F - Supports AVX-512 Foundation instructions

AVX-512-DQ - Supports AVX-512 double and quadword instructions

AVX-512-IFAMA - Supports AVX-512 integer Fused multiply-add instructions

AVX-512-PF - Supports AVX-512 prefetch instructions

AVX-512-ER - Supports AVX-512 exponential and reciprocal instructions

AVX-512-CD - Supports AVX-512 conflict detection instructions

AVX-512-BW - Supports AVX-512 byte and word instructions

AVX-512-VL - Supports AVX-512 vector length instructions

FMA * Supports FMA extensions using YMM state

MSR * Implements RDMSR/WRMSR instructions

MTRR * Supports Memory Type Range Registers

XSAVE * Supports XSAVE/XRSTOR instructions

OSXSAVE * Supports XSETBV/XGETBV instructions

RDRAND * Supports RDRAND instruction

RDSEED * Supports RDSEED instruction

CMOV * Supports CMOVcc instruction

CLFSH * Supports CLFLUSH instruction

CX8 * Supports compare and exchange 8-byte instructions

CX16 * Supports CMPXCHG16B instruction

BMI1 * Supports bit manipulation extensions 1

BMI2 * Supports bit manipulation extensions 2

ADX * Supports ADCX/ADOX instructions

DCA - Supports prefetch from memory-mapped device

F16C * Supports half-precision instruction

FXSR * Supports FXSAVE/FXSTOR instructions

FFXSR - Supports optimized FXSAVE/FSRSTOR instruction

MONITOR * Supports MONITOR and MWAIT instructions

MOVBE * Supports MOVBE instruction

ERMSB * Supports Enhanced REP MOVSB/STOSB

PCLMULDQ * Supports PCLMULDQ instruction

POPCNT * Supports POPCNT instruction

LZCNT * Supports LZCNT instruction

SEP * Supports fast system call instructions

LAHF-SAHF * Supports LAHF/SAHF instructions in 64-bit mode

HLE - Supports Hardware Lock Elision instructions

RTM - Supports Restricted Transactional Memory instructions

DE * Supports I/O breakpoints including CR4.DE

DTES64 - Can write history of 64-bit branch addresses

DS - Implements memory-resident debug buffer

DS-CPL - Supports Debug Store feature with CPL

PCID * Supports PCIDs and settable CR4.PCIDE

INVPCID * Supports INVPCID instruction

PDCM * Supports Performance Capabilities MSR

RDTSCP * Supports RDTSCP instruction

TSC * Supports RDTSC instruction

TSC-DEADLINE * Local APIC supports one-shot deadline timer

TSC-INVARIANT * TSC runs at constant rate

xTPR * Supports disabling task priority messages

EIST * Supports Enhanced Intel Speedstep

ACPI * Implements MSR for power management

TM * Implements thermal monitor circuitry

TM2 * Implements Thermal Monitor 2 control

APIC * Implements software-accessible local APIC

x2APIC * Supports x2APIC

CNXT-ID - L1 data cache mode adaptive or BIOS

MCE * Supports Machine Check, INT18 and CR4.MCE

MCA * Implements Machine Check Architecture

PBE * Supports use of FERR#/PBE# pin

PSN - Implements 96-bit processor serial number

HTT * Hyperthreading

PREFETCHW * PrefetchW instruction support

HYPERVISOR * Hypervisor is present

VMX - Supports Intel hardware-assisted virtualization

EPT - Supports Intel extended page tables (SLAT)

URG - Supports Intel unrestricted guest

Logical to Physical Processor Map:

**------------ Physical Processor 0 (Hyperthreaded)

--*----------- Physical Processor 1

---*---------- Physical Processor 2

----*--------- Physical Processor 3

-----*-------- Physical Processor 4

------*------- Physical Processor 5

-------*------ Physical Processor 6

--------*----- Physical Processor 7

---------*---- Physical Processor 8

----------**-- Physical Processor 9 (Hyperthreaded)

------------*- Physical Processor 10

-------------* Physical Processor 11

Logical Processor to Socket Map:

************** Socket 0

Logical Processor to NUMA Node Map:

************** NUMA Node 0

No NUMA nodes.

Logical Processor to Cache Map:

**------------ Data Cache 0, Level 1, 48 KB, Assoc 12, LineSize 64

**------------ Instruction Cache 0, Level 1, 64 KB, Assoc 16, LineSize 64

**------------ Unified Cache 0, Level 2, 2 MB, Assoc 16, LineSize 64

************-- Unified Cache 1, Level 3, 12 MB, Assoc 12, LineSize 64

--*----------- Data Cache 1, Level 1, 32 KB, Assoc 8, LineSize 64

--*----------- Instruction Cache 1, Level 1, 64 KB, Assoc 8, LineSize 64

--****-------- Unified Cache 2, Level 2, 2 MB, Assoc 16, LineSize 64

---*---------- Data Cache 2, Level 1, 32 KB, Assoc 8, LineSize 64

---*---------- Instruction Cache 2, Level 1, 64 KB, Assoc 8, LineSize 64

----*--------- Data Cache 3, Level 1, 32 KB, Assoc 8, LineSize 64

----*--------- Instruction Cache 3, Level 1, 64 KB, Assoc 8, LineSize 64

-----*-------- Data Cache 4, Level 1, 32 KB, Assoc 8, LineSize 64

-----*-------- Instruction Cache 4, Level 1, 64 KB, Assoc 8, LineSize 64

------*------- Data Cache 5, Level 1, 32 KB, Assoc 8, LineSize 64

------*------- Instruction Cache 5, Level 1, 64 KB, Assoc 8, LineSize 64

------****---- Unified Cache 3, Level 2, 2 MB, Assoc 16, LineSize 64

-------*------ Data Cache 6, Level 1, 32 KB, Assoc 8, LineSize 64

-------*------ Instruction Cache 6, Level 1, 64 KB, Assoc 8, LineSize 64

--------*----- Data Cache 7, Level 1, 32 KB, Assoc 8, LineSize 64

--------*----- Instruction Cache 7, Level 1, 64 KB, Assoc 8, LineSize 64

---------*---- Data Cache 8, Level 1, 32 KB, Assoc 8, LineSize 64

---------*---- Instruction Cache 8, Level 1, 64 KB, Assoc 8, LineSize 64

----------**-- Data Cache 9, Level 1, 48 KB, Assoc 12, LineSize 64

----------**-- Instruction Cache 9, Level 1, 64 KB, Assoc 16, LineSize 64

----------**-- Unified Cache 4, Level 2, 2 MB, Assoc 16, LineSize 64

------------*- Data Cache 10, Level 1, 32 KB, Assoc 8, LineSize 64

------------*- Instruction Cache 10, Level 1, 64 KB, Assoc 8, LineSize 64

------------** Unified Cache 5, Level 2, 2 MB, Assoc 16, LineSize 64

-------------* Data Cache 11, Level 1, 32 KB, Assoc 8, LineSize 64

-------------* Instruction Cache 11, Level 1, 64 KB, Assoc 8, LineSize 64

Logical Processor to Group Map:

************** Group 0

Coreinfo (3 MB). Indítsa el most a Sysinternals Live-ből.

Coreinfo (3 MB). Indítsa el most a Sysinternals Live-ből.

Fut:

- Ügyfél: Windows 11 vagy újabb.

- Kiszolgáló: Windows Server 2016 és újabb.