Menyiapkan perangkat keras untuk siaga modern

Pada entri ke siaga modern, komponen perangkat keras harus disiapkan untuk melakukan transisi ke operasi berdaya rendah. Setelah komponen dan aplikasi perangkat lunak disiapkan untuk operasi berdaya rendah, komponen perangkat keras, termasuk driver perangkat lunak mereka, harus sama-sama disiapkan untuk operasi berdaya rendah.

Sisa artikel ini menjelaskan cara menyiapkan perangkat di luar dan di dalam System on a Chip (SoC) untuk beroperasi dalam mode berdaya rendah setelah platform perangkat keras memasuki siaga.

Transisi perangkat keras ke mode daya rendah

Semua perangkat di luar SoC dan di dalam SoC harus memasuki mode berdaya rendah untuk mencapai masa pakai baterai yang lama selama tidur. Setelah platform perangkat keras tidur, perangkat di platform beralih ke mode berdaya rendah dalam proses tertib yang dimulai dengan perangkat di luar SoC.

Pertama, semua perangkat di luar SoC atau silikon inti harus memasuki mode daya rendah. Mode daya mungkin status menganggur berpagar jam—misalnya, menempatkan pengontrol sentuh yang terpasang I²C dalam mode tidur. Atau, mode daya mungkin berpagar daya, status 0 watt yang disebut D3cold. Kamera web yang terpasang USB akan sering beralih ke D3cold selama siaga modern. Untuk informasi selengkapnya, lihat Mendukung D3cold untuk Perangkat USB.

Setiap kelas perangkat dan bus koneksi memiliki terminologi dan persyaratannya sendiri untuk transisi perangkat ke mode daya terendah. Namun, sangat penting bahwa perancang sistem merencanakan mode operasi berdaya rendah untuk setiap perangkat di platform selama siaga modern. Masa pakai baterai sistem dan kemampuan untuk menempatkan SoC itu sendiri dalam mode daya rendah tergantung pada manajemen daya yang benar dari setiap perangkat di luar SoC itu sendiri.

Selanjutnya, perangkat jaringan dan radio ditempatkan dalam mode berdaya rendah untuk tidur. Selama tidur, perangkat ini sering kali masih memiliki daya yang diterapkan untuk mempertahankan konektivitas dan diperlukan untuk membangunkan SoC jika perlu. Komunikasi dan perangkat radio biasanya memasuki status daya rendah D2/D3, meskipun entri ke setiap status khusus kelas perangkat dan khusus bus.

Setelah semua perangkat di luar SoC, termasuk perangkat komunikasi, telah dimatikan, pengontrol host pada SoC akan dimatikan. Hampir setiap SoC memiliki pengontrol host USB, I²C, GPIO, SDIO, dan UART. Masing-masing komponen pada SoC ini harus dimatikan agar SoC memasuki mode berdaya rendah.

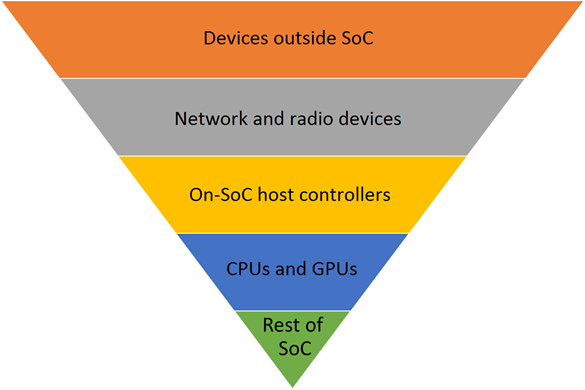

Proses untuk menyiapkan perangkat keras untuk daya rendah selama tidur dapat divisualisasikan sebagai piramida terbalik, seperti yang ditunjukkan pada diagram berikut. Daya terendah dicapai ketika seluruh chip SoC dimatikan, tetapi ini dapat terjadi hanya setelah setiap set perangkat di atasnya di piramida telah dimatikan.

Mematikan perangkat di luar SoC

Setiap perangkat di luar chip SoC harus memasuki mode berdaya rendah untuk dua tujuan utama:

- Kurangi konsumsi daya perangkat.

- Izinkan SoC itu sendiri untuk mematikan dengan memungkinkan pengontrol host on-SoC, tempat perangkat terhubung, untuk mematikan.

Metode untuk mematikan setiap perangkat di luar SoC bervariasi menurut kelas perangkat dan bus yang terpasang.

Beberapa perangkat di luar SoC ditempatkan dalam status 0 watt, tanpa daya yang digunakan yang disebut D3cold. Perangkat umum untuk D3cold mencakup kamera dan sensor. Driver harus menyimpan status register perangkat lalu transisi perangkat ke status daya D3. Daya akan dihapus oleh firmware ACPI dengan beralih ke garis GPIO atau mematikan rel daya dari manajemen daya IC (PMIC).

Beberapa perangkat di luar SoC ditempatkan dalam mode diam berdaya rendah di mana status register dipertahankan, atau perangkat mungkin hanya berjaga-jarum jam. Misalnya, banyak pengontrol sentuh memiliki status berpagar jam yang mengonsumsi kurang dari 1 miliwatt daya. Keuntungan umum untuk menggunakan status berjaga jam adalah waktu hidup yang lebih cepat dan biaya yang lebih rendah dengan tidak harus menghubungkan perangkat ke rel daya yang dapat dialihkan.

Umumnya, setiap perangkat di luar SoC harus mampu memasuki mode berdaya rendah yang mengonsumsi daya kurang dari 1 miliwatt. Perangkat yang tidak dapat mencapai tingkat daya ini dengan status berpagar jam internal harus mengimplementasikan power-gating melalui D3cold.

Perangkat jaringan dan radio adalah pengecualian penting untuk pedoman 1 miliwatt. Perangkat jaringan dan radio mungkin memerlukan lebih banyak daya untuk mempertahankan koneksi ke jaringan atau mendengarkan perangkat nirkabel. Beberapa perancang sistem mengacu pada transisi status daya ini sebagai runtime D3 (RTD3).

Manajemen daya yang diarahkan untuk perangkat PCIe

Kartu PCIe di luar SoC harus mengaktifkan mekanisme manajemen daya yang diarahkan yang disebut Device-S4 untuk memastikan bahwa mereka dapat memasuki mode daya rendah. Tanpa Device-S4, jika pengguna menyambungkan perangkat ke PCIe Root Port dengan slot yang dapat diakses pengguna pada sistem Modern Standby desktop, dan driver untuk perangkat tidak mendukung runtime D3 (RTD3), perangkat PCIe dapat mencegah sistem memasuki DRIPS. Untuk menghindari masalah ini, OEM harus memilih Port Root perangkat PCIe ke Device-S4. Agar Perangkat-S4 terlibat untuk perangkat PCIe tertentu, persyaratan berikut harus dipenuhi:

- Port Akar PCIe induk untuk perangkat harus ditentukan sebagai batasan untuk DRIPS.

- Port Akar PCIe induk harus menerapkan reset perangkat mendasar untuk semua anak di hilir Port Akar setelah transisi D0-D3> Port Root dan deassert fundamental device reset ke anak-anak tersebut setelah transisi D3-D0>. Untuk informasi selengkapnya tentang reset dasar PCIe, silakan lihat Bagian 6.6.1 dari Spesifikasi Pangkalan Ekspres PCI. Penerapan reset dasar dapat disediakan oleh mekanisme ACPI tambahan. Untuk informasi lebih lanjut, silakan merujuk ke panduan ini tentang PCI Power Management. Untuk menunjukkan bahwa platform mematuhi persyaratan reset dasar ini, firmware harus menentukan _DSD dengan dukungan untuk GUID {FDF06FAD-F744-4451-BB64-ECD792215B10}. Tanpa ini, DRIPS yang diarahkan tidak akan dipicu untuk perangkat di bawah Port Akar PCIe tersebut. Untuk informasi selengkapnya, lihat Acpi Device Specific Data (_DSD) untuk PCIe Root Ports.

- Sumber daya daya harus unik untuk Port Akar PCIe tertentu, yaitu tidak dibagikan dengan Port Akar lainnya.

Harap dicatat bahwa kartu PCIe yang memerlukan Modul Dukungan Kompatibilitas (CSM) tidak akan berfungsi dalam sistem Siaga Modern. CSM tidak didukung dalam BIOS pada sistem Modern Standby karena persyaratan Boot Aman UEFI. Untuk informasi lebih lanjut, silakan merujuk ke Spesifikasi Program Kompatibilitas Perangkat Keras Windows.

Untuk informasi selengkapnya tentang manajemen daya untuk kelas perangkat tertentu, perancang sistem didorong untuk meninjau Manajemen daya khusus perangkat untuk siaga modern, serta dokumentasi khusus perangkat di Microsoft Collaborate.

Mematikan perangkat jaringan

Mematikan jaringan dan perangkat radio adalah bagian penting lain dari menyiapkan perangkat keras untuk operasi berdaya rendah selama tidur. Perangkat jaringan dan radio berbeda dari perangkat lain di luar SoC karena harus tetap menyala dengan daya yang diterapkan untuk mendengarkan peristiwa menarik dan membangunkan SoC. Misalnya, radio Wi-Fi harus mampu mendengarkan paket yang cocok dengan pola WoL dan membangunkan SoC saat paket yang cocok terdeteksi.

Perangkat jaringan transisi Windows ke status D2/D3 selama tidur jika diharapkan untuk membangunkan SoC. Tumpukan jaringan Windows akan mengonfigurasi pola WoL dan offload protokol sebelum menempatkan perangkat dalam status D2/D3 berdaya rendah. Semua perangkat jaringan, termasuk Wi-Fi, broadband seluler (MBB), dan Ethernet kabel, harus mampu memasuki status D2/D3 selama tidur. Jika perangkat jaringan tidak diperlukan untuk membangunkan sistem, Windows akan mentransisikan perangkat ke status D3. Perangkat jaringan dapat ditempatkan dalam status D3 jika pengguna telah mengaktifkan mode pesawat atau menonaktifkan perangkat jaringan tertentu.

Setiap perangkat memiliki metode fisik yang berbeda untuk membangunkan SoC dari mode daya terendahnya. Perangkat jaringan pada SDIO atau UART diharapkan memberi sinyal garis GPIO untuk membangunkan SoC. Perangkat jaringan yang terhubung melalui USB atau HSIC diharapkan menggunakan sinyal resume USB in-band untuk membangunkan SoC. Perangkat jaringan pada bus PCI atau PCIe diharapkan menggunakan sinyal PME in-band untuk membangunkan SoC.

Selain itu, perangkat radio, seperti bluetooth atau perangkat komunikasi near-field (NFC), diperkirakan akan beralih ke status D2 jika pengguna telah menyalakan radio untuk perangkat ini. Dalam status D2, radio Bluetooth mendengarkan peristiwa input dari tikus dan keyboard yang dipasangkan. Jika peristiwa input terdeteksi, radio Bluetooth akan mengalihkan garis GPIO yang terhubung ke SoC, yang menyebabkan SoC bangun dari mode daya rendahnya.

Setiap jaringan atau perangkat radio memiliki implementasi daya sendiri untuk siaga modern. Perancang sistem didorong untuk membaca dokumen khusus kelas perangkat di situs web Microsoft Collaborate.

Mematikan pengontrol host SoC

Setelah semua perangkat di luar SoC, termasuk perangkat jaringan dan radio, telah dimatikan, pengontrol host tempat perangkat terpasang harus mati. Pengontrol host umum termasuk USB, PCI, SDIO, GPIO, dan I²C.

Driver untuk setiap pengontrol host dapat mematikan perangkat keras hanya setelah setiap perangkat yang terhubung ke pengontrol host telah mati. Contoh umumnya adalah pengontrol host USB. Pengontrol host USB dapat mati hanya setelah semua perangkat USB yang terhubung ke sana telah memasuki status ditangguhkan selektif. Jika pengontrol host USB memiliki tetikus USB dan keyboard yang terhubung, pengontrol host dapat mematikan hanya setelah mouse dan keyboard mati. Jika mouse atau keyboard tetap menyala, pengontrol host USB juga tetap menyala.

Semua pengontrol host pada SoC harus mati untuk tidur agar SoC itu sendiri dapat mati. Inilah sebabnya mengapa sangat penting bahwa setiap perangkat melakukan manajemen daya perangkat. SoC itu sendiri hanya dapat mematikan ketika setiap pengontrol host telah dimatikan. Pengontrol host dapat mati hanya setelah semua perangkat yang terhubung ke mereka telah dimatikan.

Mematikan CPU dan GPU

Dalam hal manajemen daya, CPU dan GPU pada chip SoC berbeda dari perangkat lain. CPU dan GPU mati sebagai bagian dari mematikan SoC itu sendiri dan dapat dimatikan setiap kali tidak ada aktivitas perangkat lunak yang ditargetkan kepada mereka.

Sebagian besar aktivitas perangkat lunak pada sistem akan dihentikan melalui tahap persiapan yang dirinci dalam Menyiapkan perangkat lunak untuk siaga modern. Aplikasi Microsoft Store akan dijeda sebagai bagian dari fase PLM. Aplikasi desktop akan dijeda sebagai bagian dari menyelesaikan fase DAM. Satu-satunya aktivitas CPU yang tersisa setelah platform memasuki fase ketahanan adalah operasi Windows yang menganggur itu sendiri. Demikian pula, ada sedikit aktivitas GPU karena semua aplikasi telah dijeda dan layar dimatikan.

Windows terus mengelola status daya CPU pada sistem, bahkan ketika layar menyala dan pengguna bekerja dengan PC. Manajemen status daya CPU yang sama menempatkan CPU dalam mode daya rendah selama tidur. Ketika semua CPU berada dalam mode daya rendah dan semua pengontrol host pada SoC telah dimatikan, SoC itu sendiri dapat dimatikan.

Mematikan SoC

Ketika semua pengontrol host individu, CPU, dan GPU pada SoC telah dimatikan, Windows akan menentukan apakah aman untuk mematikan seluruh SoC itu sendiri. Vendor SoC menyediakan plug-in mesin daya (PEP) untuk memberi tahu Windows ketika semua status pada SoC telah disimpan sehingga SoC siap untuk memasuki mode daya rendah. Untuk SoC berbasis Intel, PEP disediakan kotak masuk.

Setiap vendor SoC memiliki implementasi yang berbeda dari status daya rendah di seluruh SoC. Status-status ini biasanya berpagar jam atau berpagar daya status di mana konten memori dipertahankan dalam refresh diri dan sistem dapat dibangunkan oleh timer yang dapat diprogram dan sejumlah kecil pin GPIO yang mengonsumsi daya yang sangat sedikit. Windows mengacu pada status daya SoC terendah sebagai status platform diam runtime terdalam (DRIPS).

Status DRIPS selalu memiliki karakteristik berikut:

- DRIPS adalah status konsumsi daya terendah untuk SoC di mana memori dipertahankan dalam mode refresh mandiri.

- DRIPS memungkinkan SoC untuk bangun pada peristiwa dari perangkat jaringan, radio, dan input.

- Tidak ada kode CPU yang diizinkan untuk dijalankan selama status DRIPS.

- Ketika SoC berada dalam status DRIPS, platform mengonsumsi daya sekecil mungkin selama tidur (dengan pengecualian varians dalam konsumsi daya yang disebabkan oleh jaringan dan perangkat radio).