Catatan

Akses ke halaman ini memerlukan otorisasi. Anda dapat mencoba masuk atau mengubah direktori.

Akses ke halaman ini memerlukan otorisasi. Anda dapat mencoba mengubah direktori.

Di beberapa platform, prosesor dan pengontrol DMA sistem (atau adaptor DMA master bus) menunjukkan anomali koherensi cache. Panduan berikut memungkinkan driver yang menggunakan antarmuka operasi DMA versi 1 atau 2 (lihat DMA_OPERATIONS) untuk mempertahankan status cache yang koheren di semua arsitektur prosesor yang didukung, termasuk arsitektur yang tidak berisi perangkat keras untuk secara otomatis menerapkan koherensi cache.

Catatan Panduan dalam topik ini hanya berlaku untuk driver yang menggunakan antarmuka operasi DMA versi 1 dan 2. Driver yang menggunakan versi 3 antarmuka ini harus mengikuti serangkaian pedoman yang berbeda. Untuk informasi selengkapnya, lihat Versi 3 antarmuka operasi DMA.

Untuk menjaga integritas data selama operasi DMA, driver tingkat terendah harus mengikuti panduan ini

Panggil KeFlushIoBuffers sebelum memulai operasi transfer untuk mempertahankan konsistensi antara data yang mungkin di-cache di prosesor dan data dalam memori.

Jika driver memanggil AllocateCommonBuffer dengan parameter CacheEnabled diatur ke TRUE, driver harus memanggil KeFlushIoBuffers sebelum memulai operasi transfer ke/dari buffernya.

Panggil FlushAdapterBuffers di akhir setiap proses transfer perangkat untuk memastikan bahwa byte yang tersisa dalam buffer dari pengontrol DMA sistem sudah dituliskan ke dalam memori atau ke perangkat bawahan.

Atau, panggil FlushAdapterBuffers di akhir setiap operasi transfer untuk IRP tertentu untuk memastikan semua data telah dibaca ke dalam memori sistem atau ditulis ke perangkat DMA master bus.

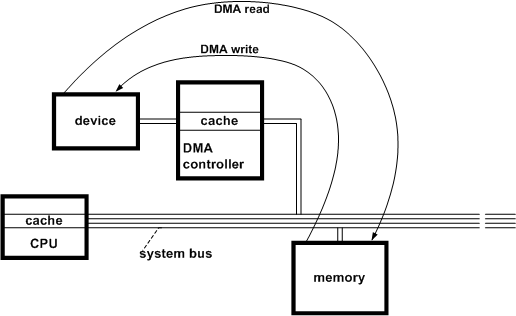

Gambar berikut menunjukkan mengapa penting untuk menghapus cache prosesor sebelum operasi baca atau tulis menggunakan DMA jika prosesor host dan pengontrol DMA tidak secara otomatis mempertahankan koherensi cache.

Operasi baca atau tulis DMA asinkron mengakses data dalam memori, bukan di cache prosesor. Kecuali cache ini telah dibersihkan dengan memanggil KeFlushIoBuffers tepat sebelum dibaca, data yang ditransfer ke memori sistem oleh operasi DMA dapat ditimpa dengan data kedaluwarsa jika cache prosesor dihapus nanti. Kecuali cache prosesor telah dibersihkan dengan memanggil KeFlushIoBuffers tepat sebelum menulis, data dalam cache ini mungkin lebih up-to-date daripada salinan dalam memori.

KeFlushIoBuffers tidak melakukan apa pun jika prosesor dan pengontrol DMA dapat diandalkan untuk mempertahankan koherensi cache, jadi panggilan ke rutinitas dukungan ini hampir tidak memiliki overhead di platform seperti itu.

Seperti yang ditunjukkan juga pada gambar sebelumnya, pengontrol DMA, yang diwakili oleh objek adaptor, dapat memiliki buffer internal. Pengontrol DMA semacam itu dapat mentransfer data yang di-cache dalam gugus ukuran tetap, biasanya delapan atau lebih byte sekaligus. Selain itu, pengontrol DMA ini dapat menunggu hingga buffer internal mereka penuh sebelum setiap operasi transfer.

Pertimbangkan kasus driver tingkat terendah yang menggunakan DMA subordinat untuk membaca data dalam gugus berukuran variabel atau dalam gugus ukuran tetap yang bukan kelipatan integral dari ukuran cache pengontrol DMA sistem. Kecuali driver ini memanggil FlushAdapterBuffers di akhir setiap transfer perangkat, itu tidak dapat memastikan kapan setiap byte yang diminta driver benar-benar akan ditransfer.

Pengemudi perangkat DMA bus-master juga harus memanggil FlushAdapterBuffers di akhir setiap operasi transfer untuk IRP guna memastikan bahwa semua data telah ditransfer ke dalam memori sistem atau keluar ke perangkat.

FlushAdapterBuffers mengembalikan Boolean, nilai yang menunjukkan apakah operasi flush yang diminta berhasil. Driver dapat menggunakan nilai ini untuk menentukan cara mengatur blok status I/O saat menyelesaikan IRP untuk operasi baca atau tulis DMA.