Catatan

Akses ke halaman ini memerlukan otorisasi. Anda dapat mencoba masuk atau mengubah direktori.

Akses ke halaman ini memerlukan otorisasi. Anda dapat mencoba mengubah direktori.

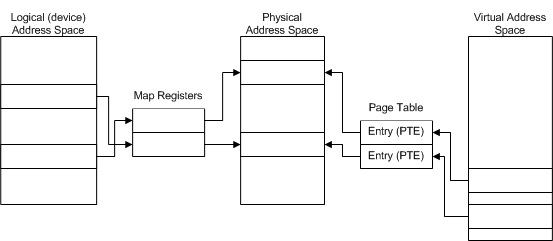

Driver yang melakukan DMA menggunakan tiga ruang alamat yang berbeda, seperti yang ditunjukkan pada gambar berikut.

Pada platform Windows apa pun, driver memiliki akses ke ruang alamat virtual lengkap yang didukung oleh prosesor. Pada prosesor 32-bit, ruang alamat virtual mewakili empat gigabyte. CPU menerjemahkan alamat di ruang alamat virtual ke alamat di ruang alamat fisik sistem dengan menggunakan tabel halaman. Setiap entri tabel halaman (PTE) memetakan satu halaman memori virtual ke halaman memori fisik, yang menghasilkan operasi paging bila diperlukan. MDL (daftar deskriptor memori) menyediakan pemetaan serupa untuk buffer yang terkait dengan operasi DMA driver.

Perangkat bervariasi dalam kemampuannya untuk mengakses ruang alamat virtual lengkap sistem. Perangkat menggunakan alamat dalam ruang alamat (perangkat) logis. Setiap HAL menggunakan register peta untuk menerjemahkan perangkat atau alamat logis ke alamat fisik (lokasi dalam RAM fisik). Untuk perangkat keras perangkat, map register melakukan fungsi yang sama dengan yang dilakukan MDL (dan tabel halaman) untuk perangkat lunak (driver): mereka menerjemahkan alamat ke memori fisik.

Karena ruang alamat ini diatur secara terpisah, driver tidak dapat menggunakan penunjuk di ruang alamat virtual untuk mengakses lokasi dalam memori fisik, dan sebaliknya. Driver harus terlebih dahulu menerjemahkan alamat virtual ke alamat fisik. Demikian pula, perangkat tidak dapat menggunakan alamat logis untuk mengakses memori fisik secara langsung. Perangkat harus terlebih dahulu menerjemahkan alamat.

HAL harus menyiapkan objek adaptor yang mendukung DMA untuk berbagai perangkat DMA dan bus I/O di komputer yang berbeda. Misalnya, sebagian besar pengontrol ISA DMA, perangkat subordinat, dan perangkat master bus memiliki garis alamat yang tidak memadai untuk mengakses ruang alamat fisik sistem empat gigabyte penuh dari prosesor 32-bit (atau alamat fisik sistem 64 gigabyte dari prosesor x86 yang berjalan dalam mode PAE 36-bit). Sebaliknya, perangkat PCI DMA umumnya memiliki lebih dari cukup baris alamat untuk mengakses ruang alamat fisik sistem penuh dalam prosesor 32-bit. Oleh karena itu, setiap HAL menyediakan pemetaan antara rentang alamat logis yang dapat diakses perangkat DMA dan rentang alamat fisik setiap komputer.

Setiap objek adaptor dikaitkan dengan satu atau beberapa register peta, tergantung pada jumlah data yang akan ditransfer dan jumlah memori yang tersedia. Selama transfer DMA, HAL menggunakan setiap register peta untuk memetakan halaman logis yang dapat diakses oleh perangkat ke halaman memori fisik di CPU. Akibatnya, daftar peta memberikan dukungan sebar/pengumpulan untuk driver yang menggunakan DMA, terlepas dari apakah perangkat mereka memiliki kemampuan sebar/pengumpulan.

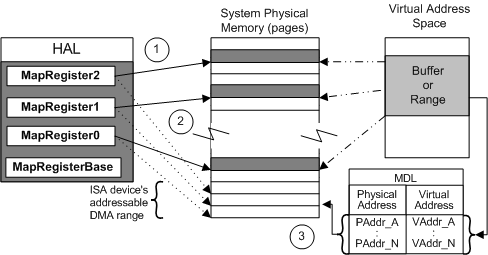

Gambar berikut mengilustrasikan pemetaan alamat fisik ke logis seperti itu untuk driver perangkat ISA DMA yang tidak memiliki kemampuan sebar/kumpulkan.

Gambar sebelumnya memperlihatkan jenis pemetaan berikut:

Setiap register peta memetakan rentang alamat fisik (ditunjukkan oleh garis solid) ke alamat logis urutan rendah (garis putus-putus) untuk perangkat ISA DMA.

Di sini, tiga register peta digunakan untuk menghubungkan tiga rentang halaman data pada memori fisik sistem ke tiga rentang alamat logis tingkat rendah berukuran halaman untuk perangkat ISA DMA.

Perangkat ISA menggunakan alamat logis yang dipetakan untuk mengakses memori sistem selama operasi DMA.

Untuk perangkat PCI DMA yang sebanding, tiga register peta juga akan digunakan untuk tiga rentang data berukuran halaman. Namun, rentang alamat logis yang dipetakan belum tentu akan identik dengan rentang alamat fisik yang sesuai, sehingga perangkat PCI juga akan menggunakan alamat logis untuk mengakses memori sistem.

Setiap entri di MDL memetakan lokasi di ruang alamat virtual ke alamat fisik.

Perhatikan korespondensi antara register peta dan entri virtual-ke-fisik di MDL:

Setiap peta register dan setiap entri virtual dalam MDL memetakan paling banyak satu halaman fisik penuh data untuk operasi transfer DMA.

Setiap pencatatan peta dan setiap entri virtual dalam MDL mungkin memetakan kurang dari satu halaman penuh data. Misalnya, entri virtual awal dalam MDL dapat memetakan ke offset dari batas halaman fisik, seperti yang ditunjukkan sebelumnya dalam gambar Pemetaan Alamat Fisik, Logis, dan Virtual .

Setiap peta mendaftar dan setiap entri virtual dalam peta MDL, minimal satu byte.

Dalam IRP yang meminta operasi baca atau tulis, setiap entri virtual dalam MDL yang tidak terlihat oleh driver di Irp->MdlAddress mewakili batas halaman dalam memori fisik sistem untuk buffer pengguna. Demikian pula, setiap register peta tambahan yang diperlukan untuk transfer DMA tunggal mewakili batas halaman dalam rentang alamat logis yang dapat diakses perangkat yang di alias ke memori fisik sistem.

Pada setiap platform Windows, setiap objek adaptor memiliki satu set register pemetaan terkait yang terletak di alamat dasar khusus platform (dan tidak dapat diakses oleh driver). Dari sudut pandang pengemudi, basis register peta yang ditunjukkan pada gambar yang mengilustrasikan pemetaan alamat untuk sampel perangkat ISA DMA adalah pengendali untuk sekumpulan register peta yang dapat berupa register perangkat keras dalam chip, dalam pengontrol DMA sistem, sebagai adaptor master bus, atau bahkan bisa menjadi register virtual yang dibuat HAL dalam memori sistem.

Jumlah register peta yang tersedia dengan objek adaptor dapat bervariasi untuk perangkat dan platform Windows yang berbeda. Misalnya, HAL dapat membuat lebih banyak register peta tersedia untuk driver yang menggunakan DMA sistem pada beberapa platform daripada pada platform lain karena pengontrol DMA pada platform Windows yang berbeda memiliki kemampuan yang berbeda.