Notitie

Voor toegang tot deze pagina is autorisatie vereist. U kunt proberen u aan te melden of de directory te wijzigen.

Voor toegang tot deze pagina is autorisatie vereist. U kunt proberen de mappen te wijzigen.

Op deze pagina wordt het IoMmu-model beschreven dat is geïntroduceerd in WDDM 2.0. Zie IOMMU-gebaseerde GPU-isolatie en IOMMU DMA opnieuw toewijzen voor recentere IOMMU-updates.

Overzicht

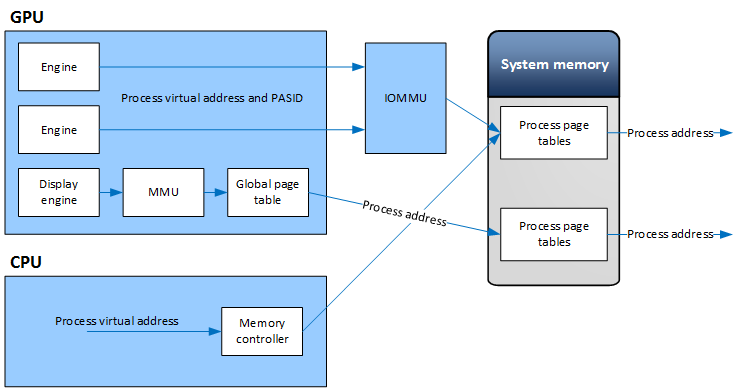

Een Input-Output Memory Management Unit (IOMMU) is een hardwareonderdeel dat een DMA-compatibele I/O-bus verbindt met systeemgeheugen. Het wijst apparaatbare virtuele adressen toe aan fysieke adressen, waardoor het handig is in virtualisatie.

In het WDDM 2.0 IoMmu-model heeft elk proces één virtuele adresruimte:

- Gedeeld tussen de CPU en GPU.

- Beheerd door het geheugenbeheer van het besturingssysteem.

Voor toegang tot geheugen verzendt de GPU een gegevensaanvraag naar een compatibele IOMMU. De aanvraag bevat een gedeeld virtueel adres en een PASID (Process Address Space Identifier ). De IOMMU voert de adresomzetting uit met behulp van de gedeelde paginatabel. Deze actie wordt geïllustreerd in het volgende diagram.

Het stuurprogramma voor kernelmodusweergave (KMD) geeft ondersteuning voor het IoMmu-model weer door de DXGK_VIDMMCAPS::IoMmuSupported caps in te stellen. Wanneer deze vlag is ingesteld, registreert de videogeheugenbeheerder (VidMm) automatisch elk proces met behulp van de GPU met de IOMMU en verkrijgt een PASID voor dat procesadresruimte. De PASID wordt tijdens het maken van het apparaat doorgegeven aan het stuurprogramma.

VidMm wijst primaire toewijzingen toe aan het aperture-segment voordat deze worden weergegeven, zodat de weergavecontroller fysieke toegang heeft tot deze toewijzingen.

In het IoMmu-model blijft het gebruikersmodusdisplaystuurprogramma (UMD) videogeheugen toewijzen voor de GPU met behulp van de Allocate-service van VidMm. Met dit proces kan de UMD het volgende doen:

- Volg het verblijfsmodel.

- Ondersteuning voor het DirectX-model voor het delen van resources.

- Zorg ervoor dat de primaire oppervlakken zichtbaar zijn voor de kernel en worden toegewezen aan een opening voordat ze worden weergegeven.

De UMD beheert volledig het eerste niveau van vertaling (tegelresourceadres naar gedeeld CPU/GPU-adres) in gebruikermodus.