作者:Mark Russinovich

发布时间: 2025 年 12 月 16 日

Coreinfo(3 MB)

Coreinfo(3 MB)

简介

Coreinfo 是一个实用工具,显示逻辑处理器与物理处理器、NUMA 节点和它们所在的套接字之间的映射,以及分配给每个逻辑处理器的缓存。 它使用低级别 Windows API(用户模式和内核模式)直接从作系统检索详细的 CPU 拓扑信息。 命令行版本输出映射到逻辑处理器的表示形式,并用星号标示,例如“*”。 UI 提供了多个专用视图来探索系统 CPU 拓扑的不同方面,包括逻辑核心和物理核心、NUMA 节点、套接字、缓存层次结构和实时性能指标。 Coreinfo 可用于深入了解系统的处理器和缓存拓扑。

安装

将存档提取到一个目录中,然后根据体系结构通过在该目录中键入Coreinfo / Coreinfo64或Coreinfo64a来运行 Coreinfo。 启动 CoreInfoEx / CoreInfoEx64 / CoreInfoEx64a 的 UI 版本。

注意: 某些功能可能需要管理权限才能完成信息检索。

用户界面概述

Coreinfo UI 由多个关键组件组成:

主窗口布局

- 顶部面板:显示系统信息,包括 CPU 名称、体系结构和核心计数

- 导航窗格 (左):提供对不同视图的快速访问

- 内容区域 (中心):显示所选视图的数据和可视化效果

- 详细信息窗格 (底部):选择核心或单元格时显示详细信息

- 设置:访问外观选项和应用程序首选项

主窗口显示完整的 UI 布局, 深色模式

主窗口显示完整的 UI 布局, 深色模式

导航视图

左侧导航窗格提供对六个专用视图的访问权限:

1. 核心视图

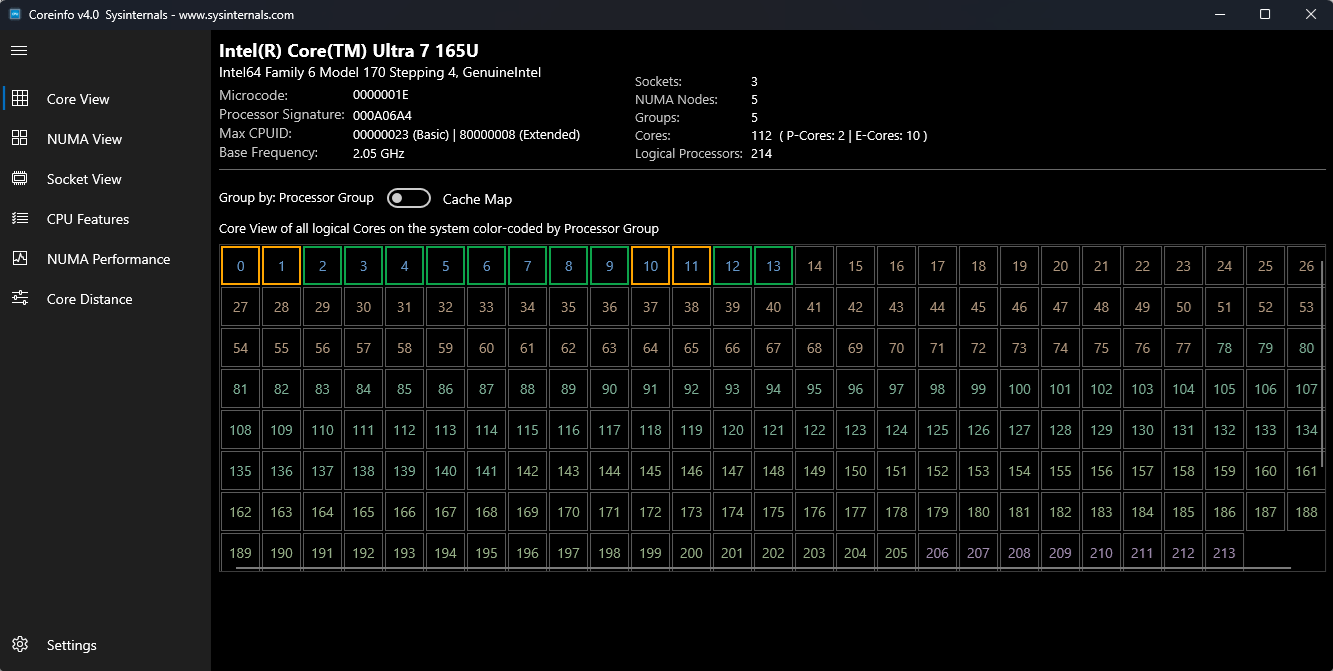

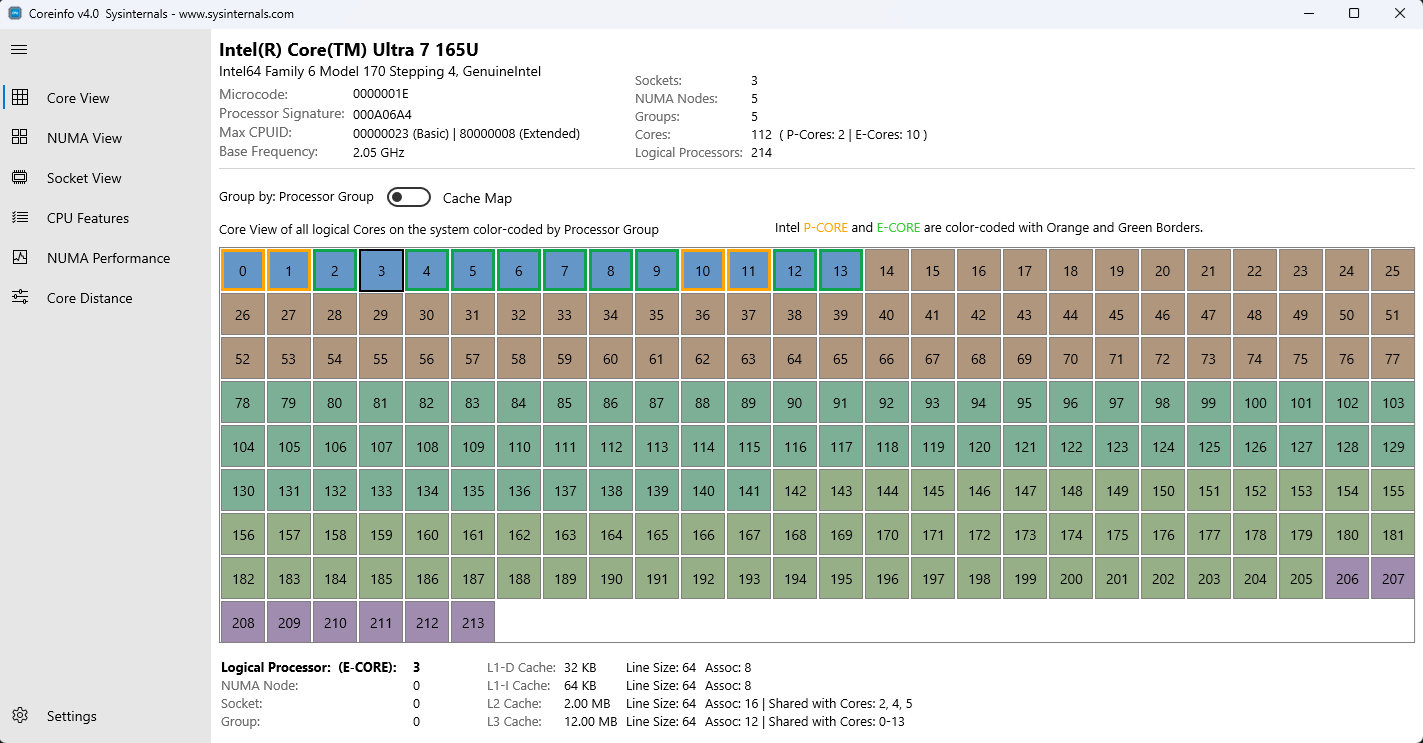

核心视图在网格布局中显示系统中的所有逻辑处理器,显示逻辑核心与其物理资源之间的关系。

功能:

- 网格布局:每个单元格表示逻辑处理器

-

核心类型指示器:

- P 核心(性能核心)- 颜色独特

- E-Core (效率核心) - 颜色不同

- 标准核心 - 默认着色

- 缓存映射切换:在默认视图和缓存层次结构视图之间进行切换

- 交互式选择:单击任意核心以查看底部窗格中的详细信息

显示的信息:

- 逻辑处理器编号

- 核心类型(如果适用为 P-Core/E-Core)

- 关联的缓存级别(L1、L2、L3)

- NUMA 节点分配

- 套接字分配

- 组分配

核心视图以网格布局显示逻辑处理器

核心视图以网格布局显示逻辑处理器

详细信息窗格 (选择核心组件时):

- 处理器掩码和相关性

- 缓存层次结构(数据缓存、指令缓存、统一缓存)

- 缓存大小和关联性

- 缓存行大小

2. NUMA 视图

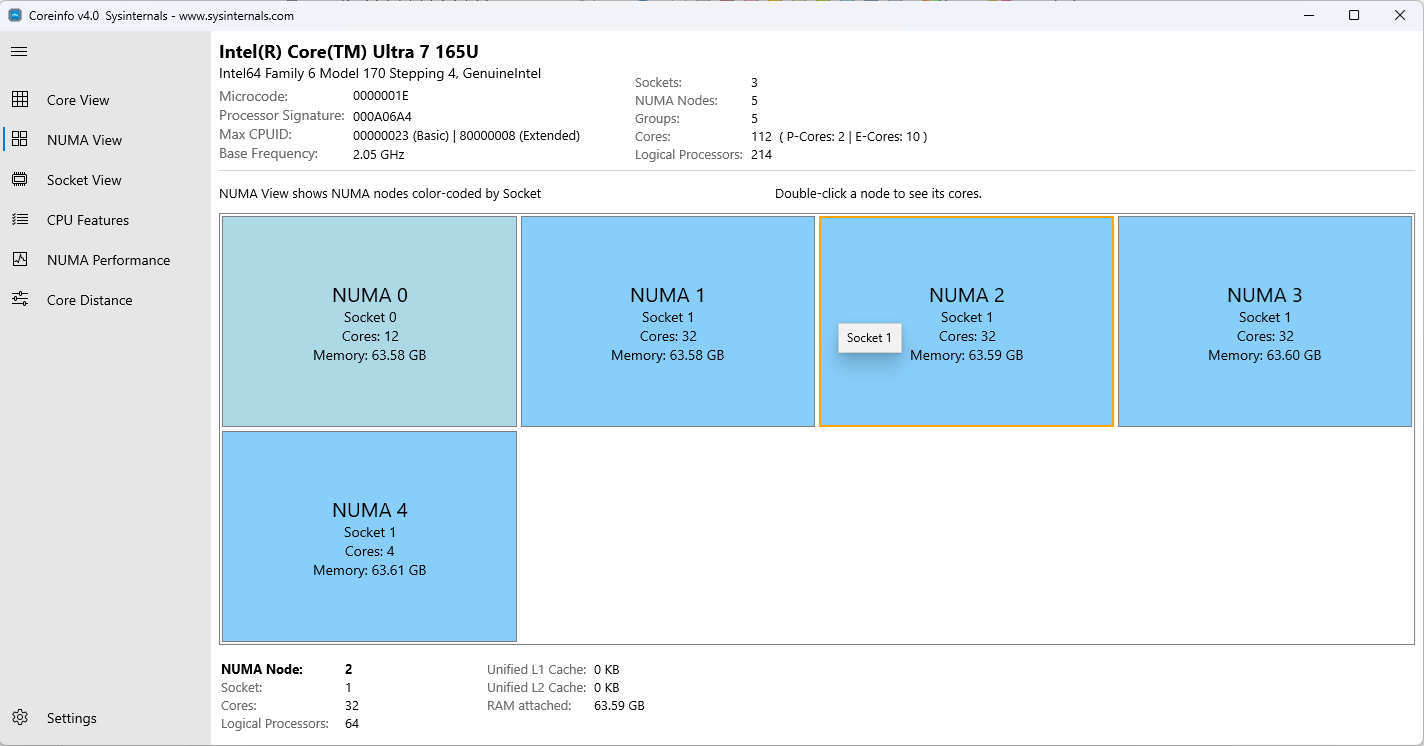

NUMA(非统一内存访问)视图按其 NUMA 节点分配组织核心,使得内存局部性和访问模式更易于理解。

功能:

- 基于节点的架构:按 NUMA 节点分组的核心

- 物理与逻辑核心:显示每个节点的两个计数

- 内存信息:显示每个 NUMA 节点的可用内存

-

交互式导航:

- 单击 NUMA 节点,在底部详细信息窗格中显示其详细信息

- 双击 NUMA 节点,导航到“核心视图”,显示所选 NUMA 节点中的所有核心

- 分层显示:显示 NUMA 节点与核心之间的关系

显示的信息:

- NUMA 节点数

- 每个 NUMA 节点的核心数(物理核心和逻辑核心)

- 每个节点的内存容量

- 跨节点的核心分布

- 效率核心计数(如果适用)

NUMA 视图,显示了按照 NUMA 节点组织的核心

NUMA 视图,显示了按照 NUMA 节点组织的核心

用例:

- 优化内存访问模式

- 理解 NUMA 识别应用程序的性能

- 规划线程/进程放置以实现最佳性能

3. 套接字视图

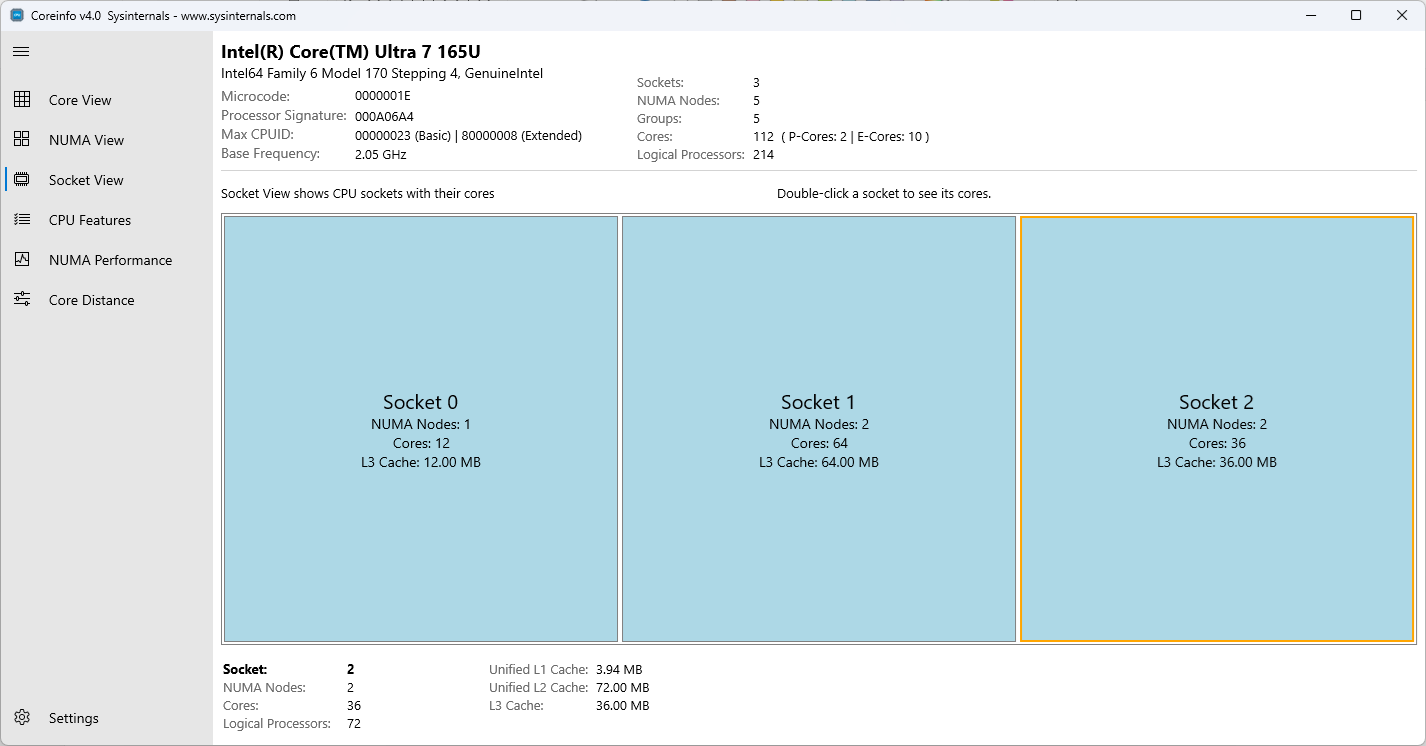

套接字视图显示按物理 CPU 插槽组织的处理器核心,有助于了解多插槽系统和插槽级资源分布。

功能:

- 基于物理插槽的分组:按物理插槽组织的内核

- 套接字信息:套接字计数和核心分发

-

交互式导航:

- 单击套接字,在底部详细信息窗格中显示其详细信息

- 双击套接字以导航到“核心视图”,显示所选套接字中的所有核心

- 缓存共享:可视化哪些核心共享套接字级缓存

显示的信息:

- 物理连接器数量

- 套接字上的核心数(包括物理核心和逻辑核心)

- 套接字级缓存信息

- 每个套接字的 NUMA 节点数

套接字视图显示核心按 CPU 套接字进行组织

套接字视图显示核心按 CPU 套接字进行组织

用例:

- 多路 CPU 插槽系统分析

- 了解跨套接字通信成本

- 在多个插槽服务器中规划工作负载分配

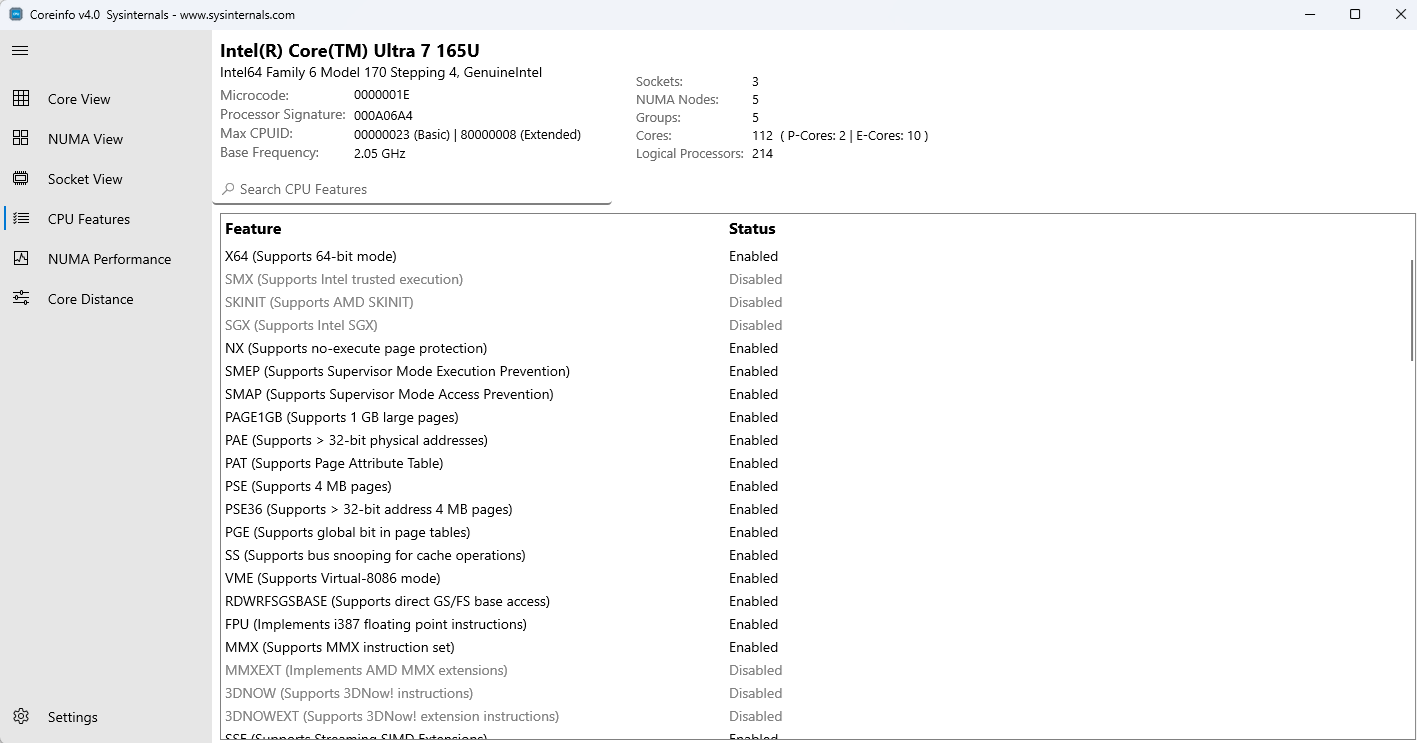

4. CPU 功能视图

CPU 功能视图显示 CPU 支持的处理器功能、指令集扩展和硬件功能的综合列表。

功能:

- 可搜索列表:使用搜索栏快速查找特定 CPU 功能

-

状态指示器:通过颜色标识清晰地指示受支持与不支持的功能

- 支持的功能以普通颜色显示

- 不支持或禁用的功能会灰色显示

-

功能类别:

- 虚拟化(VMX、SVM、虚拟机监控程序)

- 64 位支持 (EM64T, NX)

- 指令集(SSE、AVX、AES 等)

- 电源管理(EIST、ACPI、热)

- 安全功能(SMX、SKINIT)

- 内存功能(PAE、PAT、PSE)

- 调试和监视功能

显示的信息:

- 功能缩写

- 功能状态(支持/不支持)

- 完整功能说明(详细信息窗格中)

CPU 特性视图,显示处理器功能列表

CPU 特性视图,显示处理器功能列表

注意: 某些虚拟化功能(如 VMX、SVM)在运行虚拟机监控程序活动时或从虚拟机内部运行时,可能会错误地报告为不可用。 Coreinfo 必须在没有运行管理程序的系统上执行,才能获得准确的结果。

用例:

- 在部署应用程序之前验证指令集可用性

- 检查虚拟化支持

- 了解处理器生成和功能

- 调试由于缺少 CPU 功能而导致的性能问题

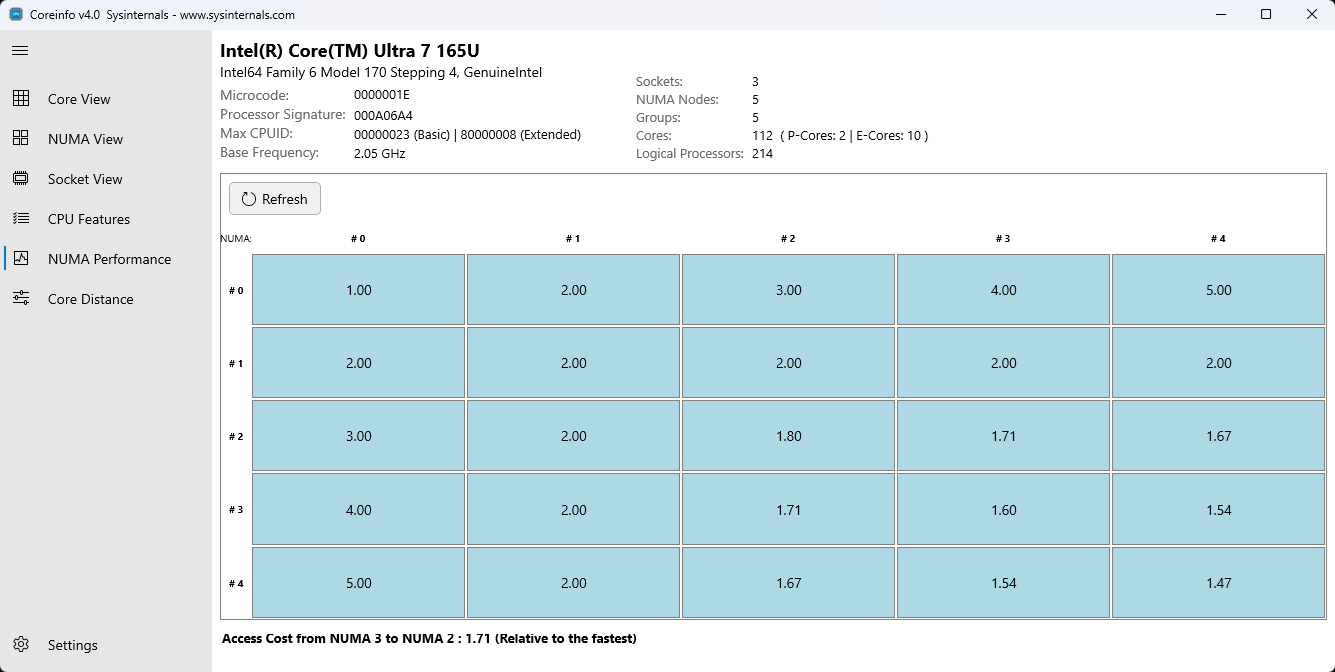

5. NUMA 性能视图

NUMA 性能视图提供网格可视化效果,显示 NUMA 节点之间的内存访问成本,帮助识别 NUMA 系统中的性能瓶颈。

功能:

- 网格可视化:显示 NUMA 节点之间的相对内存访问成本的矩阵

- 交互式矩阵:将鼠标悬停在单元格上以查看详细的性能信息

- Real-Time 更新:通过选择“刷新”按钮动态更新性能数据

- 相对成本显示:显示从不同 NUMA 节点访问内存的相对成本

显示的信息:

- NxN 矩阵,其中 N = NUMA 节点数

- 从源 NUMA 节点(行)到目标 NUMA 节点(列)的内存访问成本

- 显示相对性能成本的数字值

- 对角单元格显示本地内存访问(通常成本最低)

NUMA 性能网格,显示内存访问成本

NUMA 性能网格,显示内存访问成本

了解网格:

- 对角元素:表示本地内存访问(节点访问自己的内存) - 通常是最低值

- 对角线元素:表示具有较高相对成本的远程内存访问

- 对称性:矩阵可能不是完全对称的,因为访问成本可能因方向而异

用例:

- 识别与 NUMA 相关的性能瓶颈

- 优化内存分配策略

- 为 NUMA 系统规划进程/线程固定

- 了解跨节点内存访问处罚

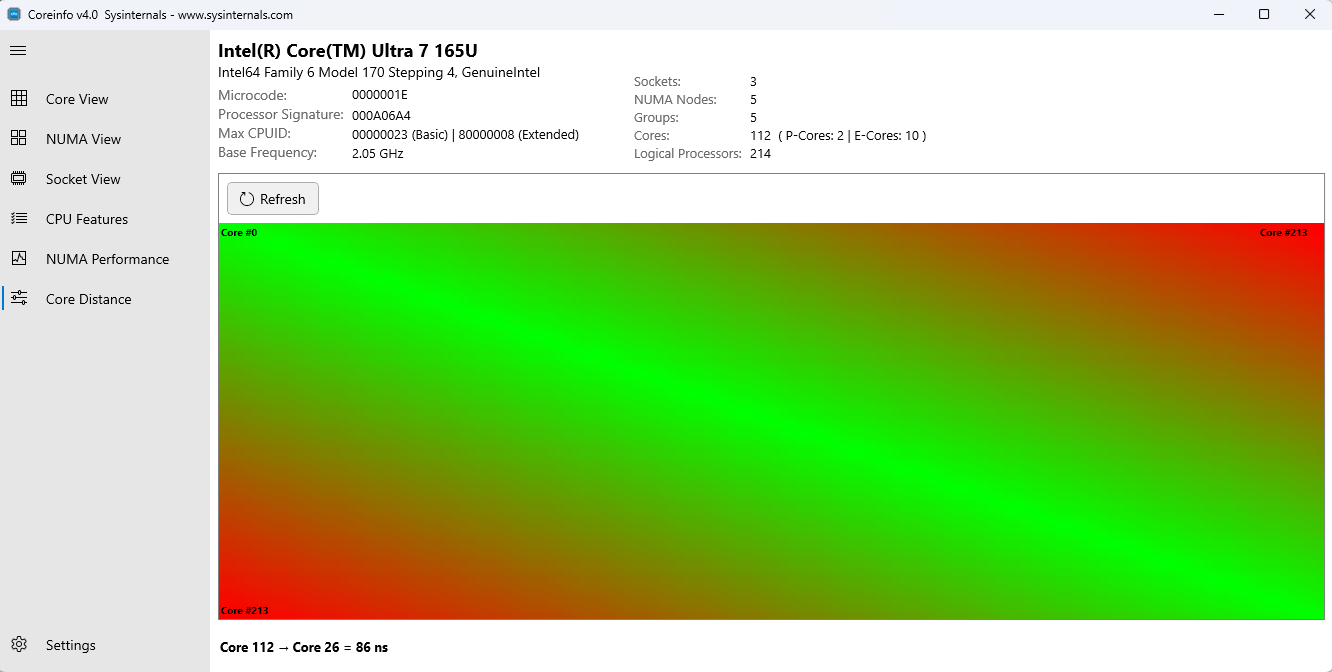

6. 核心距离视图

核心距离视图显示单个 CPU 核心之间的通信成本的详细热度图,提供有关核心到核心延迟和通信效率的见解。

功能:

-

Core-Level 热度地图:彩色编码矩阵,显示核心之间的相对距离

- 绿色/蓝色 = 低延迟(同一核心群集,共享缓存)

- 黄色/橙色 = 中等延迟(同一插槽,不同集群)

- 红色 = 高延迟(不同的套接字或 NUMA 节点)

- 交互式浏览:将鼠标悬停在网格画布上以查看详细的距离信息

- 精细分析:以最佳粒度显示核心到核心关系

- 动态刷新:使用“刷新”按钮动态获取更新的核心距离数据

显示的信息:

- NxN 矩阵,其中 N = 逻辑处理器数

- 从源核心(行)到目标核心的相对距离/延迟(列)

- 用于快速识别核心关系的颜色编码

- 详细信息窗格中的详细距离指标

核心距离热度地图,显示核心到核心通信成本

核心距离热度地图,显示核心到核心通信成本

了解距离图:

- 对角元素:始终为零(自身核心)

- 低距离(绿色):核心共享 L2 或 L3 缓存

- 中等距离(黄色):同一套接字上的核心,但在不同的缓存域

- 高距离(红色):位于不同套接字或 NUMA 节点上的核心

用例:

- 线程相关性优化

- 了解缓存一致性域

- 确定用于通信线程的最佳核心对

- 分析多线程应用程序性能

- 设计低延迟应用程序的 CPU 固定策略

交互式功能

核心选择和详细信息

在任意视图(核心视图、NUMA 视图或套接字视图)中单击一个核心会在底部的详细信息窗格中显示相关详细信息:

- 处理器信息:逻辑处理器编号、掩码和相关性

-

缓存层次结构:

- L1 数据缓存(大小、关联性、行大小)

- L1 指令缓存(大小、关联性、行大小)

- L2 缓存(大小、关联性、行大小)

- L3 缓存(大小、关联性、行大小)

- 拓扑信息:NUMA 节点、套接字和组分配

- 核心类型:P-Core、E-Core 或标准核心指定

搜索功能

CPU 功能视图包括一个搜索栏,可用于快速查找特定处理器功能:

- 单击搜索图标

- 键入功能名称或缩写

- 列表自动筛选以显示匹配功能

- 清除搜索以还原完整列表

缓存映射切换

在核心视图中,在两种可视化模式之间切换:

- 默认模式:按逻辑排列显示核心

- 缓存映射模式:重新组织核心以可视化缓存共享关系

视图之间的导航

- 使用左侧导航窗格在视图之间切换

- 查看特定 NUMA 节点或套接字时,再次单击同一视图将返回到整体视图

- 导航窗格中突出显示了当前视图

设置和自定义

通过导航菜单中的“设置”选项访问设置。

外观设置

主题选项:

- 浅色:针对明亮环境优化的浅色方案

- 深色:深色方案以减少眼睛紧张

- 系统默认值:自动匹配 Windows 主题首选项

保存到文件

导出核心拓扑数据:

- 使用 “保存到” 选项将核心拓扑数据转储到文件

- 输出格式与命令行工具输出相同

了解系统拓扑

核心类型(混合体系结构)

新式 CPU 可能具有具有不同核心类型的混合体系结构:

- P 核心(性能):针对单线程工作负载和要求苛刻的工作负荷优化的高性能核心

- E-Cores (效率):针对后台任务和多线程工作负荷优化的节能核心

Coreinfo UI 可清楚地识别和区分所有适用视图中的这些核心类型。

NUMA 体系结构

什么是 NUMA? 非统一内存访问(NUMA)是一种内存设计,其中每个处理器都有可快速访问的本地内存,以及需要处理器间通信的远程内存。

为什么它很重要:

- 本地内存访问明显快于远程访问

- 应用程序性能可能会受到 NUMA 布局的影响

- 了解 NUMA 拓扑对于高性能计算至关重要

使用 Coreinfo UI 进行 NUMA 优化:

- 使用 NUMA 视图 了解系统的 NUMA 拓扑

- 查看 NUMA 性能视图 以查看内存访问成本

- 根据 NUMA 节点分配优化线程/进程放置

- 使用 核心距离视图 了解 NUMA 节点内部和跨 NUMA 节点之间的核心到核心通信

缓存层次结构

缓存级别:

- L1 缓存:最小和最快,拆分为数据和指令缓存

- L2 缓存:较大的统一缓存,通常专用于每个核心

- L3 缓存:最大的统一缓存,通常在多个核心之间共享

使用缓存信息:

- 了解哪些核心共享缓存资源

- 优化缓存共享核心的数据本地性

- 在核心视图中使用缓存映射模式可视化缓存域

从命令行使用 Coreinfo

对于每个资源,它显示对应于指定资源的 OS 可见处理器的映射,其中“*”表示适用的处理器。 例如,在 4 核系统上,缓存输出中的一行包含核心 3 和 4 共享的映射。

用法:

coreinfo [-c][-f][-g][-l][-n][-s][-m][-v]

| 参数 | 说明 |

|---|---|

| -c | 有关核心的转储信息。 |

| -f | 转储核心功能信息。 |

| -g | 有关组的转储信息。 |

| -l | 有关缓存的转储信息。 |

| -n | 有关 NUMA 节点的转储信息。 |

| -s | 有关套接字的转储信息。 |

| -m | 转储 NUMA 访问成本。 |

| -v | 仅转储与虚拟化相关的功能,包括对二级地址转换的支持。 (需要 Intel 系统的管理权限)。 |

默认情况下,除-v之外,其他选项均处于选中状态。

Coreinfo 输出:

Coreinfo v4.0 - Dump information on system CPU and memory topology

Copyright © 2008-2025 Mark Russinovich

Sysinternals - www.sysinternals.com

Intel(R) Core(TM) Ultra 7 165U

Intel64 Family 6 Model 170 Stepping 4, GenuineIntel

Microcode signature: 0000001E

Processor signature: 000A06A4

Maximum implemented CPUID leaves: 00000023 (Basic), 80000008 (Extended).

Maximum implemented address width: 48 bits (virtual), 46 bits (physical).

HTT * Hyperthreading enabled

CET * Supports Control Flow Enforcement Technology

Kernel CET - Kernel-mode CET Enabled

User CET * User-mode CET Allowed

X64 * Supports 64-bit mode

SMX - Supports Intel trusted execution

SKINIT - Supports AMD SKINIT

SGX - Supports Intel SGX

NX * Supports no-execute page protection

SMEP * Supports Supervisor Mode Execution Prevention

SMAP * Supports Supervisor Mode Access Prevention

PAGE1GB * Supports 1 GB large pages

PAE * Supports > 32-bit physical addresses

PAT * Supports Page Attribute Table

PSE * Supports 4 MB pages

PSE36 * Supports > 32-bit address 4 MB pages

PGE * Supports global bit in page tables

SS * Supports bus snooping for cache operations

VME * Supports Virtual-8086 mode

RDWRFSGSBASE * Supports direct GS/FS base access

FPU * Implements i387 floating point instructions

MMX * Supports MMX instruction set

MMXEXT - Implements AMD MMX extensions

3DNOW - Supports 3DNow! instructions

3DNOWEXT - Supports 3DNow! extension instructions

SSE * Supports Streaming SIMD Extensions

SSE2 * Supports Streaming SIMD Extensions 2

SSE3 * Supports Streaming SIMD Extensions 3

SSSE3 * Supports Supplemental SIMD Extensions 3

SSE4a - Supports Streaming SIMDR Extensions 4a

SSE4.1 * Supports Streaming SIMD Extensions 4.1

SSE4.2 * Supports Streaming SIMD Extensions 4.2

AES * Supports AES extensions

AVX * Supports AVX instruction extensions

AVX2 * Supports AVX2 instruction extensions

AVX-512-F - Supports AVX-512 Foundation instructions

AVX-512-DQ - Supports AVX-512 double and quadword instructions

AVX-512-IFAMA - Supports AVX-512 integer Fused multiply-add instructions

AVX-512-PF - Supports AVX-512 prefetch instructions

AVX-512-ER - Supports AVX-512 exponential and reciprocal instructions

AVX-512-CD - Supports AVX-512 conflict detection instructions

AVX-512-BW - Supports AVX-512 byte and word instructions

AVX-512-VL - Supports AVX-512 vector length instructions

FMA * Supports FMA extensions using YMM state

MSR * Implements RDMSR/WRMSR instructions

MTRR * Supports Memory Type Range Registers

XSAVE * Supports XSAVE/XRSTOR instructions

OSXSAVE * Supports XSETBV/XGETBV instructions

RDRAND * Supports RDRAND instruction

RDSEED * Supports RDSEED instruction

CMOV * Supports CMOVcc instruction

CLFSH * Supports CLFLUSH instruction

CX8 * Supports compare and exchange 8-byte instructions

CX16 * Supports CMPXCHG16B instruction

BMI1 * Supports bit manipulation extensions 1

BMI2 * Supports bit manipulation extensions 2

ADX * Supports ADCX/ADOX instructions

DCA - Supports prefetch from memory-mapped device

F16C * Supports half-precision instruction

FXSR * Supports FXSAVE/FXSTOR instructions

FFXSR - Supports optimized FXSAVE/FSRSTOR instruction

MONITOR * Supports MONITOR and MWAIT instructions

MOVBE * Supports MOVBE instruction

ERMSB * Supports Enhanced REP MOVSB/STOSB

PCLMULDQ * Supports PCLMULDQ instruction

POPCNT * Supports POPCNT instruction

LZCNT * Supports LZCNT instruction

SEP * Supports fast system call instructions

LAHF-SAHF * Supports LAHF/SAHF instructions in 64-bit mode

HLE - Supports Hardware Lock Elision instructions

RTM - Supports Restricted Transactional Memory instructions

DE * Supports I/O breakpoints including CR4.DE

DTES64 - Can write history of 64-bit branch addresses

DS - Implements memory-resident debug buffer

DS-CPL - Supports Debug Store feature with CPL

PCID * Supports PCIDs and settable CR4.PCIDE

INVPCID * Supports INVPCID instruction

PDCM * Supports Performance Capabilities MSR

RDTSCP * Supports RDTSCP instruction

TSC * Supports RDTSC instruction

TSC-DEADLINE * Local APIC supports one-shot deadline timer

TSC-INVARIANT * TSC runs at constant rate

xTPR * Supports disabling task priority messages

EIST * Supports Enhanced Intel Speedstep

ACPI * Implements MSR for power management

TM * Implements thermal monitor circuitry

TM2 * Implements Thermal Monitor 2 control

APIC * Implements software-accessible local APIC

x2APIC * Supports x2APIC

CNXT-ID - L1 data cache mode adaptive or BIOS

MCE * Supports Machine Check, INT18 and CR4.MCE

MCA * Implements Machine Check Architecture

PBE * Supports use of FERR#/PBE# pin

PSN - Implements 96-bit processor serial number

HTT * Hyperthreading

PREFETCHW * PrefetchW instruction support

HYPERVISOR * Hypervisor is present

VMX - Supports Intel hardware-assisted virtualization

EPT - Supports Intel extended page tables (SLAT)

URG - Supports Intel unrestricted guest

Logical to Physical Processor Map:

**------------ Physical Processor 0 (Hyperthreaded)

--*----------- Physical Processor 1

---*---------- Physical Processor 2

----*--------- Physical Processor 3

-----*-------- Physical Processor 4

------*------- Physical Processor 5

-------*------ Physical Processor 6

--------*----- Physical Processor 7

---------*---- Physical Processor 8

----------**-- Physical Processor 9 (Hyperthreaded)

------------*- Physical Processor 10

-------------* Physical Processor 11

Logical Processor to Socket Map:

************** Socket 0

Logical Processor to NUMA Node Map:

************** NUMA Node 0

No NUMA nodes.

Logical Processor to Cache Map:

**------------ Data Cache 0, Level 1, 48 KB, Assoc 12, LineSize 64

**------------ Instruction Cache 0, Level 1, 64 KB, Assoc 16, LineSize 64

**------------ Unified Cache 0, Level 2, 2 MB, Assoc 16, LineSize 64

************-- Unified Cache 1, Level 3, 12 MB, Assoc 12, LineSize 64

--*----------- Data Cache 1, Level 1, 32 KB, Assoc 8, LineSize 64

--*----------- Instruction Cache 1, Level 1, 64 KB, Assoc 8, LineSize 64

--****-------- Unified Cache 2, Level 2, 2 MB, Assoc 16, LineSize 64

---*---------- Data Cache 2, Level 1, 32 KB, Assoc 8, LineSize 64

---*---------- Instruction Cache 2, Level 1, 64 KB, Assoc 8, LineSize 64

----*--------- Data Cache 3, Level 1, 32 KB, Assoc 8, LineSize 64

----*--------- Instruction Cache 3, Level 1, 64 KB, Assoc 8, LineSize 64

-----*-------- Data Cache 4, Level 1, 32 KB, Assoc 8, LineSize 64

-----*-------- Instruction Cache 4, Level 1, 64 KB, Assoc 8, LineSize 64

------*------- Data Cache 5, Level 1, 32 KB, Assoc 8, LineSize 64

------*------- Instruction Cache 5, Level 1, 64 KB, Assoc 8, LineSize 64

------****---- Unified Cache 3, Level 2, 2 MB, Assoc 16, LineSize 64

-------*------ Data Cache 6, Level 1, 32 KB, Assoc 8, LineSize 64

-------*------ Instruction Cache 6, Level 1, 64 KB, Assoc 8, LineSize 64

--------*----- Data Cache 7, Level 1, 32 KB, Assoc 8, LineSize 64

--------*----- Instruction Cache 7, Level 1, 64 KB, Assoc 8, LineSize 64

---------*---- Data Cache 8, Level 1, 32 KB, Assoc 8, LineSize 64

---------*---- Instruction Cache 8, Level 1, 64 KB, Assoc 8, LineSize 64

----------**-- Data Cache 9, Level 1, 48 KB, Assoc 12, LineSize 64

----------**-- Instruction Cache 9, Level 1, 64 KB, Assoc 16, LineSize 64

----------**-- Unified Cache 4, Level 2, 2 MB, Assoc 16, LineSize 64

------------*- Data Cache 10, Level 1, 32 KB, Assoc 8, LineSize 64

------------*- Instruction Cache 10, Level 1, 64 KB, Assoc 8, LineSize 64

------------** Unified Cache 5, Level 2, 2 MB, Assoc 16, LineSize 64

-------------* Data Cache 11, Level 1, 32 KB, Assoc 8, LineSize 64

-------------* Instruction Cache 11, Level 1, 64 KB, Assoc 8, LineSize 64

Logical Processor to Group Map:

************** Group 0

Sysinternals Live下载下载 Coreinfo(3 MB)立即运行。

Sysinternals Live下载下载 Coreinfo(3 MB)立即运行。

运行于:

- 客户端:Windows 11 及更高版本。

- 服务器:Windows Server 2016 及更高版本。