Catatan

Akses ke halaman ini memerlukan otorisasi. Anda dapat mencoba masuk atau mengubah direktori.

Akses ke halaman ini memerlukan otorisasi. Anda dapat mencoba mengubah direktori.

Oleh Mark Russinovich

Diterbitkan: 16 Desember 2025

Coreinfo(3 MB)

Coreinfo(3 MB)

Pendahuluan

Coreinfo adalah utilitas yang menunjukkan pemetaan antara prosesor logis dan prosesor fisik, simpul NUMA, dan soket tempat mereka berada, serta cache yang ditetapkan untuk setiap prosesor logis. Ini menggunakan API Windows tingkat rendah (mode pengguna dan mode kernel) untuk mengambil informasi topologi CPU terperinci langsung dari sistem operasi. Versi baris perintah menghasilkan representasi pemetaan ke prosesor logis dengan tanda bintang misalnya '*'. UI menyediakan beberapa tampilan khusus untuk mengeksplorasi berbagai aspek topologi CPU sistem Anda, termasuk inti logis dan fisik, node NUMA, soket, hierarki cache, dan metrik performa real time. Coreinfo berguna untuk mendapatkan wawasan tentang topologi prosesor dan cache sistem.

Penginstalan

Ekstrak arsip ke direktori lalu jalankan Coreinfo dengan mengetik dari direktori Coreinfo / Coreinfo64 tersebut atau Coreinfo64a, tergantung pada arsitekturnya. Luncurkan CoreInfoEx / CoreInfoEx64 / CoreInfoEx64a untuk versi UI.

Catatan: Beberapa fitur mungkin memerlukan hak administratif untuk pengambilan informasi lengkap.

Gambaran Umum Antarmuka Pengguna

Antarmuka pengguna Coreinfo terdiri dari beberapa komponen utama:

Tata Letak Jendela Utama

- Panel Atas: Menampilkan informasi sistem termasuk nama CPU, arsitektur, dan jumlah inti

- Panel Navigasi (Kiri): Menyediakan akses cepat ke tampilan yang berbeda

- Area Konten (Tengah): Menampilkan data dan visualisasi tampilan yang dipilih

- Panel Detail (Bawah): Menampilkan informasi terperinci saat inti atau sel dipilih

- Pengaturan: Opsi tampilan akses dan preferensi aplikasi

memperlihatkan tata letak UI lengkap, mode gelap

memperlihatkan tata letak UI lengkap, mode gelap

Tampilan Navigasi

Panel navigasi kiri menyediakan akses ke enam tampilan khusus:

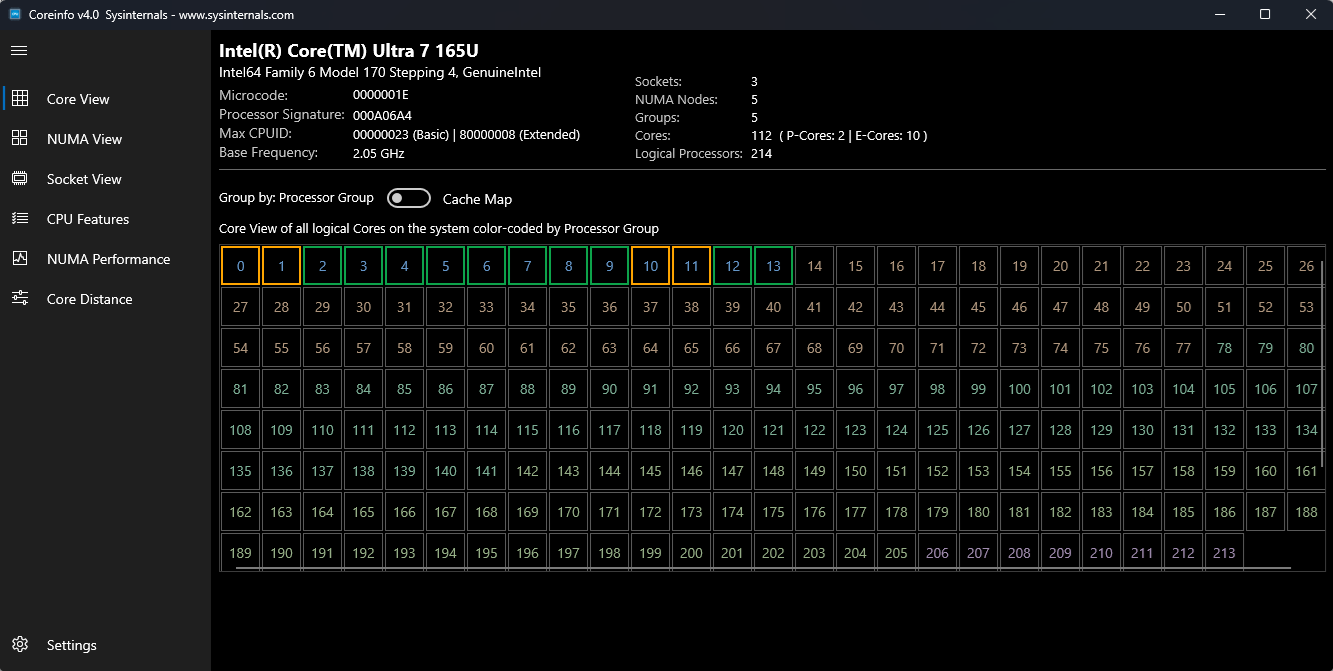

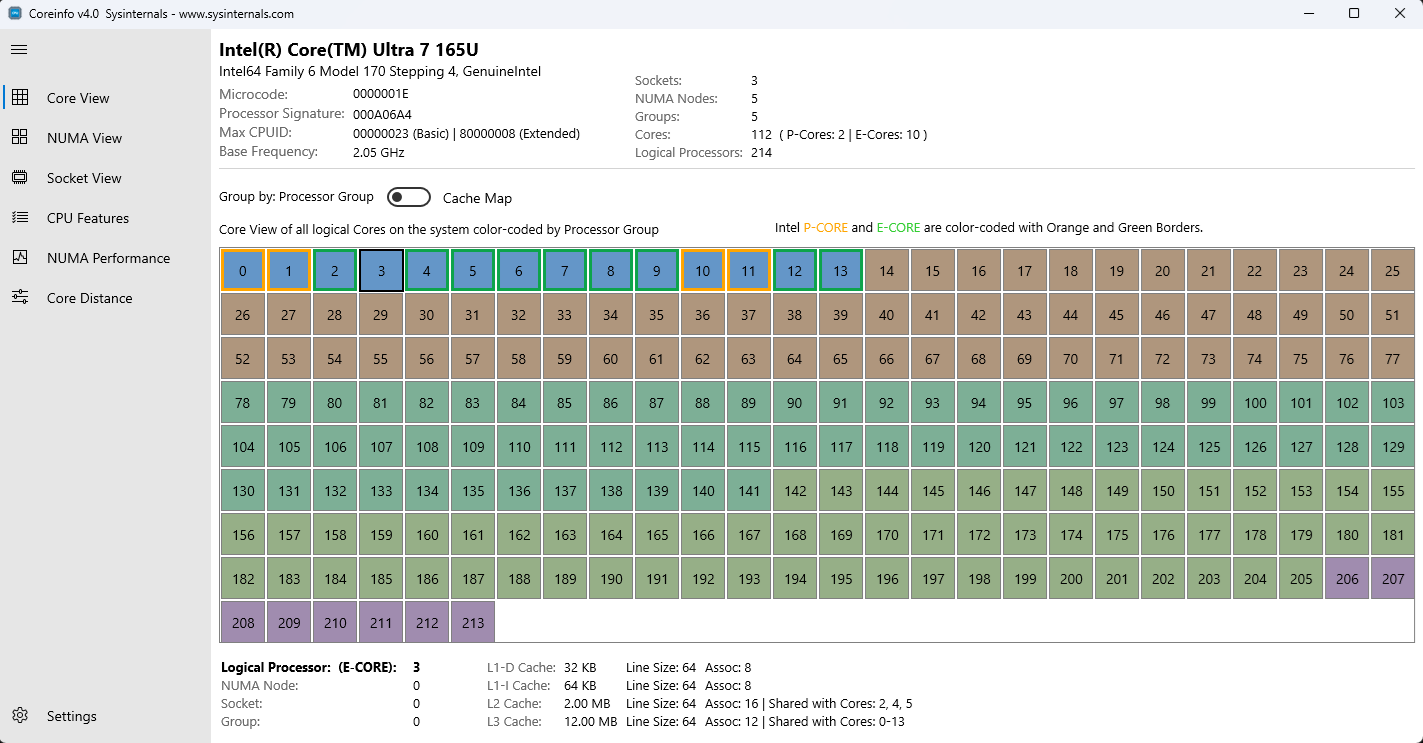

1. Tampilan Inti

Tampilan Inti menampilkan semua prosesor logis dalam sistem Anda dalam tata letak kisi, memperlihatkan hubungan antara inti logis dan sumber daya fisiknya.

Fitur:

- Tata Letak Kisi: Setiap sel mewakili prosesor logis

-

Indikator Tipe Inti:

- P-Cores (Inti performa) - berwarna berbeda

- E-Cores (Inti Efisiensi) - Berwarna berbeda

- Inti standar - pewarnaan default

- Bolak-balik Pemetaan Cache: Beralih antara tampilan default dan tampilan hierarki cache

- Pilihan Interaktif: Klik inti apa pun untuk melihat informasi terperinci di panel bawah

Informasi yang Ditampilkan:

- Nomor prosesor logis

- Jenis inti (P-Core/E-Core jika berlaku)

- Tingkat cache terkait (L1, L2, L3)

- Penetapan simpul NUMA

- Penetapan soket

- Tugas kelompok

Core View menampilkan proses-proses logis dalam tata letak grid

Core View menampilkan proses-proses logis dalam tata letak grid

Informasi Panel Detail (saat inti dipilih):

- Masker prosesor dan afinitas

- Hierarki cache (Cache Data, Cache Instruksi, Cache Terpadu)

- Ukuran cache dan asosiasi

- Ukuran garis cache

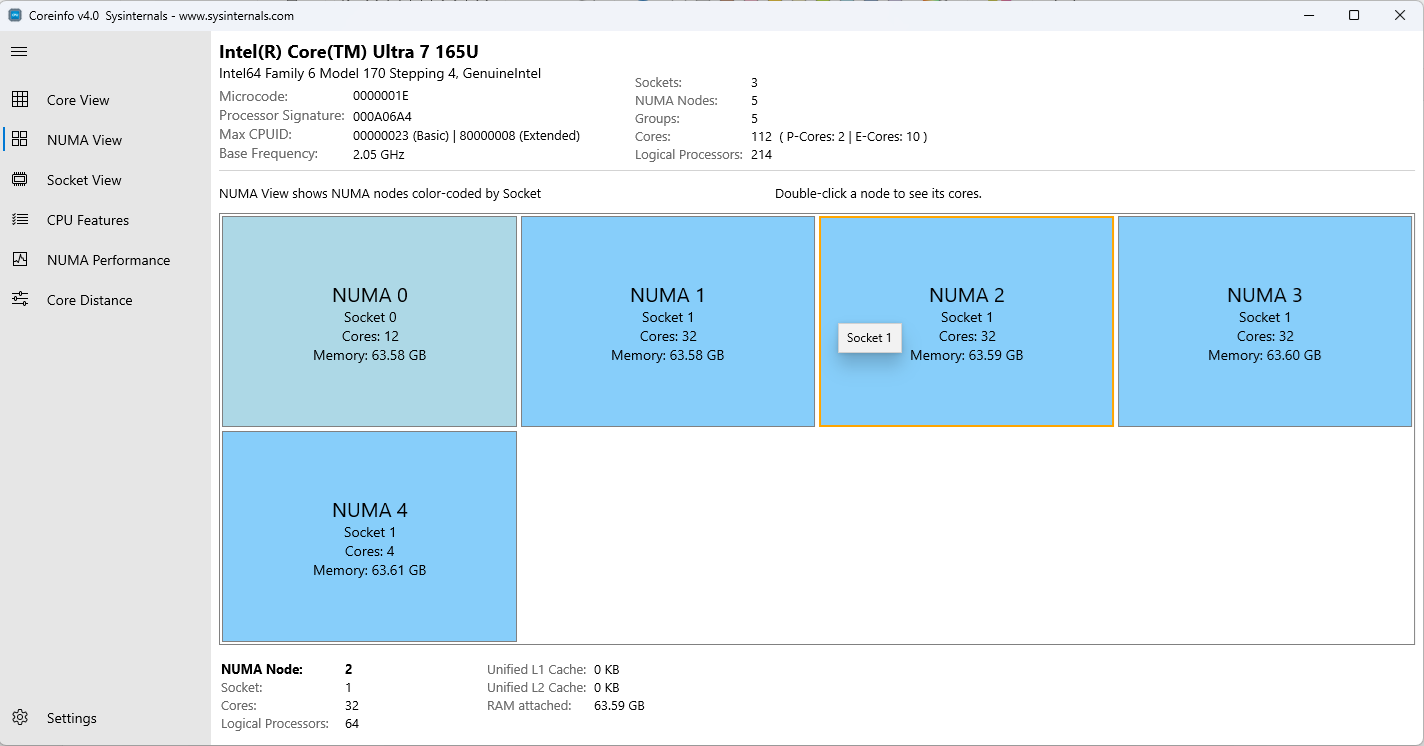

2. Tampilan NUMA

Tampilan NUMA (Akses Memori Non-Seragam) mengatur inti berdasarkan penetapan simpul NUMA mereka, sehingga mudah untuk memahami lokalitas memori dan pola akses.

Fitur:

- Organisasi Berbasis Node: Inti yang dikelompokkan berdasarkan node NUMA

- Core Fisik vs Logis: Menampilkan kedua hitungan untuk setiap simpul

- Informasi Memori: Menampilkan memori yang tersedia per simpul NUMA

-

Navigasi Interaktif:

- Klik tunggal pada simpul NUMA untuk menampilkan detailnya di panel detail bawah

- Klik dua kali pada simpul NUMA untuk menavigasi ke Tampilan Inti yang memperlihatkan semua inti dari simpul NUMA yang dipilih

- Tampilan Hierarkis: Menampilkan hubungan antara simpul NUMA dan inti

Informasi yang Ditampilkan:

- Jumlah simpul NUMA

- Inti per simpul NUMA (fisik dan logis)

- Kapasitas memori per simpul

- Distribusi inti di seluruh simpul

- Jumlah inti efisiensi (jika berlaku)

NUMA memperlihatkan inti yang diatur oleh simpul NUMA

NUMA memperlihatkan inti yang diatur oleh simpul NUMA

Kasus Penggunaan:

- Mengoptimalkan pola akses memori

- Memahami kinerja aplikasi yang mendukung NUMA

- Merencanakan penempatan utas/proses untuk performa optimal

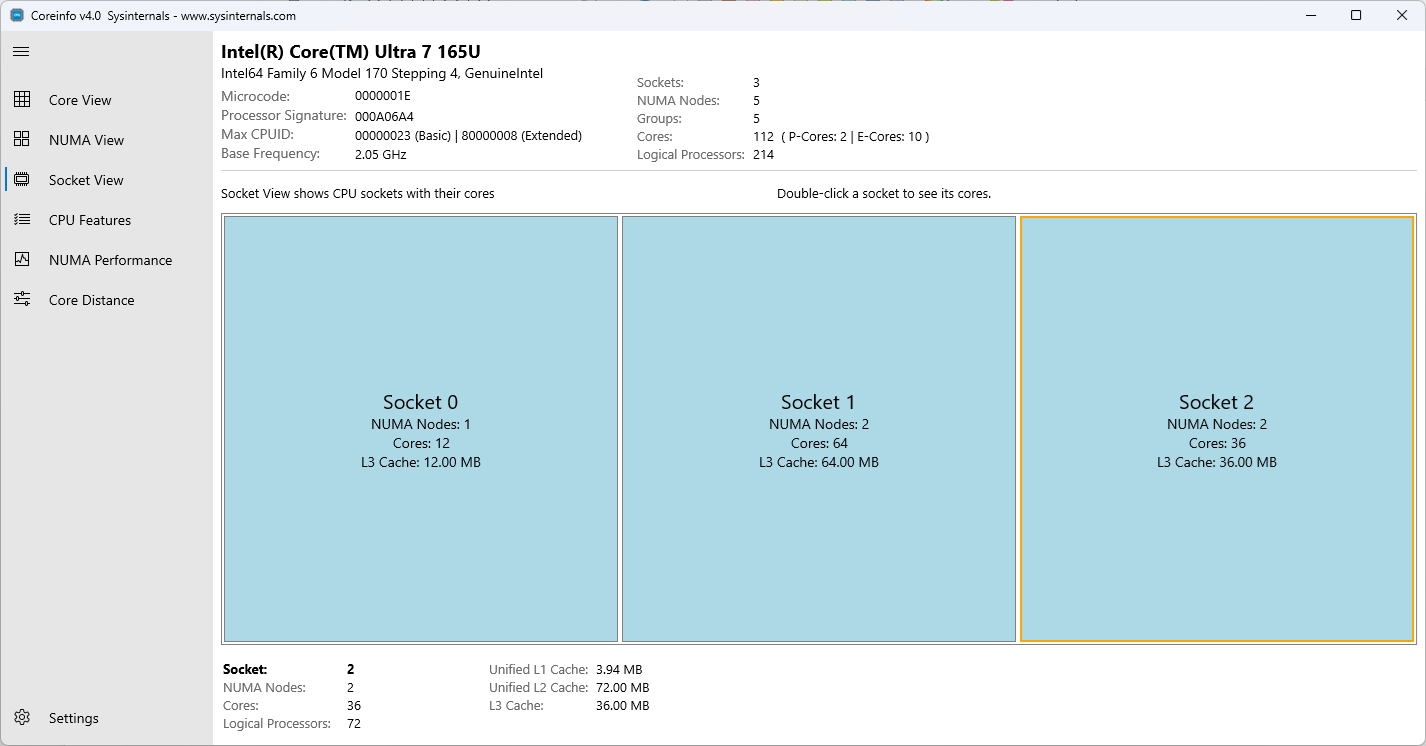

3. Tampilan Soket

Tampilan Soket menampilkan inti yang diatur oleh soket CPU fisiknya, berguna untuk memahami sistem multi-soket dan distribusi sumber daya tingkat soket.

Fitur:

- Pengelompokan Berbasis Soket: Core yang diatur oleh soket fisik

- Informasi Soket: Jumlah soket dan distribusi inti

-

Navigasi Interaktif:

- Klik tunggal pada soket untuk menampilkan detailnya di panel detail bawah

- Klik dua kali pada soket untuk menavigasi ke Tampilan Inti yang memperlihatkan semua inti dari soket yang dipilih

- Berbagi Cache: Memvisualisasikan inti mana yang berbagi cache tingkat soket

Informasi yang Ditampilkan:

- Jumlah soket fisik

- Core per soket (fisik dan logis)

- Informasi cache tingkat soket

- Simpul NUMA per soket

Tampilan Soket yang memperlihatkan inti yang diatur oleh soket CPU

Tampilan Soket yang memperlihatkan inti yang diatur oleh soket CPU

Kasus Penggunaan:

- Analisis sistem multi-soket

- Memahami biaya komunikasi lintas soket

- Merencanakan distribusi beban kerja di server multi-soket

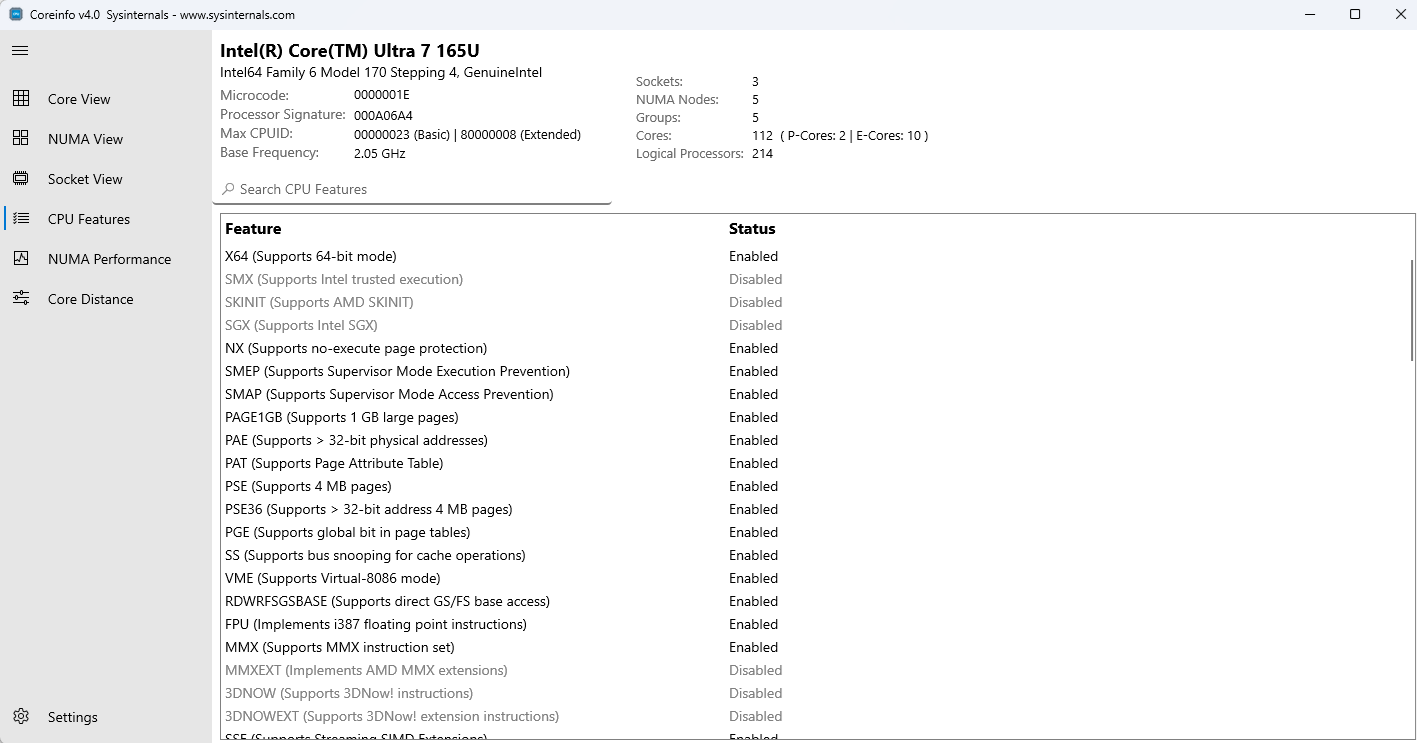

4. Tampilan Fitur CPU

Tampilan Fitur CPU menampilkan daftar kemampuan prosesor yang komprehensif, ekstensi set instruksi, dan fitur perangkat keras yang didukung oleh CPU Anda.

Fitur:

- Daftar yang Dapat Dicari: Menemukan fitur CPU tertentu dengan cepat menggunakan bilah pencarian

-

Indikator Status: Indikasi visual yang jelas untuk fitur yang didukung/tidak didukung menggunakan pengodean warna

- Fitur yang didukung ditampilkan dalam warna normal

- Fitur yang tidak didukung/dinonaktifkan berwarna abu-abu

-

Kategori Fitur:

- Virtualisasi (VMX, SVM, HYPERVISOR)

- Dukungan 64-bit (EM64T, NX)

- Set Instruksi (SSE, AVX, AES, dll.)

- Power Management (EIST, ACPI, Thermal)

- Fitur keamanan (SMX, SKINIT)

- Fitur memori (PAE, PAT, PSE)

- Fitur debug dan pemantauan

Informasi yang Ditampilkan:

- Singkatan fitur

- Status fitur (didukung/tidak didukung)

- Deskripsi fitur lengkap (di panel detail)

Tampilan  Fitur CPU memperlihatkan daftar kemampuan prosesor

Fitur CPU memperlihatkan daftar kemampuan prosesor

Catatan: Beberapa fitur virtualisasi (seperti VMX, SVM) dapat salah dilaporkan sebagai tidak tersedia saat berjalan dengan hypervisor aktif, atau saat berjalan dari dalam komputer virtual. Coreinfo harus dijalankan pada sistem tanpa hypervisor yang berjalan untuk hasil yang akurat.

Kasus Penggunaan:

- Memverifikasi ketersediaan set instruksi sebelum menyebarkan aplikasi

- Memeriksa dukungan virtualisasi

- Memahami pembuatan dan kemampuan prosesor

- Men-debug masalah performa yang terkait dengan fitur CPU yang hilang

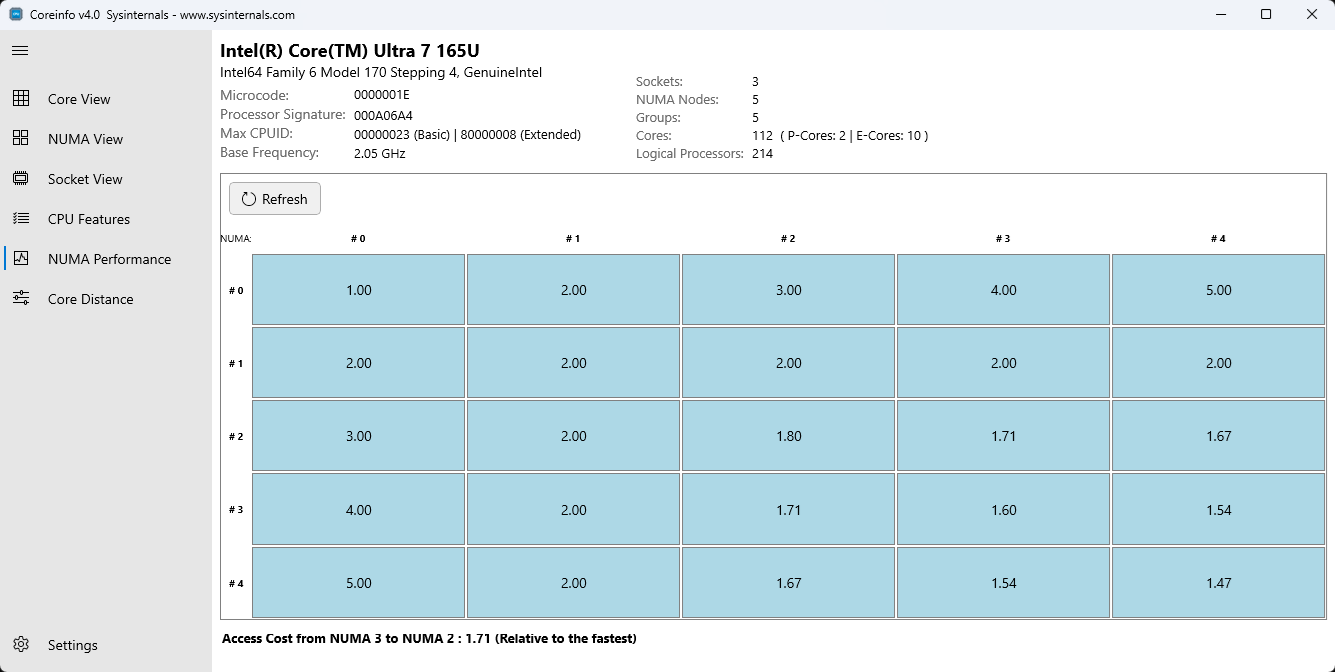

5. Tampilan Performa NUMA

Tampilan Performa NUMA menyediakan visualisasi kisi yang menunjukkan biaya akses memori antara simpul NUMA, membantu mengidentifikasi hambatan performa dalam sistem NUMA.

Fitur:

- Visualisasi Kisi: Matriks yang menampilkan biaya akses memori relatif antara simpul NUMA

- Matriks Interaktif: Arahkan kursor ke sel untuk melihat informasi performa terperinci

- Real-Time Pembaruan: Pembaruan data performa secara dinamis dengan memilih tombol Refresh

- Tampilan Biaya Relatif: Menunjukkan biaya relatif mengakses memori dari node NUMA yang berbeda

Informasi yang Ditampilkan:

- Matriks NxN di mana N = jumlah simpul NUMA

- Biaya akses memori dari simpul NUMA sumber (baris) ke simpul NUMA tujuan (kolom)

- Nilai numerik yang menunjukkan biaya performa relatif

- Sel diagonal memperlihatkan akses memori lokal (biasanya biaya terendah)

kisi kinerja NUMA yang memperlihatkan biaya akses memori

kisi kinerja NUMA yang memperlihatkan biaya akses memori

Memahami Jaringan:

- Elemen diagonal: Mewakili akses memori lokal (simpul yang mengakses memorinya sendiri) - biasanya nilai terendah

- Elemen off-diagonal: Mewakili akses memori jarak jauh dengan biaya relatif yang lebih tinggi

- Simetri: Matriks mungkin tidak simetris sempurna karena biaya akses dapat bervariasi menurut arah

Kasus Penggunaan:

- Mengidentifikasi hambatan performa terkait NUMA

- Mengoptimalkan strategi alokasi memori

- Merencanakan proses/penyematan utas untuk sistem NUMA

- Memahami penalti akses memori lintas simpul

6. Tampilan Jarak Inti

Tampilan Jarak Antara Inti menampilkan peta panas terperinci tentang biaya komunikasi antara inti CPU individual, memberikan wawasan tentang latensi antar inti dan efisiensi komunikasi.

Fitur:

-

Core-Level Peta Panas: Matriks berkode warna memperlihatkan jarak relatif antar inti

- Hijau/Biru = Latensi rendah (kluster inti yang sama, cache bersama)

- Kuning/Oranye = Latensi sedang (soket yang sama, kluster yang berbeda)

- Merah = Latensi tinggi (soket berbeda atau simpul NUMA)

- Eksplorasi Interaktif: Arahkan kursor ke kanvas kisi untuk melihat informasi jarak terperinci

- Analisis Terperinci: Menunjukkan hubungan inti-ke-inti pada granularitas terbaik

- Refresh Dinamis: Gunakan tombol Refresh untuk mendapatkan data jarak inti yang diperbarui secara dinamis

Informasi yang Ditampilkan:

- Matriks NxN di mana N = jumlah prosesor logis

- Jarak/latensi relatif dari inti sumber (baris) ke inti tujuan (kolom)

- Pengkodian warna untuk identifikasi visual cepat hubungan inti

- Metrik jarak terperinci di panel detail

Peta panas Tampilan Jarak Inti menampilkan biaya komunikasi antar inti

Memahami Peta Jarak:

- Elemen diagonal: Selalu nol (inti ke dirinya sendiri)

- Jarak rendah (hijau): Core berbagi cache L2 atau L3

- Jarak sedang (kuning): Core pada soket yang sama tetapi domain cache yang berbeda

- Jarak tinggi (merah): Core pada soket atau node NUMA yang berbeda

Kasus Penggunaan:

- Pengoptimalan afinitas utas

- Memahami domain koherensi cache

- Mengidentifikasi pasangan inti yang optimal untuk mengomunikasikan utas

- Menganalisis kinerja aplikasi multi-utas

- Merencanakan strategi pengikatan CPU untuk aplikasi latensi rendah

Fitur Interaktif

Pilihan dan Detail Inti

Mengklik inti dalam tampilan apa pun (Core, NUMA, atau Socket) menampilkan informasi terperinci di panel detail bawah:

- Informasi Prosesor: Nomor prosesor logis, masker, dan afinitas

-

Hierarki Cache:

- L1 Data Cache (ukuran, asosiasi, ukuran garis)

- Cache Instruksi L1 (ukuran, associativity, ukuran baris)

- L2 Cache (ukuran, asosiasi, ukuran baris)

- Cache L3 (ukuran, ketertautan, ukuran garis)

- Informasi Topologi: Penugasan simpul, soket, dan grup NUMA

- Jenis Inti: P-Core, E-Core, atau sebutan inti standar

Fungsionalitas Pencarian

Tampilan Fitur CPU menyertakan bilah pencarian yang memungkinkan Anda menemukan fitur prosesor tertentu dengan cepat:

- Klik ikon pencarian

- Ketik nama fitur atau singkatan

- Daftar secara otomatis memfilter untuk menampilkan fitur yang cocok

- Hapus pencarian untuk memulihkan daftar lengkap

Bolak-belakang Peta Cache

Di Tampilan Inti, alihkan di antara dua mode visualisasi:

- Mode Default: Menampilkan inti dalam susunan logisnya

- Mode Peta Cache: Mengatur ulang inti untuk memvisualisasikan hubungan berbagi cache

Navigasi Antar Tampilan

- Menggunakan panel navigasi kiri untuk beralih antar tampilan

- Saat melihat simpul atau soket NUMA tertentu, mengklik tampilan yang sama mengembalikan ke tampilan keseluruhan

- Tampilan saat ini disorot di panel navigasi

Pengaturan dan Kustomisasi

Akses pengaturan melalui menu Pengaturan di navigasi.

Pengaturan Tampilan

Opsi Tema:

- Cahaya: Skema warna terang dioptimalkan untuk lingkungan cerah

- Gelap: Skema warna gelap untuk mengurangi ketegangan mata

- Sistem Bawaan: Secara otomatis menyesuaikan dengan preferensi tema Windows Anda

Simpan ke File

Ekspor Data Topologi Inti:

- Gunakan opsi Simpan Ke untuk mencadangkan data topologi inti ke file

- Format output identik dengan output alat baris perintah

Memahami Topologi Sistem Anda

Jenis Inti (Arsitektur Hibrid)

CPU modern dapat menampilkan arsitektur hibrid dengan jenis inti yang berbeda:

- P-Cores (Performa): Inti berkinerja tinggi yang dioptimalkan untuk beban kerja berulir tunggal dan menuntut

- E-Cores (Efisiensi): Inti hemat energi yang dioptimalkan untuk tugas latar belakang dan beban kerja multi-utas

Antarmuka pengguna Coreinfo dengan jelas mengidentifikasi dan membedakan jenis inti ini dalam semua tampilan yang berlaku.

Arsitektur NUMA

Apa itu NUMA? Akses Memori Non-Seragam (NUMA) adalah desain memori di mana setiap prosesor memiliki memori lokal yang dapat diakses dengan cepat, dan memori jarak jauh yang memerlukan komunikasi antarprosesor.

Mengapa penting:

- Akses memori lokal secara signifikan lebih cepat daripada akses jarak jauh

- Performa aplikasi dapat dipengaruhi secara dramatis oleh penempatan NUMA

- Memahami topologi NUMA sangat penting untuk komputasi berkinerja tinggi

Menggunakan Coreinfo UI untuk Pengoptimalan NUMA:

- Gunakan Tampilan NUMA untuk memahami topologi NUMA sistem Anda

- Periksa Tampilan Performa NUMA untuk melihat biaya akses memori

- Mengoptimalkan penempatan utas/proses berdasarkan penetapan simpul NUMA

- Gunakan Visibilitas Jarak Inti untuk memahami komunikasi antar inti di dalam dan antar simpul NUMA

Hierarki Cache

Tingkat Cache:

- L1 Cache: Terkecil dan tercepat, dibagi menjadi data dan cache instruksi

- Cache L2: Cache terpadu yang lebih besar, biasanya privat ke setiap inti

- Cache L3: Cache terpadu terbesar, sering dibagikan di antara beberapa inti

Menggunakan Informasi Cache:

- Memahami inti mana yang berbagi sumber daya cache

- Mengoptimalkan lokalitas data untuk inti yang berbagi cache

- Menggunakan mode Peta Cache di Tampilan Inti untuk memvisualisasikan domain cache

Menggunakan Coreinfo dari baris perintah

Untuk setiap sumber daya, ini menunjukkan peta prosesor yang terlihat OS yang sesuai dengan sumber daya yang ditentukan, dengan '*' mewakili prosesor yang berlaku. Misalnya, pada sistem 4-core, garis dalam output cache dengan peta dibagikan oleh inti 3 dan 4.

Penggunaan:

coreinfo [-c][-f][-g][-l][-n][-s][-m][-v]

| Parameter | Deskripsi |

|---|---|

| -c | Buang informasi pada inti. |

| -f | Mencadangkan informasi fitur inti. |

| -g | Buang informasi pada grup. |

| -L | Buang informasi pada cache. |

| -n | Buang informasi pada simpul NUMA. |

| -s | Buang informasi pada soket. |

| -m | Mencadangkan biaya akses NUMA. |

| -v | Buang hanya fitur terkait virtualisasi termasuk dukungan untuk terjemahan alamat tingkat kedua. (memerlukan hak administratif pada sistem Intel). |

Semua opsi kecuali -v dipilih secara default.

Output Coreinfo:

Coreinfo v4.0 - Dump information on system CPU and memory topology

Copyright © 2008-2025 Mark Russinovich

Sysinternals - www.sysinternals.com

Intel(R) Core(TM) Ultra 7 165U

Intel64 Family 6 Model 170 Stepping 4, GenuineIntel

Microcode signature: 0000001E

Processor signature: 000A06A4

Maximum implemented CPUID leaves: 00000023 (Basic), 80000008 (Extended).

Maximum implemented address width: 48 bits (virtual), 46 bits (physical).

HTT * Hyperthreading enabled

CET * Supports Control Flow Enforcement Technology

Kernel CET - Kernel-mode CET Enabled

User CET * User-mode CET Allowed

X64 * Supports 64-bit mode

SMX - Supports Intel trusted execution

SKINIT - Supports AMD SKINIT

SGX - Supports Intel SGX

NX * Supports no-execute page protection

SMEP * Supports Supervisor Mode Execution Prevention

SMAP * Supports Supervisor Mode Access Prevention

PAGE1GB * Supports 1 GB large pages

PAE * Supports > 32-bit physical addresses

PAT * Supports Page Attribute Table

PSE * Supports 4 MB pages

PSE36 * Supports > 32-bit address 4 MB pages

PGE * Supports global bit in page tables

SS * Supports bus snooping for cache operations

VME * Supports Virtual-8086 mode

RDWRFSGSBASE * Supports direct GS/FS base access

FPU * Implements i387 floating point instructions

MMX * Supports MMX instruction set

MMXEXT - Implements AMD MMX extensions

3DNOW - Supports 3DNow! instructions

3DNOWEXT - Supports 3DNow! extension instructions

SSE * Supports Streaming SIMD Extensions

SSE2 * Supports Streaming SIMD Extensions 2

SSE3 * Supports Streaming SIMD Extensions 3

SSSE3 * Supports Supplemental SIMD Extensions 3

SSE4a - Supports Streaming SIMDR Extensions 4a

SSE4.1 * Supports Streaming SIMD Extensions 4.1

SSE4.2 * Supports Streaming SIMD Extensions 4.2

AES * Supports AES extensions

AVX * Supports AVX instruction extensions

AVX2 * Supports AVX2 instruction extensions

AVX-512-F - Supports AVX-512 Foundation instructions

AVX-512-DQ - Supports AVX-512 double and quadword instructions

AVX-512-IFAMA - Supports AVX-512 integer Fused multiply-add instructions

AVX-512-PF - Supports AVX-512 prefetch instructions

AVX-512-ER - Supports AVX-512 exponential and reciprocal instructions

AVX-512-CD - Supports AVX-512 conflict detection instructions

AVX-512-BW - Supports AVX-512 byte and word instructions

AVX-512-VL - Supports AVX-512 vector length instructions

FMA * Supports FMA extensions using YMM state

MSR * Implements RDMSR/WRMSR instructions

MTRR * Supports Memory Type Range Registers

XSAVE * Supports XSAVE/XRSTOR instructions

OSXSAVE * Supports XSETBV/XGETBV instructions

RDRAND * Supports RDRAND instruction

RDSEED * Supports RDSEED instruction

CMOV * Supports CMOVcc instruction

CLFSH * Supports CLFLUSH instruction

CX8 * Supports compare and exchange 8-byte instructions

CX16 * Supports CMPXCHG16B instruction

BMI1 * Supports bit manipulation extensions 1

BMI2 * Supports bit manipulation extensions 2

ADX * Supports ADCX/ADOX instructions

DCA - Supports prefetch from memory-mapped device

F16C * Supports half-precision instruction

FXSR * Supports FXSAVE/FXSTOR instructions

FFXSR - Supports optimized FXSAVE/FSRSTOR instruction

MONITOR * Supports MONITOR and MWAIT instructions

MOVBE * Supports MOVBE instruction

ERMSB * Supports Enhanced REP MOVSB/STOSB

PCLMULDQ * Supports PCLMULDQ instruction

POPCNT * Supports POPCNT instruction

LZCNT * Supports LZCNT instruction

SEP * Supports fast system call instructions

LAHF-SAHF * Supports LAHF/SAHF instructions in 64-bit mode

HLE - Supports Hardware Lock Elision instructions

RTM - Supports Restricted Transactional Memory instructions

DE * Supports I/O breakpoints including CR4.DE

DTES64 - Can write history of 64-bit branch addresses

DS - Implements memory-resident debug buffer

DS-CPL - Supports Debug Store feature with CPL

PCID * Supports PCIDs and settable CR4.PCIDE

INVPCID * Supports INVPCID instruction

PDCM * Supports Performance Capabilities MSR

RDTSCP * Supports RDTSCP instruction

TSC * Supports RDTSC instruction

TSC-DEADLINE * Local APIC supports one-shot deadline timer

TSC-INVARIANT * TSC runs at constant rate

xTPR * Supports disabling task priority messages

EIST * Supports Enhanced Intel Speedstep

ACPI * Implements MSR for power management

TM * Implements thermal monitor circuitry

TM2 * Implements Thermal Monitor 2 control

APIC * Implements software-accessible local APIC

x2APIC * Supports x2APIC

CNXT-ID - L1 data cache mode adaptive or BIOS

MCE * Supports Machine Check, INT18 and CR4.MCE

MCA * Implements Machine Check Architecture

PBE * Supports use of FERR#/PBE# pin

PSN - Implements 96-bit processor serial number

HTT * Hyperthreading

PREFETCHW * PrefetchW instruction support

HYPERVISOR * Hypervisor is present

VMX - Supports Intel hardware-assisted virtualization

EPT - Supports Intel extended page tables (SLAT)

URG - Supports Intel unrestricted guest

Logical to Physical Processor Map:

**------------ Physical Processor 0 (Hyperthreaded)

--*----------- Physical Processor 1

---*---------- Physical Processor 2

----*--------- Physical Processor 3

-----*-------- Physical Processor 4

------*------- Physical Processor 5

-------*------ Physical Processor 6

--------*----- Physical Processor 7

---------*---- Physical Processor 8

----------**-- Physical Processor 9 (Hyperthreaded)

------------*- Physical Processor 10

-------------* Physical Processor 11

Logical Processor to Socket Map:

************** Socket 0

Logical Processor to NUMA Node Map:

************** NUMA Node 0

No NUMA nodes.

Logical Processor to Cache Map:

**------------ Data Cache 0, Level 1, 48 KB, Assoc 12, LineSize 64

**------------ Instruction Cache 0, Level 1, 64 KB, Assoc 16, LineSize 64

**------------ Unified Cache 0, Level 2, 2 MB, Assoc 16, LineSize 64

************-- Unified Cache 1, Level 3, 12 MB, Assoc 12, LineSize 64

--*----------- Data Cache 1, Level 1, 32 KB, Assoc 8, LineSize 64

--*----------- Instruction Cache 1, Level 1, 64 KB, Assoc 8, LineSize 64

--****-------- Unified Cache 2, Level 2, 2 MB, Assoc 16, LineSize 64

---*---------- Data Cache 2, Level 1, 32 KB, Assoc 8, LineSize 64

---*---------- Instruction Cache 2, Level 1, 64 KB, Assoc 8, LineSize 64

----*--------- Data Cache 3, Level 1, 32 KB, Assoc 8, LineSize 64

----*--------- Instruction Cache 3, Level 1, 64 KB, Assoc 8, LineSize 64

-----*-------- Data Cache 4, Level 1, 32 KB, Assoc 8, LineSize 64

-----*-------- Instruction Cache 4, Level 1, 64 KB, Assoc 8, LineSize 64

------*------- Data Cache 5, Level 1, 32 KB, Assoc 8, LineSize 64

------*------- Instruction Cache 5, Level 1, 64 KB, Assoc 8, LineSize 64

------****---- Unified Cache 3, Level 2, 2 MB, Assoc 16, LineSize 64

-------*------ Data Cache 6, Level 1, 32 KB, Assoc 8, LineSize 64

-------*------ Instruction Cache 6, Level 1, 64 KB, Assoc 8, LineSize 64

--------*----- Data Cache 7, Level 1, 32 KB, Assoc 8, LineSize 64

--------*----- Instruction Cache 7, Level 1, 64 KB, Assoc 8, LineSize 64

---------*---- Data Cache 8, Level 1, 32 KB, Assoc 8, LineSize 64

---------*---- Instruction Cache 8, Level 1, 64 KB, Assoc 8, LineSize 64

----------**-- Data Cache 9, Level 1, 48 KB, Assoc 12, LineSize 64

----------**-- Instruction Cache 9, Level 1, 64 KB, Assoc 16, LineSize 64

----------**-- Unified Cache 4, Level 2, 2 MB, Assoc 16, LineSize 64

------------*- Data Cache 10, Level 1, 32 KB, Assoc 8, LineSize 64

------------*- Instruction Cache 10, Level 1, 64 KB, Assoc 8, LineSize 64

------------** Unified Cache 5, Level 2, 2 MB, Assoc 16, LineSize 64

-------------* Data Cache 11, Level 1, 32 KB, Assoc 8, LineSize 64

-------------* Instruction Cache 11, Level 1, 64 KB, Assoc 8, LineSize 64

Logical Processor to Group Map:

************** Group 0

Unduh Coreinfo(3 MB)Jalankan sekarang dari Sysinternals Live.

Unduh Coreinfo(3 MB)Jalankan sekarang dari Sysinternals Live.

Berjalan pada:

- Klien: Windows 11 dan yang lebih tinggi.

- Server: Windows Server 2016 dan yang lebih tinggi.