Nota

O acesso a esta página requer autorização. Pode tentar iniciar sessão ou alterar os diretórios.

O acesso a esta página requer autorização. Pode tentar alterar os diretórios.

Por Mark Russinovich

Publicado: 16 de dezembro de 2025

Descarregar Coreinfo(3 MB)

Descarregar Coreinfo(3 MB)

Introdução

O Coreinfo é uma ferramenta que mostra o mapeamento entre os processadores lógicos e o processador físico, o nó NUMA e o socket onde residem, bem como o cache atribuído a cada processador lógico. Utiliza APIs Windows de baixo nível (modo utilizador e modo kernel) para obter informações detalhadas sobre a topologia da CPU diretamente do sistema operativo. A versão de linha de comandos fornece a representação do mapeamento para um processador lógico com um asterisco, por exemplo '*'. A interface oferece múltiplas vistas especializadas para explorar diferentes aspetos da topologia da CPU do seu sistema, incluindo núcleos lógicos e físicos, nós NUMA, sockets, hierarquias de cache e métricas de desempenho em tempo real. O Coreinfo é útil para obter informações sobre a topologia do processador e cache do sistema.

Instalação

Extrai o arquivo para um diretório e depois executa o Coreinfo escrevendo a partir desse diretório Coreinfo / Coreinfo64 ou Coreinfo64a, dependendo da arquitetura. Lança CoreInfoEx / CoreInfoEx64 / CoreInfoEx64a para a versão da interface.

Nota: Algumas funcionalidades podem exigir privilégios administrativos para uma recuperação completa de informação.

Visão Geral da Interface de Utilizador

A interface Coreinfo consiste em vários componentes chave:

Disposição das Janelas Principais

- Painel superior: Apresenta informações do sistema, incluindo nome da CPU, arquitetura e contagem de núcleos

- Painel de Navegação (Esquerda): Permite acesso rápido a diferentes vistas

- Área de Conteúdo (Centro): Mostra os dados e visualizações da vista selecionada

- Painel de Detalhes (Inferior): Apresenta informação detalhada quando núcleos ou células são selecionados

- Definições: Aceder a opções de aparência e preferências de aplicação

Janela principal a mostrar o layout completo da interface, modo escuro

Janela principal a mostrar o layout completo da interface, modo escuro

Vistas de Navegação

O painel de navegação esquerdo dá acesso a seis vistas especializadas:

1. Visão Principal

A Vista de Núcleo apresenta todos os processadores lógicos do seu sistema numa disposição em grelha, mostrando a relação entre os núcleos lógicos e os seus recursos físicos.

Caraterísticas:

- Disposição da grelha: Cada célula representa um processador lógico

-

Indicadores de Tipo Central:

- P-Cores (núcleos de performance) - coloridos distintamente

- E-Cores (núcleos de eficiência) - coloridos de forma diferente

- Cores padrão - colorização padrão

- Alternância de Mapeamento da Cache: Alternar entre a vista padrão e a hierarquia da cache

- Seleção Interativa: Clique em qualquer núcleo para ver informações detalhadas no painel inferior

Informação Exibida:

- Número lógico do processador

- Tipo de núcleo (P-Core/E-Core, se aplicável)

- Níveis de cache associados (L1, L2, L3)

- Atribuição dos nós NUMA

- Atribuição de soquetes

- Atribuição de grupo

Vista Principal mostrando processadores lógicos em layout de grelha

Vista Principal mostrando processadores lógicos em layout de grelha

Informação do Painel de Detalhes (quando um núcleo é selecionado):

- Máscara de processador e afinidade

- Hierarquia de cache (Data Cache, Instruction Cache, Unified Cache)

- Tamanhos do cache e associatividade

- Tamanhos das linhas de cache

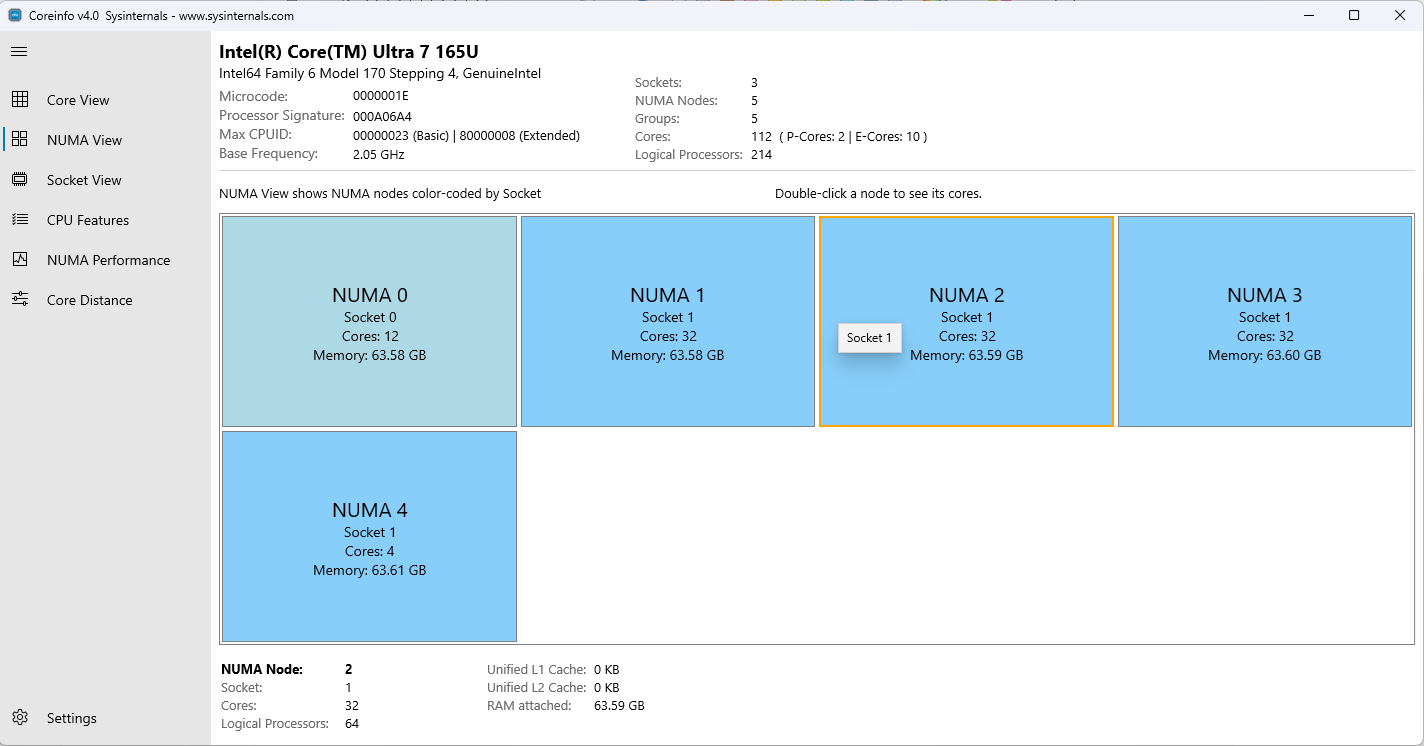

2. Vista NUMA

A Vista NUMA (Acesso à Memória Não Uniforme) organiza os núcleos pelas atribuições de nós NUMA, facilitando a compreensão da localidade e dos padrões de acesso à memória.

Caraterísticas:

- Organização Baseada em Nós: Núcleos agrupados por nós NUMA

- Núcleos Físicos vs Lógicos: Mostra ambas as contagens para cada nó

- Informação de Memória: Mostra memória disponível por nó NUMA

-

Navegação Interativa:

- Clique único num nó NUMA para mostrar os seus detalhes no painel de detalhes na parte inferior.

- Clique duas vezes num nó NUMA para navegar até à Core View, mostrando todos os núcleos desse nó NUMA selecionado

- Ecrã Hierárquica: Mostra a relação entre nós NUMA e núcleos

Informação Exibida:

- Número de nós NUMA

- Núcleos por nó NUMA (físico e lógico)

- Capacidade de memória por nó

- Distribuição dos núcleos entre nós

- Contagem de núcleos de eficiência (se aplicável)

Visualização NUMA mostrando núcleos organizados por nós NUMA

Visualização NUMA mostrando núcleos organizados por nós NUMA

Casos de Uso:

- Otimização dos padrões de acesso à memória

- Compreender o desempenho de aplicações otimizadas para NUMA

- Planeamento da colocação de fios/processos para um desempenho ótimo

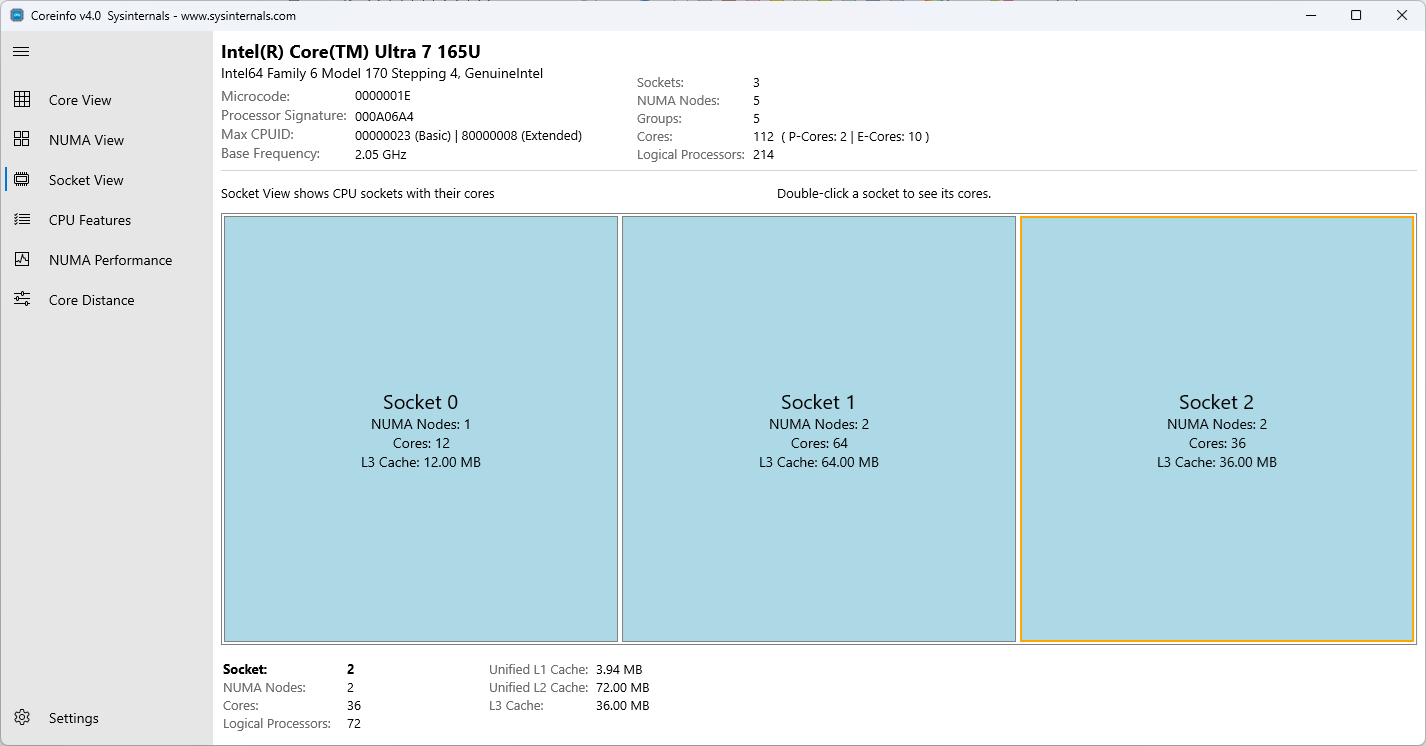

3. Vista do Soquete

A Vista de Soquetes apresenta núcleos organizados pelo seu soquete físico de CPU, útil para compreender sistemas multi-soquete e distribuição de recursos ao nível dos soquetes.

Caraterísticas:

- Agrupamento Baseado em Socket: Núcleos organizados por socket físico

- Informação sobre Soquetes: Contagem de soquetes e distribuição dos núcleos

-

Navegação Interativa:

- Clique com um único clique num soquete para mostrar os seus detalhes no painel inferior

- Clique duas vezes num socket para navegar até à Core View que mostra todos os núcleos desse socket selecionado

- Partilha de Cache: Visualize quais os núcleos que partilham caches ao nível dos sockets

Informação Exibida:

- Número de soquetes físicos

- Núcleos por soquete (físicos e lógicos)

- Informação de cache ao nível do socket

- Nós NUMA por socket

Vista de Soquete mostrando núcleos organizados por soquetes CPU

Vista de Soquete mostrando núcleos organizados por soquetes CPU

Casos de Uso:

- Análise de sistemas multi-soquete

- Compreender os custos de comunicação entre soquetes

- Planeamento da distribuição de cargas de trabalho em servidores multi-socket

4. Vista de Funcionalidades do CPU

A Visualização de Funcionalidades da CPU apresenta uma lista abrangente de capacidades do processador, extensões de conjunto de instruções e funcionalidades de hardware suportadas pelo seu CPU.

Caraterísticas:

- Lista pesquisável: Encontre rapidamente funcionalidades específicas do CPU usando a barra de pesquisa

-

Indicadores de Estado: Indicação visual clara de funcionalidades suportadas/não suportadas usando codificação por cores

- As funcionalidades suportadas são exibidas a cores normais

- Funcionalidades não suportadas/desativadas estão acinzentadas

-

Categorias de Funcionalidades:

- Virtualização (VMX, SVM, HYPERVISOR)

- Suporte a 64 bits (EM64T, NX)

- Conjuntos de Instruções (SSE, AVX, AES, etc.)

- Gestão de Energia (EIST, ACPI, Térmica)

- Funcionalidades de segurança (SMX, SKINIT)

- Funcionalidades de memória (PAE, PAT, PSE)

- Funcionalidades de depuração e monitorização

Informação Exibida:

- Abreviatura de funcionalidades

- Estado da funcionalidade (suportado/não suportado)

- Descrição completa da funcionalidade (painel de detalhes)

Visualização de Funcionalidades do CPU que mostra a lista de capacidades do processador

Visualização de Funcionalidades do CPU que mostra a lista de capacidades do processador

Nota: Algumas funcionalidades de virtualização (como VMX, SVM) podem ser incorretamente reportadas como não disponíveis ao ser executado com um hipervisor ativo, ou ao ser executado dentro de uma máquina virtual. O Coreinfo deve ser executado num sistema sem hipervisor a correr para obter resultados precisos.

Casos de Uso:

- Verificação da disponibilidade do conjunto de instruções antes de implementar aplicações

- Verificação de suporte à virtualização

- Compreender a geração e capacidades de processadores

- Depuração de problemas de desempenho relacionados com a ausência de características da unidade central de processamento (CPU)

5. Vista de Desempenho NUMA

A Vista de Performance NUMA fornece uma visualização em grelha que mostra os custos de acesso à memória entre nós NUMA, ajudando a identificar gargalos de desempenho nos sistemas NUMA.

Caraterísticas:

- Visualização de Grelha: Matriz que mostra os custos relativos de acesso à memória entre nós NUMA

- Matriz Interativa: Passe o rato sobre as células para ver informações detalhadas de desempenho

- Real-Time Atualizações: Os dados de desempenho são atualizados dinamicamente ao selecionar o botão Atualizar

- Exibição de Custo Relativo: Mostra o custo relativo de aceder à memória de diferentes nós NUMA

Informação Exibida:

- Matriz NxN onde N = número de nós NUMA

- Custo de acesso à memória do nó NUMA de origem (linha) para o nó NUMA de destino (coluna)

- Valores numéricos que mostram os custos relativos de desempenho

- As células diagonais mostram acesso local à memória (tipicamente o custo mais baixo)

Grelha de Desempenho NUMA a mostrar custos de acesso à memória

Grelha de Desempenho NUMA a mostrar custos de acesso à memória

Compreender a Grelha:

- Elementos diagonais: Representam o acesso à memória local (nó a aceder à sua própria memória) - tipicamente os valores mais baixos

- Elementos fora da diagonal: Representam acesso remoto à memória com custos relativos mais elevados

- Simetria: A matriz pode não ser perfeitamente simétrica, pois os custos de acesso podem variar consoante a direção

Casos de Uso:

- Identificação de gargalos de desempenho relacionados com NUMA

- Otimização das estratégias de alocação de memória

- Processo de planeamento/fixação de threads para sistemas NUMA

- Compreensão das penalizações de acesso à memória entre nós

6. Vista de Distância do Núcleo

A Vista de Distância do Núcleo apresenta um mapa de calor detalhado dos custos de comunicação entre os núcleos individuais da CPU, fornecendo informações sobre a latência entre núcleos e eficiência da comunicação.

Caraterísticas:

-

Core-Level Mapa de Calor: Matriz codificada por cores que mostra distâncias relativas entre núcleos

- Verde/Azul = Baixa latência (mesmo cluster de núcleos, cache partilhada)

- Amarelo/Laranja = Latência média (mesmo socket, cluster diferente)

- Vermelho = Alta latência (socket diferente ou nó de NUMA)

- Exploração Interativa: Passe o rato sobre a tela da grelha para ver informações detalhadas sobre distâncias

- Análise Granular: Mostra as relações núcleo-núcleo com a mais fina granularidade

- Atualização Dinâmica: Use o botão de Atualização para obter dinamicamente dados atualizados de distância do núcleo

Informação Exibida:

- Matriz NxN onde N = número de processadores lógicos

- Distância/latência relativa do núcleo de origem (linha) ao núcleo de destino (coluna)

- Codificação por cores para identificação visual rápida das relações centrais

- Métricas detalhadas de distância no painel de detalhes

Mapa de calor da Distância entre Núcleos mostrando os custos de comunicação núcleo-a-núcleo

Mapa de calor da Distância entre Núcleos mostrando os custos de comunicação núcleo-a-núcleo

Compreender o Mapa de Distâncias:

- Elementos diagonais: Sempre zero (núcleo para si próprio)

- Baixa distância (verde): Os núcleos partilham cache L2 ou L3

- Média distância (amarelo): Núcleos no mesmo socket mas domínios de cache diferentes

- Distância alta (vermelho): Núcleos em sockets diferentes ou nós NUMA

Casos de Uso:

- Otimização de afinidade de threads

- Compreender domínios de coerência de cache

- Identificação de pares de núcleos ótimos para comunicações de threads

- Análise do desempenho de aplicações multi-thread

- Planeamento de estratégias de imobilização de CPU para aplicações de baixa latência

Funcionalidades Interativas

Seleção Principal e Detalhes

Clicar num núcleo em qualquer vista (Núcleo, NUMA ou Soquete) apresenta informação detalhada no painel inferior de detalhes:

- Informação do Processador: Número lógico do processador, máscara e afinidade

-

Hierarquia de Cache:

- Cache de Dados L1 (tamanho, associatividade, tamanho da linha)

- Cache de Instruções L1 (tamanho, associatividade, tamanho da linha)

- Cache L2 (tamanho, associatividade, tamanho da linha)

- Cache L3 (tamanho, associatividade, tamanho da linha)

- Informação de Topologia: atribuições de nó NUMA, socket e grupos de processadores

- Tipo de Núcleo: P-Core, E-Core ou designação padrão de núcleo

Funcionalidade de Pesquisa

A vista de Funcionalidades da CPU inclui uma barra de pesquisa que permite localizar rapidamente características específicas do processador:

- Clique no ícone de pesquisa

- Digite o nome ou abreviatura da funcionalidade

- A lista filtra automaticamente para mostrar características correspondentes

- Limpe a pesquisa para restaurar a lista completa

Alternar o Mapa de Cache

Na Vista Core, alterne entre dois modos de visualização:

- Modo Padrão: Mostra os núcleos na sua disposição lógica

- Modo de Mapa de Cache: Reorganiza os núcleos para visualizar as relações de partilha de cache

Navegação entre Visualizações

- Use o painel de navegação esquerdo para alternar entre vistas

- Ao visualizar um nó ou socket NUMA específico, clicar novamente na mesma visualização retorna à visão geral.

- A vista atual está destacada no painel de navegação

Definições e Personalização

Acede às definições através da opção Definições no menu de navegação.

Definições de Aparência

Opções de Tema:

- Luz: Esquema de cores de luz otimizado para ambientes luminosos

- Escuro: Esquema de cores escuro para reduzir a fadiga ocular

- Padrão do Sistema: Corresponde automaticamente à sua preferência de tema Windows

Salvar em arquivo

Exportar Dados de Topologia Central:

- Use a opção Guardar para despejar dados da topologia do núcleo para um ficheiro

- O formato de saída é idêntico ao da saída da ferramenta de linha de comandos

Compreender a Topologia do Seu Sistema

Tipos de Núcleo (Arquitetura Híbrida)

CPUs modernas podem apresentar arquiteturas híbridas com diferentes tipos de núcleos:

- P-Cores (Performance): Núcleos de alto desempenho otimizados para cargas de trabalho monofilamentares e exigentes

- E-Cores (Eficiência): Núcleos energeticamente eficientes otimizados para tarefas em segundo plano e cargas de trabalho multi-thread

A interface Coreinfo identifica e diferencia claramente estes tipos de núcleos em todas as vistas aplicáveis.

Arquitetura NUMA

O que é o NUMA? O Acesso à Memória Não Uniforme (NUMA) é um design de memória onde cada processador possui memória local à qual pode aceder rapidamente e memória remota que requer comunicação entre processadores.

Porque é importante:

- O acesso à memória local é significativamente mais rápido do que o acesso remoto

- O desempenho da aplicação pode ser drasticamente afetado pela colocação no NUMA

- Compreender a topologia NUMA é fundamental para computação de alto desempenho

Usar a interface Coreinfo para otimização NUMA:

- Use a Visualização NUMA para compreender a topologia NUMA do seu sistema

- Consulte a Visualização de Desempenho da NUMA para ver os custos de acesso à memória

- Otimizar a colocação de threads/processos com base nas atribuições de nós NUMA

- Utilize a Visão de Distância do Núcleo para compreender a comunicação entre núcleos dentro e entre nós NUMA.

Hierarquia de cache

Níveis de Cache:

- Cache L1: Menor e mais rápido, dividido em caches de dados e instruções

- Cache L2: Cache unificada maior, tipicamente privada para cada núcleo

- Cache L3: A maior cache unificada, frequentemente partilhada entre múltiplos núcleos

Utilização da Informação de Cache:

- Compreender quais os núcleos que partilham recursos de cache

- Otimizar a localidade de dados para núcleos que partilham cache

- Use o modo Cache Map na Core View para visualizar domínios de cache

Utilização do Coreinfo a partir da linha de comandos

Para cada recurso, ele mostra um mapa dos processadores visíveis do sistema operacional que correspondem aos recursos especificados, com '*' representando os processadores aplicáveis. Por exemplo, em um sistema de 4 núcleos, uma linha na saída de cache com um mapa de compartilhado pelos núcleos 3 e 4.

Utilização:

coreinfo [-c][-f][-g][-l][-n][-s][-m][-v]

| Parâmetro | Description |

|---|---|

| -c | Despeje informações em núcleos. |

| -f | Despeje as informações do recurso principal. |

| -g | Despeje informações em grupos. |

| -l | Despeje informações em caches. |

| -n | Despeje informações em nós NUMA. |

| -s | Despeje informações em soquetes. |

| -m | Despeje o custo de acesso NUMA. |

| -v | Despeje apenas recursos relacionados à virtualização, incluindo suporte para conversão de endereços de segundo nível. (requer direitos administrativos nos sistemas Intel). |

Todas as opções, exceto, -v são selecionadas por defeito.

Saída Coreinfo:

Coreinfo v4.0 - Dump information on system CPU and memory topology

Copyright © 2008-2025 Mark Russinovich

Sysinternals - www.sysinternals.com

Intel(R) Core(TM) Ultra 7 165U

Intel64 Family 6 Model 170 Stepping 4, GenuineIntel

Microcode signature: 0000001E

Processor signature: 000A06A4

Maximum implemented CPUID leaves: 00000023 (Basic), 80000008 (Extended).

Maximum implemented address width: 48 bits (virtual), 46 bits (physical).

HTT * Hyperthreading enabled

CET * Supports Control Flow Enforcement Technology

Kernel CET - Kernel-mode CET Enabled

User CET * User-mode CET Allowed

X64 * Supports 64-bit mode

SMX - Supports Intel trusted execution

SKINIT - Supports AMD SKINIT

SGX - Supports Intel SGX

NX * Supports no-execute page protection

SMEP * Supports Supervisor Mode Execution Prevention

SMAP * Supports Supervisor Mode Access Prevention

PAGE1GB * Supports 1 GB large pages

PAE * Supports > 32-bit physical addresses

PAT * Supports Page Attribute Table

PSE * Supports 4 MB pages

PSE36 * Supports > 32-bit address 4 MB pages

PGE * Supports global bit in page tables

SS * Supports bus snooping for cache operations

VME * Supports Virtual-8086 mode

RDWRFSGSBASE * Supports direct GS/FS base access

FPU * Implements i387 floating point instructions

MMX * Supports MMX instruction set

MMXEXT - Implements AMD MMX extensions

3DNOW - Supports 3DNow! instructions

3DNOWEXT - Supports 3DNow! extension instructions

SSE * Supports Streaming SIMD Extensions

SSE2 * Supports Streaming SIMD Extensions 2

SSE3 * Supports Streaming SIMD Extensions 3

SSSE3 * Supports Supplemental SIMD Extensions 3

SSE4a - Supports Streaming SIMDR Extensions 4a

SSE4.1 * Supports Streaming SIMD Extensions 4.1

SSE4.2 * Supports Streaming SIMD Extensions 4.2

AES * Supports AES extensions

AVX * Supports AVX instruction extensions

AVX2 * Supports AVX2 instruction extensions

AVX-512-F - Supports AVX-512 Foundation instructions

AVX-512-DQ - Supports AVX-512 double and quadword instructions

AVX-512-IFAMA - Supports AVX-512 integer Fused multiply-add instructions

AVX-512-PF - Supports AVX-512 prefetch instructions

AVX-512-ER - Supports AVX-512 exponential and reciprocal instructions

AVX-512-CD - Supports AVX-512 conflict detection instructions

AVX-512-BW - Supports AVX-512 byte and word instructions

AVX-512-VL - Supports AVX-512 vector length instructions

FMA * Supports FMA extensions using YMM state

MSR * Implements RDMSR/WRMSR instructions

MTRR * Supports Memory Type Range Registers

XSAVE * Supports XSAVE/XRSTOR instructions

OSXSAVE * Supports XSETBV/XGETBV instructions

RDRAND * Supports RDRAND instruction

RDSEED * Supports RDSEED instruction

CMOV * Supports CMOVcc instruction

CLFSH * Supports CLFLUSH instruction

CX8 * Supports compare and exchange 8-byte instructions

CX16 * Supports CMPXCHG16B instruction

BMI1 * Supports bit manipulation extensions 1

BMI2 * Supports bit manipulation extensions 2

ADX * Supports ADCX/ADOX instructions

DCA - Supports prefetch from memory-mapped device

F16C * Supports half-precision instruction

FXSR * Supports FXSAVE/FXSTOR instructions

FFXSR - Supports optimized FXSAVE/FSRSTOR instruction

MONITOR * Supports MONITOR and MWAIT instructions

MOVBE * Supports MOVBE instruction

ERMSB * Supports Enhanced REP MOVSB/STOSB

PCLMULDQ * Supports PCLMULDQ instruction

POPCNT * Supports POPCNT instruction

LZCNT * Supports LZCNT instruction

SEP * Supports fast system call instructions

LAHF-SAHF * Supports LAHF/SAHF instructions in 64-bit mode

HLE - Supports Hardware Lock Elision instructions

RTM - Supports Restricted Transactional Memory instructions

DE * Supports I/O breakpoints including CR4.DE

DTES64 - Can write history of 64-bit branch addresses

DS - Implements memory-resident debug buffer

DS-CPL - Supports Debug Store feature with CPL

PCID * Supports PCIDs and settable CR4.PCIDE

INVPCID * Supports INVPCID instruction

PDCM * Supports Performance Capabilities MSR

RDTSCP * Supports RDTSCP instruction

TSC * Supports RDTSC instruction

TSC-DEADLINE * Local APIC supports one-shot deadline timer

TSC-INVARIANT * TSC runs at constant rate

xTPR * Supports disabling task priority messages

EIST * Supports Enhanced Intel Speedstep

ACPI * Implements MSR for power management

TM * Implements thermal monitor circuitry

TM2 * Implements Thermal Monitor 2 control

APIC * Implements software-accessible local APIC

x2APIC * Supports x2APIC

CNXT-ID - L1 data cache mode adaptive or BIOS

MCE * Supports Machine Check, INT18 and CR4.MCE

MCA * Implements Machine Check Architecture

PBE * Supports use of FERR#/PBE# pin

PSN - Implements 96-bit processor serial number

HTT * Hyperthreading

PREFETCHW * PrefetchW instruction support

HYPERVISOR * Hypervisor is present

VMX - Supports Intel hardware-assisted virtualization

EPT - Supports Intel extended page tables (SLAT)

URG - Supports Intel unrestricted guest

Logical to Physical Processor Map:

**------------ Physical Processor 0 (Hyperthreaded)

--*----------- Physical Processor 1

---*---------- Physical Processor 2

----*--------- Physical Processor 3

-----*-------- Physical Processor 4

------*------- Physical Processor 5

-------*------ Physical Processor 6

--------*----- Physical Processor 7

---------*---- Physical Processor 8

----------**-- Physical Processor 9 (Hyperthreaded)

------------*- Physical Processor 10

-------------* Physical Processor 11

Logical Processor to Socket Map:

************** Socket 0

Logical Processor to NUMA Node Map:

************** NUMA Node 0

No NUMA nodes.

Logical Processor to Cache Map:

**------------ Data Cache 0, Level 1, 48 KB, Assoc 12, LineSize 64

**------------ Instruction Cache 0, Level 1, 64 KB, Assoc 16, LineSize 64

**------------ Unified Cache 0, Level 2, 2 MB, Assoc 16, LineSize 64

************-- Unified Cache 1, Level 3, 12 MB, Assoc 12, LineSize 64

--*----------- Data Cache 1, Level 1, 32 KB, Assoc 8, LineSize 64

--*----------- Instruction Cache 1, Level 1, 64 KB, Assoc 8, LineSize 64

--****-------- Unified Cache 2, Level 2, 2 MB, Assoc 16, LineSize 64

---*---------- Data Cache 2, Level 1, 32 KB, Assoc 8, LineSize 64

---*---------- Instruction Cache 2, Level 1, 64 KB, Assoc 8, LineSize 64

----*--------- Data Cache 3, Level 1, 32 KB, Assoc 8, LineSize 64

----*--------- Instruction Cache 3, Level 1, 64 KB, Assoc 8, LineSize 64

-----*-------- Data Cache 4, Level 1, 32 KB, Assoc 8, LineSize 64

-----*-------- Instruction Cache 4, Level 1, 64 KB, Assoc 8, LineSize 64

------*------- Data Cache 5, Level 1, 32 KB, Assoc 8, LineSize 64

------*------- Instruction Cache 5, Level 1, 64 KB, Assoc 8, LineSize 64

------****---- Unified Cache 3, Level 2, 2 MB, Assoc 16, LineSize 64

-------*------ Data Cache 6, Level 1, 32 KB, Assoc 8, LineSize 64

-------*------ Instruction Cache 6, Level 1, 64 KB, Assoc 8, LineSize 64

--------*----- Data Cache 7, Level 1, 32 KB, Assoc 8, LineSize 64

--------*----- Instruction Cache 7, Level 1, 64 KB, Assoc 8, LineSize 64

---------*---- Data Cache 8, Level 1, 32 KB, Assoc 8, LineSize 64

---------*---- Instruction Cache 8, Level 1, 64 KB, Assoc 8, LineSize 64

----------**-- Data Cache 9, Level 1, 48 KB, Assoc 12, LineSize 64

----------**-- Instruction Cache 9, Level 1, 64 KB, Assoc 16, LineSize 64

----------**-- Unified Cache 4, Level 2, 2 MB, Assoc 16, LineSize 64

------------*- Data Cache 10, Level 1, 32 KB, Assoc 8, LineSize 64

------------*- Instruction Cache 10, Level 1, 64 KB, Assoc 8, LineSize 64

------------** Unified Cache 5, Level 2, 2 MB, Assoc 16, LineSize 64

-------------* Data Cache 11, Level 1, 32 KB, Assoc 8, LineSize 64

-------------* Instruction Cache 11, Level 1, 64 KB, Assoc 8, LineSize 64

Logical Processor to Group Map:

************** Group 0

Coreinfo(3 MB)Executar agora a partir do Sysinternals Live.

Coreinfo(3 MB)Executar agora a partir do Sysinternals Live.

Funciona em:

- Cliente: Windows 11 e superior.

- Servidor: Windows Server 2016 e superior.