Notatka

Dostęp do tej strony wymaga autoryzacji. Może spróbować zalogować się lub zmienić katalogi.

Dostęp do tej strony wymaga autoryzacji. Możesz spróbować zmienić katalogi.

Autor: Mark Russinovich

Opublikowano: 16 grudnia 2025 r.

Coreinfo(3 MB)

Coreinfo(3 MB)

Wprowadzenie

Coreinfo to narzędzie, które pokazuje mapowanie między procesorami logicznymi a procesorem fizycznym, węzłem NUMA i gniazdem, na którym się znajdują, a także pamięci podręcznej przypisanej do każdego procesora logicznego. Używa on interfejsów API systemu Windows niskiego poziomu (tryb użytkownika i tryb jądra) do pobierania szczegółowych informacji o topologii procesora CPU bezpośrednio z systemu operacyjnego. Wersja wiersza polecenia zwraca reprezentację przyporządkowania do procesora logicznego z użyciem gwiazdki, np. "*". Interfejs użytkownika udostępnia wiele wyspecjalizowanych widoków do eksplorowania różnych aspektów topologii procesora CPU systemu, w tym rdzeni logicznych i fizycznych, węzłów NUMA, gniazd, hierarchii pamięci podręcznej i metryk wydajności w czasie rzeczywistym. Informacje coreinfo są przydatne do uzyskiwania wglądu w topologię procesora i pamięci podręcznej systemu.

Instalacja

Wyodrębnij archiwum do katalogu, a następnie uruchom polecenie Coreinfo, wpisując z tego katalogu Coreinfo / Coreinfo64 lub Coreinfo64a, w zależności od architektury. Uruchom CoreInfoEx / CoreInfoEx64 / CoreInfoEx64a wersję interfejsu użytkownika.

Uwaga: Niektóre funkcje mogą wymagać uprawnień administracyjnych do pełnego pobierania informacji.

Omówienie interfejsu użytkownika

Interfejs użytkownika Coreinfo składa się z kilku kluczowych składników:

Układ okna głównego

- Górny panel: wyświetla informacje o systemie, w tym nazwę procesora CPU, architekturę i liczby rdzeni

- Okienko nawigacji (po lewej): zapewnia szybki dostęp do różnych widoków

- Obszar zawartości (Centrum): pokazuje dane i wizualizacje wybranego widoku

- Okienko szczegółów (dolne): wyświetla szczegółowe informacje o zaznaczonych rdzeniach lub komórkach

- Ustawienia: dostęp do opcji wyglądu i preferencji aplikacji

Okno główne z pełnym układem UI, tryb ciemny

Okno główne z pełnym układem UI, tryb ciemny

Widoki nawigacji

Okienko nawigacji po lewej stronie zapewnia dostęp do sześciu wyspecjalizowanych widoków:

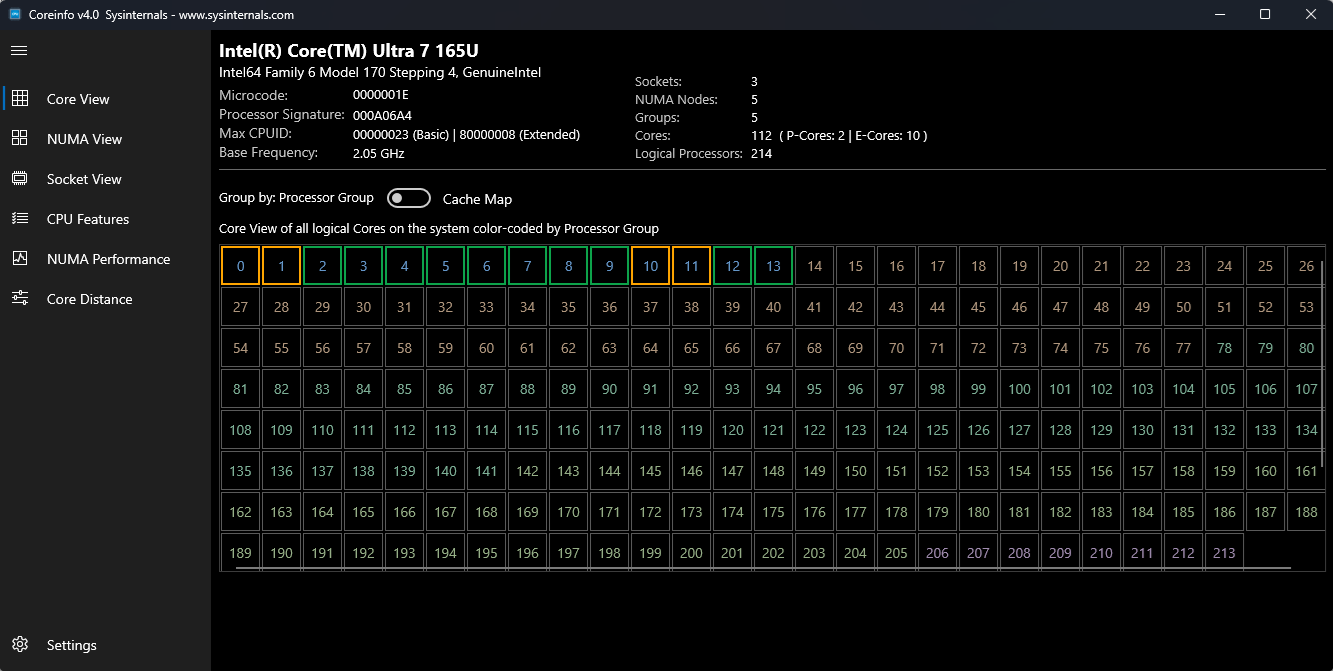

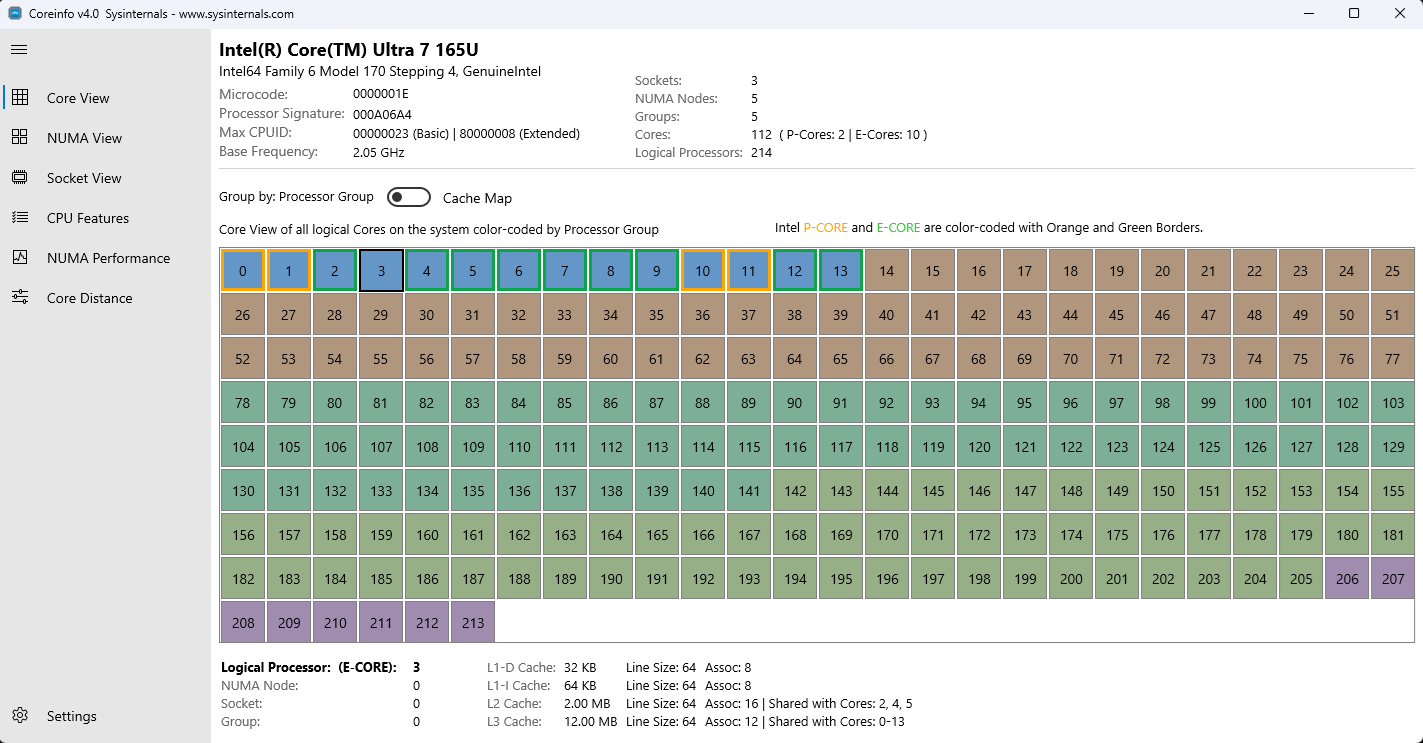

1. Widok podstawowy

Widok podstawowy wyświetla wszystkie procesory logiczne w systemie w układzie siatki, pokazując relację między rdzeniami logicznymi a ich zasobami fizycznymi.

Funkcje:

- Układ siatki: Każda komórka reprezentuje procesor logiczny

-

Kluczowe wskaźniki typów:

- Rdzenie P (rdzenie wydajności) — wyróżnione kolorem

- Rdzenie E-Core (rdzenie wydajności) — kolorowane inaczej

- Rdzenie standardowe — domyślne kolorowanie

- Przełącznik mapowania pamięci podręcznej: przełączanie między widokiem domyślnym a widokiem hierarchii pamięci podręcznej

- Wybór interaktywny: kliknij dowolny rdzeń, aby wyświetlić szczegółowe informacje w dolnym okienku

Wyświetlane informacje:

- Numer procesora logicznego

- Typ rdzenia (P-Core/E-Core, jeśli ma to zastosowanie)

- Skojarzone poziomy pamięci podręcznej (L1, L2, L3)

- Przypisanie węzła NUMA

- Przypisanie gniazda

- Przypisanie grupy

Widok rdzenia przedstawiający procesory logiczne w układzie siatkowym

Widok rdzenia przedstawiający procesory logiczne w układzie siatkowym

Informacje panelu szczegółów (po wybraniu rdzenia):

- Maska procesora i koligacja

- Hierarchia pamięci podręcznej (pamięć podręczna danych, pamięć podręczna instrukcji, ujednolicona pamięć podręczna)

- Rozmiary pamięci podręcznej i asocjacyjność

- Rozmiary wierszy pamięci podręcznej

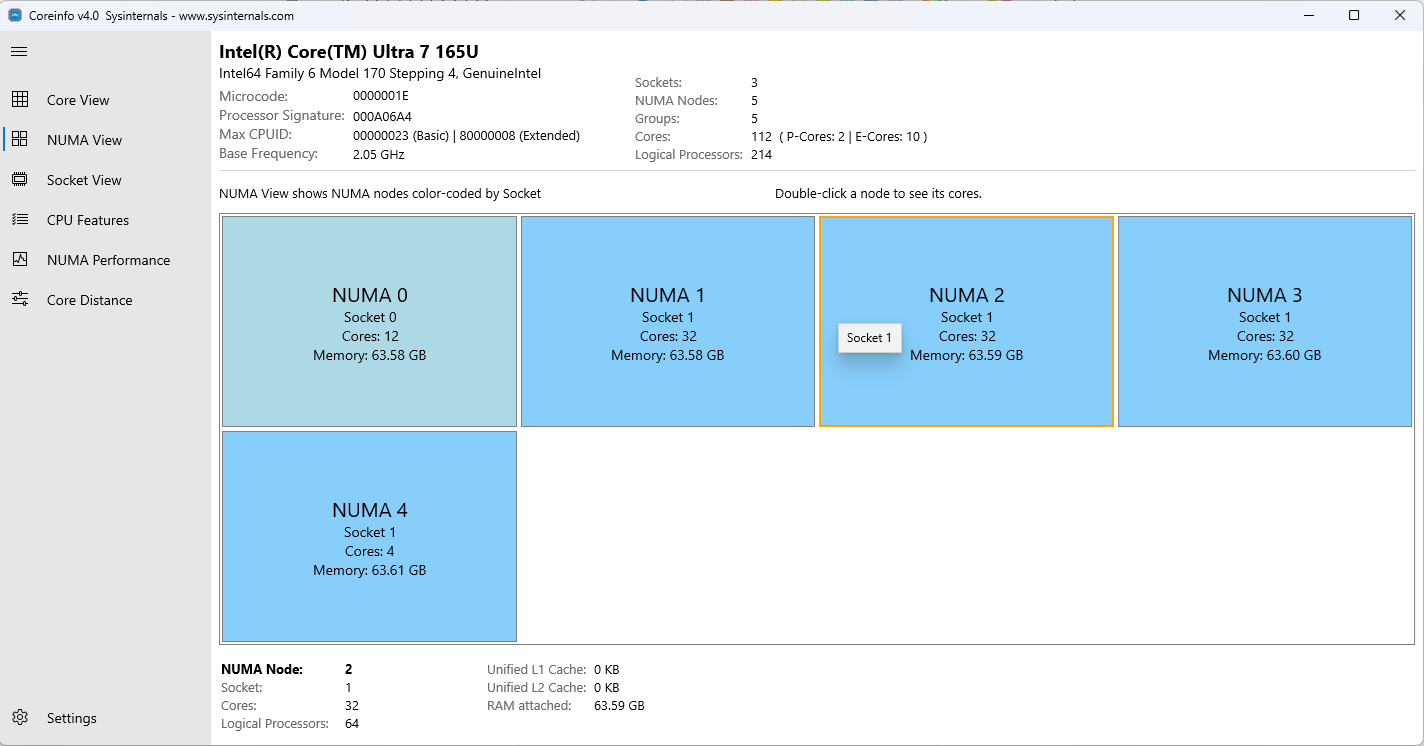

2. Widok NUMA

Widok NUMA (Niejednolity Dostęp do Pamięci) organizuje rdzenie według przypisań węzłów NUMA, co ułatwia zrozumienie lokalizacji pamięci i wzorców jej dostępu.

Funkcje:

- Organizacja oparta na węzłach: rdzenie pogrupowane według węzła NUMA

- Rdzenie fizyczne i logiczne: pokazuje obie liczby dla każdego węzła

- Informacje o pamięci: wyświetla dostępną pamięć na węzeł NUMA

-

Nawigacja interaktywna:

- Kliknij na jedną z węzłów NUMA, aby wyświetlić jej szczegóły w dolnym panelu szczegółów

- Kliknij dwukrotnie węzeł NUMA, aby przejść do widoku podstawowego pokazującego wszystkie rdzenie z wybranego węzła NUMA

- Wyświetlanie hierarchiczne: pokazuje relację między węzłami NUMA i rdzeniami

Wyświetlane informacje:

- Liczba węzłów NUMA

- Rdzenie na węzeł NUMA (fizyczny i logiczny)

- Pojemność pamięci na węzeł

- Dystrybucja podstawowa między węzłami

- Liczba rdzeni efektywności (jeśli dotyczy)

Widok NUMA pokazujący rdzenie zorganizowane według węzłów NUMA

Widok NUMA pokazujący rdzenie zorganizowane według węzłów NUMA

Przypadki użycia:

- Optymalizowanie wzorców dostępu do pamięci

- Opis wydajności aplikacji obsługujących NUMA

- Planowanie rozmieszczania wątków/procesów w celu uzyskania optymalnej wydajności

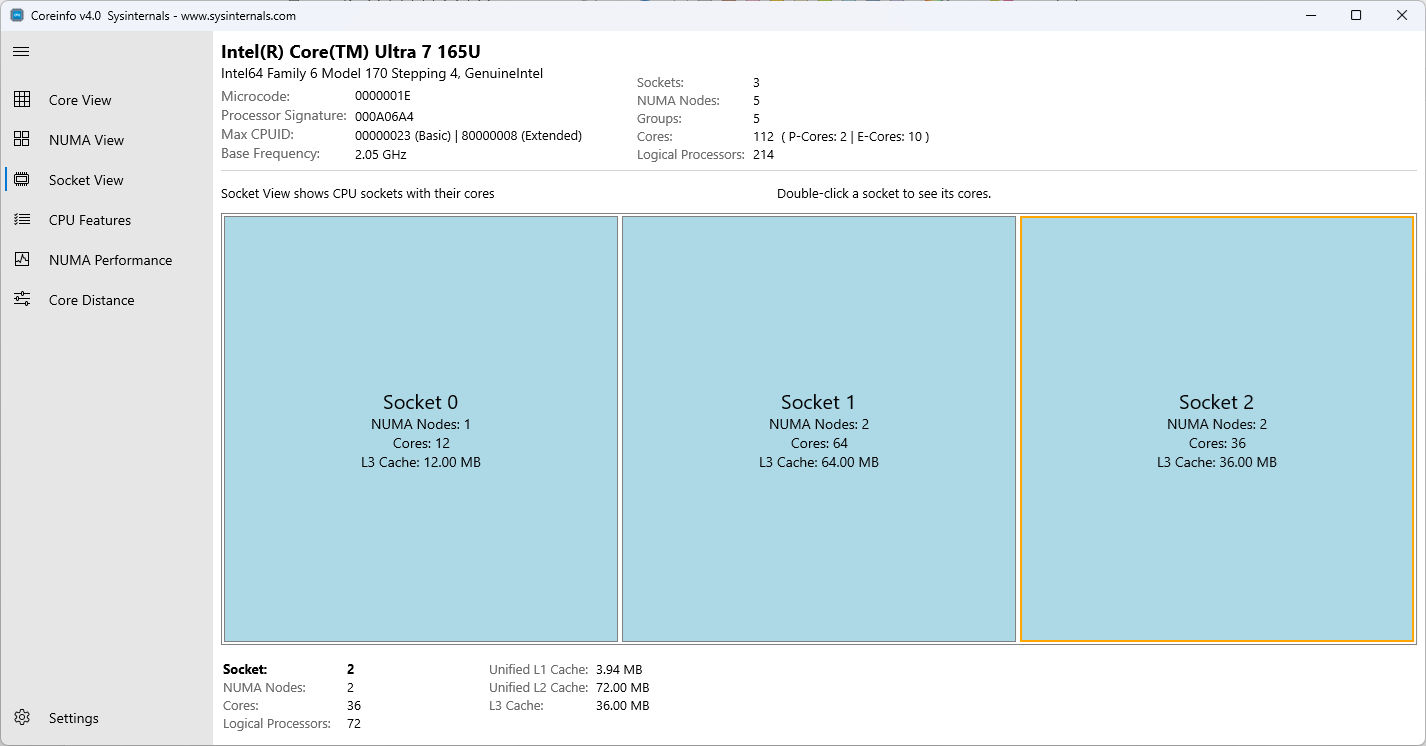

3. Widok gniazda

Widok gniazda wyświetla rdzenie zorganizowane według ich fizycznych gniazd procesora, co jest przydatne do zrozumienia systemów z wieloma gniazdami i dystrybucji zasobów na poziomie gniazda.

Funkcje:

- Grupowanie oparte na gniazdach: rdzenie zorganizowane według fizycznego gniazda

- Informacje o gniazdach: liczba gniazd i dystrybucja rdzeni

-

Nawigacja interaktywna:

- Kliknij raz gniazdo, aby wyświetlić szczegóły w dolnym panelu szczegółów

- Kliknij dwukrotnie gniazdo, aby przejść do widoku podstawowego pokazującego wszystkie rdzenie z wybranego gniazda

- Udostępnianie Cache: wizualizacja rdzeni współdzielących cache na poziomie gniazda

Wyświetlane informacje:

- Liczba gniazd fizycznych

- Rdzenie na gniazdo (fizyczne i logiczne)

- Informacje o pamięci podręcznej na poziomie gniazda

- Węzły NUMA na każde gniazdo

rdzenie uporządkowane według gniazd procesora

rdzenie uporządkowane według gniazd procesora

Przypadki użycia:

- Analiza systemu z wieloma gniazdami

- Omówienie kosztów komunikacji między gniazdami

- Planowanie dystrybucji obciążeń na serwerach z wieloma gniazdami

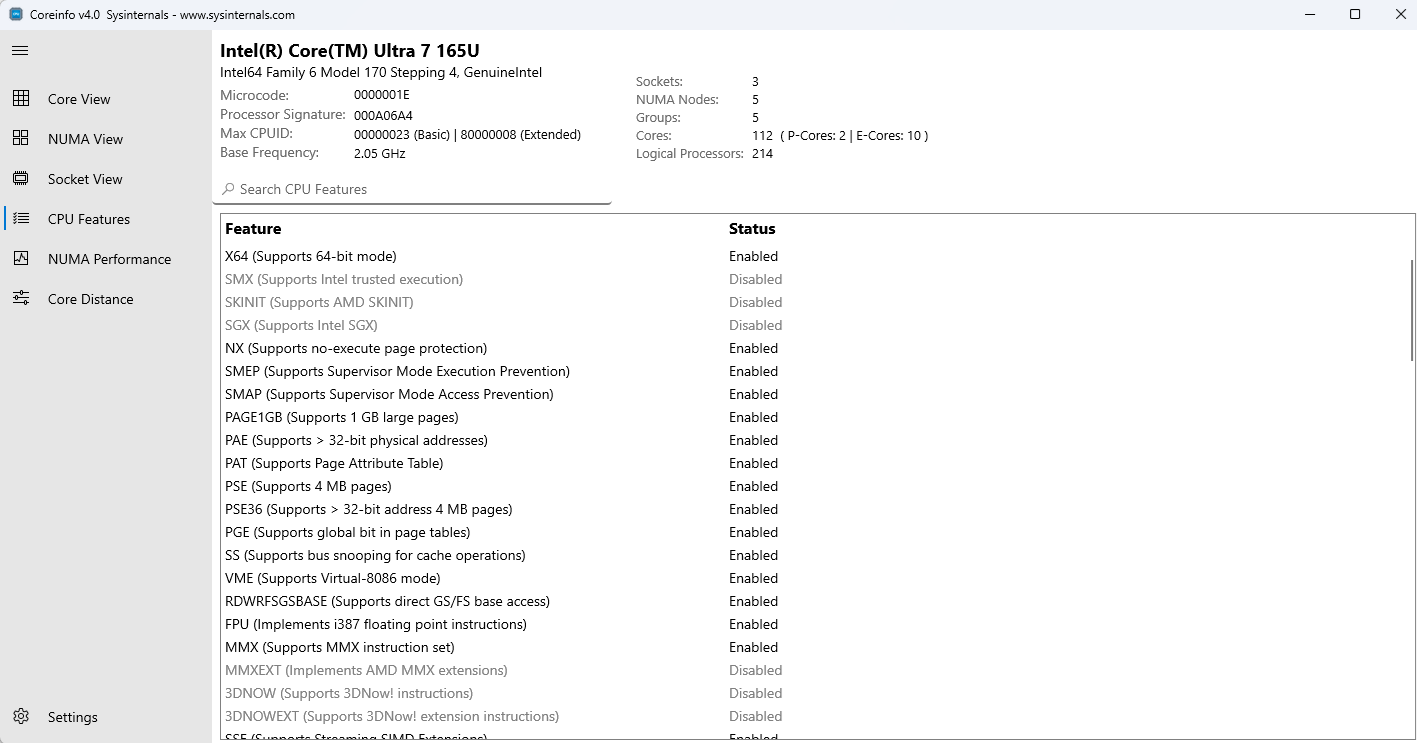

4. Widok funkcji procesora CPU

Widok funkcji procesora CPU zawiera kompleksową listę możliwości procesora, rozszerzeń zestawu instrukcji i funkcji sprzętowych obsługiwanych przez procesor.

Funkcje:

- Lista z możliwością wyszukiwania: szybkie znajdowanie określonych funkcji procesora CPU przy użyciu paska wyszukiwania

-

Wskaźniki stanu: Wyraźne wizualne oznaczenie obsługiwanych/nieobsługiwanych funkcji z użyciem kodowania kolorystycznego

- Obsługiwane funkcje są wyświetlane w normalnym kolorze

- Nieobsługiwane/wyłączone funkcje są wyszarywane

-

Kategorie funkcji:

- Wirtualizacja (VMX, SVM, HYPERVISOR)

- Obsługa 64-bitowa (EM64T, NX)

- Zestawy instrukcji (SSE, AVX, AES itp.)

- Zarządzanie energią (EIST, ACPI, Thermal)

- Funkcje zabezpieczeń (SMX, SKINIT)

- Funkcje pamięci (PAE, PAT, PSE)

- Funkcje debugowania i monitorowania

Wyświetlane informacje:

- Skrót funkcji

- Stan funkcji (obsługiwany/nieobsługiwany)

- Pełny opis funkcji (w okienku szczegółów)

Widok funkcji procesora z wyświetloną listą możliwości procesora

Widok funkcji procesora z wyświetloną listą możliwości procesora

Uwaga: Niektóre funkcje wirtualizacji (takie jak VMX, SVM) mogą być niepoprawnie zgłaszane jako niedostępne podczas uruchamiania z aktywną funkcją hypervisor lub podczas uruchamiania z poziomu maszyny wirtualnej. Coreinfo musi być uruchomiony w systemie bez działającego hipernadzorcy, aby uzyskać dokładne wyniki.

Przypadki użycia:

- Weryfikowanie dostępności zestawu instrukcji przed wdrożeniem aplikacji

- Sprawdzanie obsługi wirtualizacji

- Zrozumienie generacji i możliwości procesora

- Debugowanie problemów z wydajnością związanych z brakującymi cechami procesora

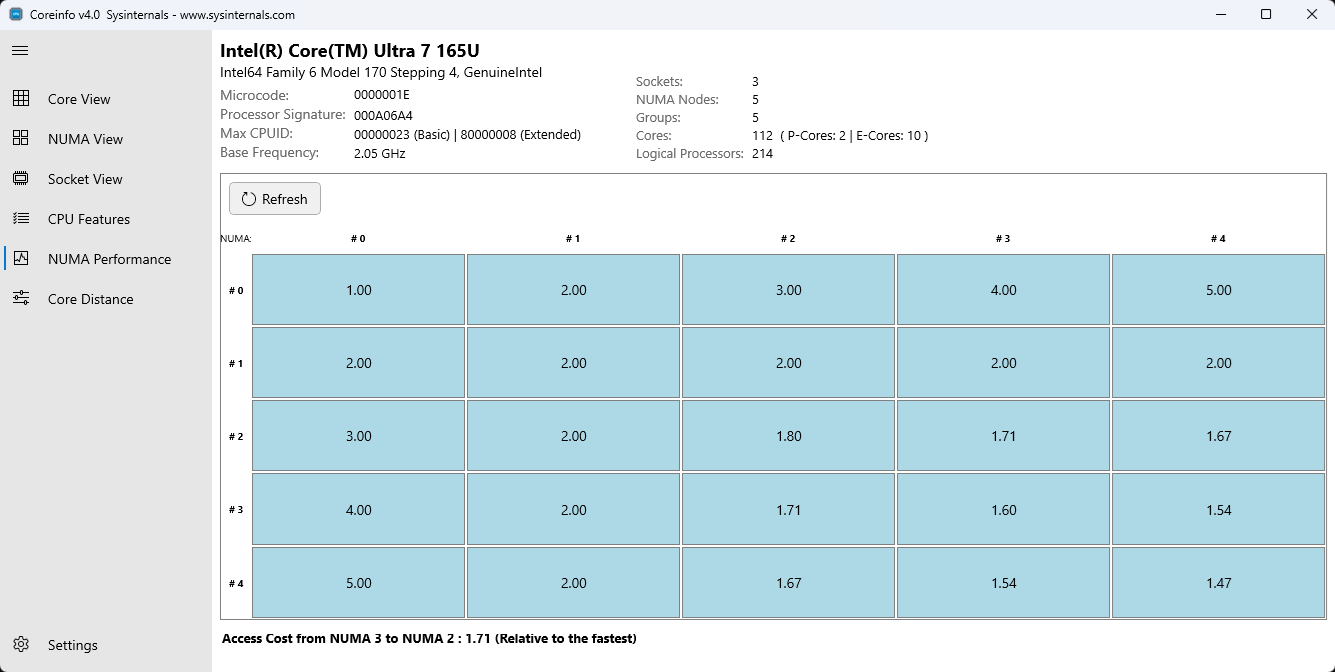

5. Widok wydajności NUMA

Widok wydajności NUMA udostępnia wizualizację siatki, przedstawiającą koszty dostępu do pamięci między węzłami NUMA, co pomaga identyfikować wąskie gardła wydajności w systemach NUMA.

Funkcje:

- Wizualizacja siatki: macierz wyświetlającą względne koszty dostępu do pamięci między węzłami NUMA

- Macierz interaktywna: umieść kursor na komórkach, aby wyświetlić szczegółowe informacje o wydajności

- Aktualizacje w czasie rzeczywistym: dane dotyczące wydajności są dynamicznie aktualizowane po naciśnięciu przycisku Odśwież

- Wyświetlanie względnego kosztu: pokazuje względny koszt uzyskiwania dostępu do pamięci z różnych węzłów NUMA

Wyświetlane informacje:

- Macierz NxN, gdzie N = liczba węzłów NUMA

- Koszt dostępu do pamięci z węzła NUMA źródłowego (wiersz) do węzła NUMA docelowego (kolumna)

- Wartości liczbowe przedstawiające względne koszty wydajności

- Komórki ukośne pokazują dostęp do pamięci lokalnej (zazwyczaj najniższy koszt)

Siatka wydajności NUMA przedstawiająca koszty dostępu pamięci

Siatka wydajności NUMA przedstawiająca koszty dostępu pamięci

Informacje o siatce:

- Elementy ukośne: Reprezentują dostęp do pamięci lokalnej (węzeł uzyskuje dostęp do własnej pamięci) — zazwyczaj najniższe wartości

- Elementy poza przekątną: reprezentują dostęp do pamięci zdalnej z wyższymi kosztami względnymi

- Symetria: Macierz może nie być idealnie symetryczna, ponieważ koszty dostępu mogą się różnić w zależności od kierunku

Przypadki użycia:

- Identyfikowanie ograniczeń wydajności związanych z NUMA

- Optymalizowanie strategii alokacji pamięci

- Planowanie i przypinanie wątków dla systemów NUMA

- Zrozumienie kar za dostęp do pamięci między węzłami

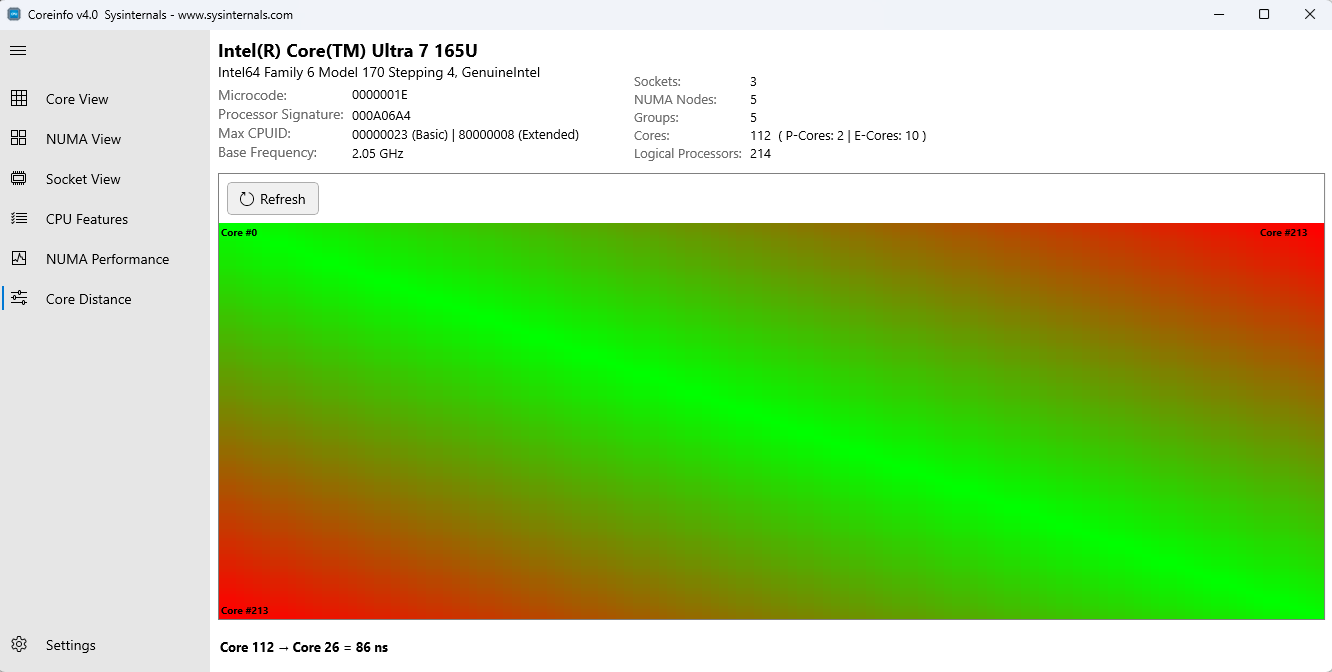

6. Widok na dystans rdzeniowy

Widok odległości rdzeni przedstawia szczegółową mapę cieplną kosztów komunikacji między poszczególnymi rdzeniami CPU, zapewniając wgląd w opóźnienia między rdzeniami i efektywność komunikacji między rdzeniami.

Funkcje:

-

Mapa cieplna poziomu rdzenia: matryca oznaczona kolorami przedstawiająca relatywne odległości między rdzeniami

- Zielony/Niebieski = małe opóźnienie (ten sam klaster podstawowy, udostępniona pamięć podręczna)

- Żółty/pomarańczowy = średnie opóźnienie (to samo gniazdo, inny klaster)

- Czerwony = duże opóźnienie (inne gniazdo lub węzeł NUMA)

- Eksploracja interaktywna: umieść kursor na kanwie siatki, aby wyświetlić szczegółowe informacje o odległości

- Granularna analiza: pokazuje relacje między rdzeniami na najdrobniejszym poziomie szczegółowości

- Odświeżanie dynamiczne: użyj przycisku Odśwież, aby dynamicznie uzyskać zaktualizowane dane odległości rdzenia

Wyświetlane informacje:

- Macierz NxN, gdzie N = liczba procesorów logicznych

- Względna odległość/opóźnienie od rdzenia źródłowego w wierszu do rdzenia docelowego w kolumnie.

- Kodowanie kolorami na potrzeby szybkiej wizualnej identyfikacji podstawowych relacji

- Szczegółowe metryki odległości w okienku szczegółów

Mapa cieplna odległości rdzenia przedstawiająca koszty komunikacji między rdzeniami

Mapa cieplna odległości rdzenia przedstawiająca koszty komunikacji między rdzeniami

Opis mapy odległości:

- Elementy diagonalne: Zawsze zero (rdzeń sam dla siebie)

- Niska odległość (zielony): Rdzenie współdzielą pamięć podręczną L2 lub L3.

- Średnia odległość (żółty): rdzenie na tym samym gniazdach, ale w różnych domenach pamięci podręcznej

- Duża odległość (czerwone): rdzenie w różnych gniazdach lub węzłach NUMA

Przypadki użycia:

- Optymalizacja koligacji wątków

- Informacje o domenach współistnienia pamięci podręcznej

- Identyfikowanie optymalnych par rdzeni do komunikowania wątków

- Analizowanie wydajności aplikacji wielowątowych

- Planowanie strategii przypinania procesora CPU dla aplikacji o małych opóźnieniach

Funkcje interakcyjne

Wybór rdzenia i szczegóły

Kliknięcie rdzenia w dowolnym widoku (Core, NUMA lub Socket) powoduje wyświetlenie szczegółowych informacji w dolnym okienku szczegółów:

- Informacje o procesorze: numer procesora logicznego, maska i koligacja

-

Hierarchia pamięci podręcznej:

- Pamięć podręczna danych L1 (rozmiar, kojarzenie, rozmiar wiersza)

- Pamięć podręczna instrukcji L1 (rozmiar, kojarzenie, rozmiar wiersza)

- Pamięć podręczna L2 (rozmiar, kojarzenie, rozmiar wiersza)

- Pamięć podręczna L3 (rozmiar, kojarzenie, rozmiar linii)

- Informacje o topologii: węzły NUMA, gniazda i przypisania grup

- Typ rdzenia: P-Core, E-Core lub standardowe oznaczenie rdzenia

Funkcja wyszukiwania

Widok Funkcje procesora CPU zawiera pasek wyszukiwania, który umożliwia szybkie lokalizowanie określonych funkcji procesora:

- Kliknij ikonę wyszukiwania

- Wpisz nazwę lub skrót funkcji

- Lista automatycznie filtruje w celu wyświetlenia pasujących funkcji

- Wyczyść wyszukiwanie, aby przywrócić pełną listę

Przełącznik mapy pamięci podręcznej

W widoku podstawowym przełącz się między dwoma trybami wizualizacji:

- Tryb domyślny: pokazuje rdzenie w ich układzie logicznym

- Tryb mapy pamięci podręcznej: reorganizuje rdzenie w celu wizualizacji relacji udostępniania pamięci podręcznej

Nawigacja między widokami

- Przełączanie między widokami za pomocą okienka nawigacji po lewej stronie

- Podczas przeglądania konkretnego węzła lub gniazda NUMA, ponowne kliknięcie tego samego widoku spowoduje powrót do widoku ogólnego.

- Bieżący widok jest wyróżniony w okienku nawigacji

Ustawienia i dostosowywanie

Dostęp do ustawień za pośrednictwem opcji Ustawienia w menu nawigacji.

Ustawienia wyglądu

Opcje motywu:

- Jasny: Jasny schemat kolorów zoptymalizowany pod kątem jasnych środowisk

- Ciemny: Ciemny schemat kolorów, aby zmniejszyć obciążenie oczu

- Ustawienie domyślne systemu: Automatycznie pasuje do preferencji motywu systemu Windows

Zapisz w pliku

Eksportuj podstawowe dane topologii:

- Użyj opcji Zapisz do, aby przenieść dane topologii rdzenia do pliku

- Format danych wyjściowych jest identyczny z danymi wyjściowymi narzędzia wiersza polecenia

Opis topologii systemu

Typy podstawowe (architektura hybrydowa)

Nowoczesne procesory CPU mogą zawierać architektury hybrydowe z różnymi typami rdzeni:

- Rdzenie P (wydajność): rdzenie o wysokiej wydajności zoptymalizowane pod kątem obciążeń jednowątkowych i wymagających

- E-Cores (Efektywność): wydajne energetycznie rdzenie zoptymalizowane pod kątem zadań w tle i obciążeń wielowątowych

Interfejs użytkownika Coreinfo wyraźnie identyfikuje i rozróżnia te typy rdzeni we wszystkich odpowiednich widokach.

Architektura NUMA

Co to jest architektura NUMA? Nieumundurowy dostęp do pamięci (NUMA) to projekt pamięci, w którym każdy procesor ma pamięć lokalną, do której może uzyskać szybki dostęp, oraz pamięć zdalną, która wymaga komunikacji między procesorami.

Dlaczego to ważne:

- Dostęp do pamięci lokalnej jest znacznie szybszy niż dostęp zdalny

- Na wydajność aplikacji może znacząco wpływać rozmieszczenie w architekturze NUMA.

- Zrozumienie topologii NUMA ma kluczowe znaczenie dla obliczeń o wysokiej wydajności

Korzystanie z interfejsu użytkownika Coreinfo na potrzeby optymalizacji NUMA:

- Używanie widoku NUMA do zrozumienia topologii NUMA systemu

- Sprawdź widok wydajności NUMA , aby wyświetlić koszty dostępu do pamięci

- Optymalizacja rozmieszczenia wątków/procesów w oparciu o przypisania węzłów NUMA

- Użyj Widoku Odległości Rdzenia, aby zrozumieć komunikację rdzeń-do-rdzeń w obrębie węzłów NUMA oraz między nimi.

Hierarchia pamięci podręcznej

Poziomy pamięci podręcznej:

- Pamięć podręczna L1: najmniejsza i najszybsza, podzielona na pamięć podręczną danych i instrukcji

- Pamięć podręczna L2: Większa ujednolicona pamięć podręczna, zwykle prywatna dla każdego rdzenia

- Pamięć podręczna L3: największa ujednolicona pamięć podręczna, często współdzielona między wieloma rdzeniami

Korzystanie z informacji o pamięci podręcznej:

- Zrozumieć, które rdzenie współdzielą zasoby pamięci podręcznej

- Optymalizowanie lokalizacji danych dla rdzeni współdzielących pamięć podręczną

- Wizualizowanie domen pamięci podręcznej za pomocą trybu mapy pamięci podręcznej w widoku podstawowym

Korzystanie z narzędzia Coreinfo z poziomu wiersza polecenia

Dla każdego zasobu jest wyświetlana mapa procesorów widocznych dla systemu operacyjnego, które odpowiadają określonym zasobom, z wartością "*" reprezentującą odpowiednie procesory. Na przykład w systemie 4-rdzeniowym wiersz w danych wyjściowych pamięci podręcznej z mapą współdzieloną przez rdzenie 3 i 4.

Usage:

coreinfo [-c][-f][-g][-l][-n][-s][-m][-v]

| Parametr | Opis |

|---|---|

| -c | Zrzut informacji na temat rdzeni. |

| -f | Informacje o funkcji zrzutu podstawowego. |

| -g | Zrzut informacji na temat grup. |

| -l | Zrzut informacji na temat pamięci podręcznych. |

| -n | Zrzut informacji na temat węzłów NUMA. |

| -s | Zrzut informacji na temat gniazd. |

| -m | Zrzuć koszt dostępu NUMA. |

| -v | Zrzut tylko funkcje związane z wirtualizacją, w tym obsługa tłumaczenia adresów drugiego poziomu. (wymaga uprawnień administracyjnych w systemach Intel). |

Wszystkie opcje z wyjątkiem -v są domyślnie zaznaczone.

Dane wyjściowe coreinfo:

Coreinfo v4.0 - Dump information on system CPU and memory topology

Copyright © 2008-2025 Mark Russinovich

Sysinternals - www.sysinternals.com

Intel(R) Core(TM) Ultra 7 165U

Intel64 Family 6 Model 170 Stepping 4, GenuineIntel

Microcode signature: 0000001E

Processor signature: 000A06A4

Maximum implemented CPUID leaves: 00000023 (Basic), 80000008 (Extended).

Maximum implemented address width: 48 bits (virtual), 46 bits (physical).

HTT * Hyperthreading enabled

CET * Supports Control Flow Enforcement Technology

Kernel CET - Kernel-mode CET Enabled

User CET * User-mode CET Allowed

X64 * Supports 64-bit mode

SMX - Supports Intel trusted execution

SKINIT - Supports AMD SKINIT

SGX - Supports Intel SGX

NX * Supports no-execute page protection

SMEP * Supports Supervisor Mode Execution Prevention

SMAP * Supports Supervisor Mode Access Prevention

PAGE1GB * Supports 1 GB large pages

PAE * Supports > 32-bit physical addresses

PAT * Supports Page Attribute Table

PSE * Supports 4 MB pages

PSE36 * Supports > 32-bit address 4 MB pages

PGE * Supports global bit in page tables

SS * Supports bus snooping for cache operations

VME * Supports Virtual-8086 mode

RDWRFSGSBASE * Supports direct GS/FS base access

FPU * Implements i387 floating point instructions

MMX * Supports MMX instruction set

MMXEXT - Implements AMD MMX extensions

3DNOW - Supports 3DNow! instructions

3DNOWEXT - Supports 3DNow! extension instructions

SSE * Supports Streaming SIMD Extensions

SSE2 * Supports Streaming SIMD Extensions 2

SSE3 * Supports Streaming SIMD Extensions 3

SSSE3 * Supports Supplemental SIMD Extensions 3

SSE4a - Supports Streaming SIMDR Extensions 4a

SSE4.1 * Supports Streaming SIMD Extensions 4.1

SSE4.2 * Supports Streaming SIMD Extensions 4.2

AES * Supports AES extensions

AVX * Supports AVX instruction extensions

AVX2 * Supports AVX2 instruction extensions

AVX-512-F - Supports AVX-512 Foundation instructions

AVX-512-DQ - Supports AVX-512 double and quadword instructions

AVX-512-IFAMA - Supports AVX-512 integer Fused multiply-add instructions

AVX-512-PF - Supports AVX-512 prefetch instructions

AVX-512-ER - Supports AVX-512 exponential and reciprocal instructions

AVX-512-CD - Supports AVX-512 conflict detection instructions

AVX-512-BW - Supports AVX-512 byte and word instructions

AVX-512-VL - Supports AVX-512 vector length instructions

FMA * Supports FMA extensions using YMM state

MSR * Implements RDMSR/WRMSR instructions

MTRR * Supports Memory Type Range Registers

XSAVE * Supports XSAVE/XRSTOR instructions

OSXSAVE * Supports XSETBV/XGETBV instructions

RDRAND * Supports RDRAND instruction

RDSEED * Supports RDSEED instruction

CMOV * Supports CMOVcc instruction

CLFSH * Supports CLFLUSH instruction

CX8 * Supports compare and exchange 8-byte instructions

CX16 * Supports CMPXCHG16B instruction

BMI1 * Supports bit manipulation extensions 1

BMI2 * Supports bit manipulation extensions 2

ADX * Supports ADCX/ADOX instructions

DCA - Supports prefetch from memory-mapped device

F16C * Supports half-precision instruction

FXSR * Supports FXSAVE/FXSTOR instructions

FFXSR - Supports optimized FXSAVE/FSRSTOR instruction

MONITOR * Supports MONITOR and MWAIT instructions

MOVBE * Supports MOVBE instruction

ERMSB * Supports Enhanced REP MOVSB/STOSB

PCLMULDQ * Supports PCLMULDQ instruction

POPCNT * Supports POPCNT instruction

LZCNT * Supports LZCNT instruction

SEP * Supports fast system call instructions

LAHF-SAHF * Supports LAHF/SAHF instructions in 64-bit mode

HLE - Supports Hardware Lock Elision instructions

RTM - Supports Restricted Transactional Memory instructions

DE * Supports I/O breakpoints including CR4.DE

DTES64 - Can write history of 64-bit branch addresses

DS - Implements memory-resident debug buffer

DS-CPL - Supports Debug Store feature with CPL

PCID * Supports PCIDs and settable CR4.PCIDE

INVPCID * Supports INVPCID instruction

PDCM * Supports Performance Capabilities MSR

RDTSCP * Supports RDTSCP instruction

TSC * Supports RDTSC instruction

TSC-DEADLINE * Local APIC supports one-shot deadline timer

TSC-INVARIANT * TSC runs at constant rate

xTPR * Supports disabling task priority messages

EIST * Supports Enhanced Intel Speedstep

ACPI * Implements MSR for power management

TM * Implements thermal monitor circuitry

TM2 * Implements Thermal Monitor 2 control

APIC * Implements software-accessible local APIC

x2APIC * Supports x2APIC

CNXT-ID - L1 data cache mode adaptive or BIOS

MCE * Supports Machine Check, INT18 and CR4.MCE

MCA * Implements Machine Check Architecture

PBE * Supports use of FERR#/PBE# pin

PSN - Implements 96-bit processor serial number

HTT * Hyperthreading

PREFETCHW * PrefetchW instruction support

HYPERVISOR * Hypervisor is present

VMX - Supports Intel hardware-assisted virtualization

EPT - Supports Intel extended page tables (SLAT)

URG - Supports Intel unrestricted guest

Logical to Physical Processor Map:

**------------ Physical Processor 0 (Hyperthreaded)

--*----------- Physical Processor 1

---*---------- Physical Processor 2

----*--------- Physical Processor 3

-----*-------- Physical Processor 4

------*------- Physical Processor 5

-------*------ Physical Processor 6

--------*----- Physical Processor 7

---------*---- Physical Processor 8

----------**-- Physical Processor 9 (Hyperthreaded)

------------*- Physical Processor 10

-------------* Physical Processor 11

Logical Processor to Socket Map:

************** Socket 0

Logical Processor to NUMA Node Map:

************** NUMA Node 0

No NUMA nodes.

Logical Processor to Cache Map:

**------------ Data Cache 0, Level 1, 48 KB, Assoc 12, LineSize 64

**------------ Instruction Cache 0, Level 1, 64 KB, Assoc 16, LineSize 64

**------------ Unified Cache 0, Level 2, 2 MB, Assoc 16, LineSize 64

************-- Unified Cache 1, Level 3, 12 MB, Assoc 12, LineSize 64

--*----------- Data Cache 1, Level 1, 32 KB, Assoc 8, LineSize 64

--*----------- Instruction Cache 1, Level 1, 64 KB, Assoc 8, LineSize 64

--****-------- Unified Cache 2, Level 2, 2 MB, Assoc 16, LineSize 64

---*---------- Data Cache 2, Level 1, 32 KB, Assoc 8, LineSize 64

---*---------- Instruction Cache 2, Level 1, 64 KB, Assoc 8, LineSize 64

----*--------- Data Cache 3, Level 1, 32 KB, Assoc 8, LineSize 64

----*--------- Instruction Cache 3, Level 1, 64 KB, Assoc 8, LineSize 64

-----*-------- Data Cache 4, Level 1, 32 KB, Assoc 8, LineSize 64

-----*-------- Instruction Cache 4, Level 1, 64 KB, Assoc 8, LineSize 64

------*------- Data Cache 5, Level 1, 32 KB, Assoc 8, LineSize 64

------*------- Instruction Cache 5, Level 1, 64 KB, Assoc 8, LineSize 64

------****---- Unified Cache 3, Level 2, 2 MB, Assoc 16, LineSize 64

-------*------ Data Cache 6, Level 1, 32 KB, Assoc 8, LineSize 64

-------*------ Instruction Cache 6, Level 1, 64 KB, Assoc 8, LineSize 64

--------*----- Data Cache 7, Level 1, 32 KB, Assoc 8, LineSize 64

--------*----- Instruction Cache 7, Level 1, 64 KB, Assoc 8, LineSize 64

---------*---- Data Cache 8, Level 1, 32 KB, Assoc 8, LineSize 64

---------*---- Instruction Cache 8, Level 1, 64 KB, Assoc 8, LineSize 64

----------**-- Data Cache 9, Level 1, 48 KB, Assoc 12, LineSize 64

----------**-- Instruction Cache 9, Level 1, 64 KB, Assoc 16, LineSize 64

----------**-- Unified Cache 4, Level 2, 2 MB, Assoc 16, LineSize 64

------------*- Data Cache 10, Level 1, 32 KB, Assoc 8, LineSize 64

------------*- Instruction Cache 10, Level 1, 64 KB, Assoc 8, LineSize 64

------------** Unified Cache 5, Level 2, 2 MB, Assoc 16, LineSize 64

-------------* Data Cache 11, Level 1, 32 KB, Assoc 8, LineSize 64

-------------* Instruction Cache 11, Level 1, 64 KB, Assoc 8, LineSize 64

Logical Processor to Group Map:

************** Group 0

Download Coreinfo(3 MB)Uruchom teraz z usługi Sysinternals Live.

Download Coreinfo(3 MB)Uruchom teraz z usługi Sysinternals Live.

Działa w:

- Klient: System Windows 11 lub nowszy.

- Serwer: System Windows Server 2016 lub nowszy.