Poznámka:

Přístup k této stránce vyžaduje autorizaci. Můžete se zkusit přihlásit nebo změnit adresáře.

Přístup k této stránce vyžaduje autorizaci. Můžete zkusit změnit adresáře.

Od Mark Russinovich

Publikováno: 16. prosince 2025

Coreinfo(3 MB)

Coreinfo(3 MB)

Úvod

Coreinfo je nástroj, který ukazuje mapování mezi logickými procesory a fyzickým procesorem, uzlem NUMA a soketem, na kterém se nacházejí, a také mezipamětí přiřazenými ke každému logickému procesoru. K načtení podrobných informací o topologii procesoru přímo z operačního systému používá rozhraní API systému Windows nízké úrovně (uživatelský režim a režim jádra). Verze příkazového řádku vypíše reprezentaci mapování na logický procesor, označenou hvězdičkou, například '*'. Uživatelské rozhraní poskytuje několik specializovaných zobrazení pro zkoumání různých aspektů topologie procesoru systému, včetně logických a fyzických jader, uzlů NUMA, soketů, hierarchií mezipaměti a metrik výkonu v reálném čase. Základní informace jsou užitečné pro získání přehledu o procesoru a topologii mezipaměti systému.

Instalace

Extrahujte archiv do adresáře a spusťte Coreinfo zadáním z daného adresáře Coreinfo / Coreinfo64 nebo Coreinfo64av závislosti na architektuře. Spusťte CoreInfoEx / CoreInfoEx64 / CoreInfoEx64a verzi uživatelského rozhraní.

Poznámka: Některé funkce můžou vyžadovat oprávnění správce k úplnému načtení informací.

Přehled uživatelského rozhraní

Uživatelské rozhraní Coreinfo se skládá z několika klíčových komponent:

Rozložení hlavního okna

- Horní panel: Zobrazí systémové informace, včetně názvu procesoru, architektury a počtu jader.

- Navigační podokno (vlevo): Poskytuje rychlý přístup k různým zobrazením.

- Oblast obsahu (Střed): Zobrazuje data a vizualizace vybraného zobrazení.

- Podokno podrobností (dole): Zobrazí podrobné informace, když jsou vybrána jádra nebo buňky.

- Nastavení: Možnosti vzhledu accessu a předvolby aplikace

Hlavní okno s úplným rozložením uživatelského rozhraní, tmavým režimem

Hlavní okno s úplným rozložením uživatelského rozhraní, tmavým režimem

Navigační zobrazení

Levé navigační podokno poskytuje přístup k šesti specializovaným zobrazením:

1. Základní zobrazení

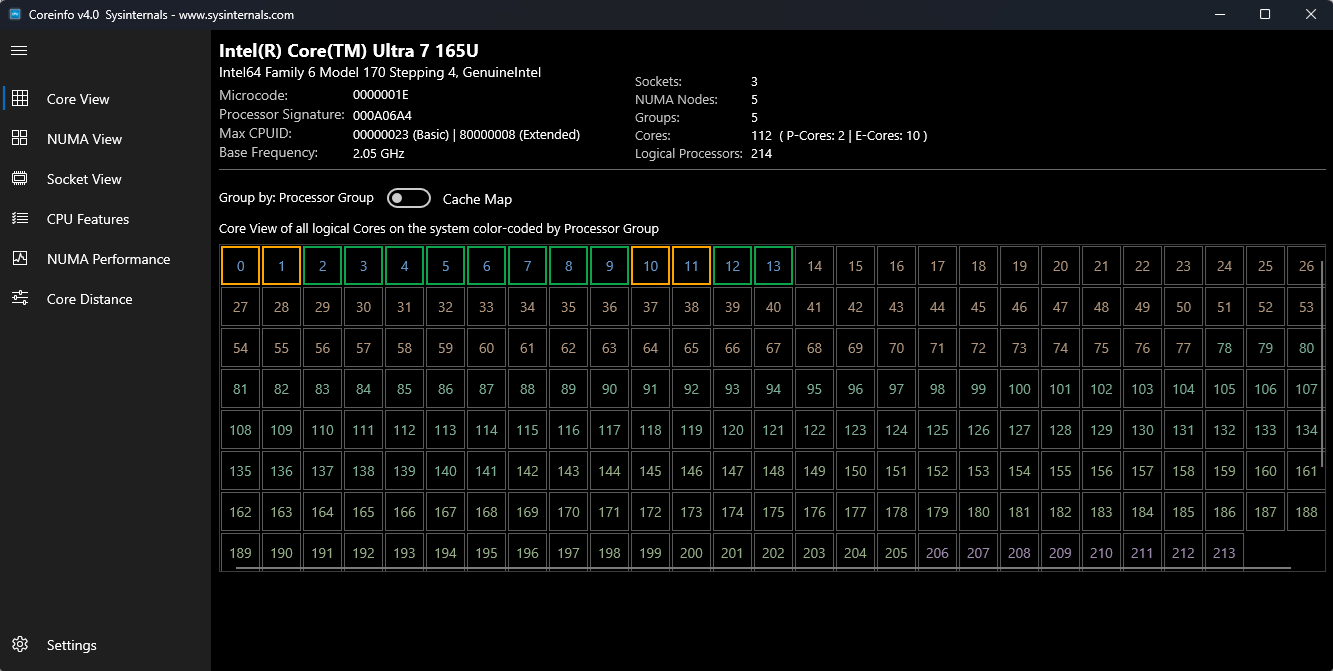

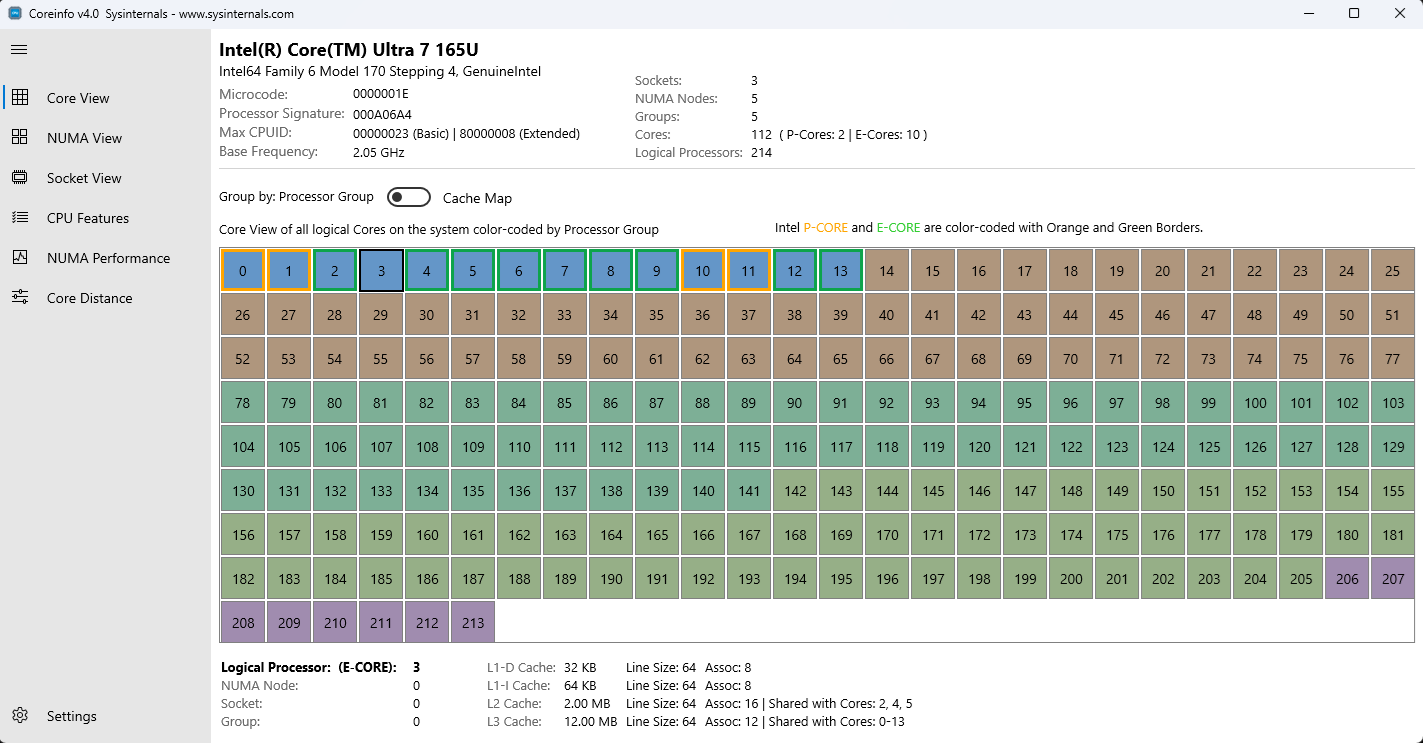

Základní zobrazení zobrazuje všechny logické procesory ve vašem systému v rozložení mřížky a zobrazuje vztah mezi logickými jádry a jejich fyzickými prostředky.

Rysy:

- Rozložení mřížky: Každá buňka představuje logický procesor.

-

Indikátory základního typu:

- Jádra P (jádra výkonu) – barevná zřetelně

- E-Cores (jádra efektivity) – barevné odlišně

- Standardní jádra – výchozí barvení

- Přepínač mapování mezipaměti: Přepínání mezi výchozím zobrazením a hierarchií mezipaměti

- Interaktivní výběr: Kliknutím na libovolné jádro zobrazíte podrobné informace v dolním podokně.

Zobrazené informace:

- Číslo logického procesoru

- Typ jádra (P-Core/E-Core, pokud je k dispozici)

- Přidružené úrovně mezipaměti (L1, L2, L3)

- Přiřazení uzlu NUMA

- Přiřazení soketů

- Přiřazení skupiny

Zobrazení jádra ukazující logické procesory v mřížkovém uspořádání

Zobrazení jádra ukazující logické procesory v mřížkovém uspořádání

Podokno s podrobnostmi (při výběru jádra):

- Maska a spřažení procesoru

- Hierarchie mezipaměti (mezipaměť dat, mezipaměť instrukcí, jednotná mezipaměť)

- Velikosti mezipaměti a asociativita

- Velikosti řádků mezipaměti

2. Zobrazení NUMA

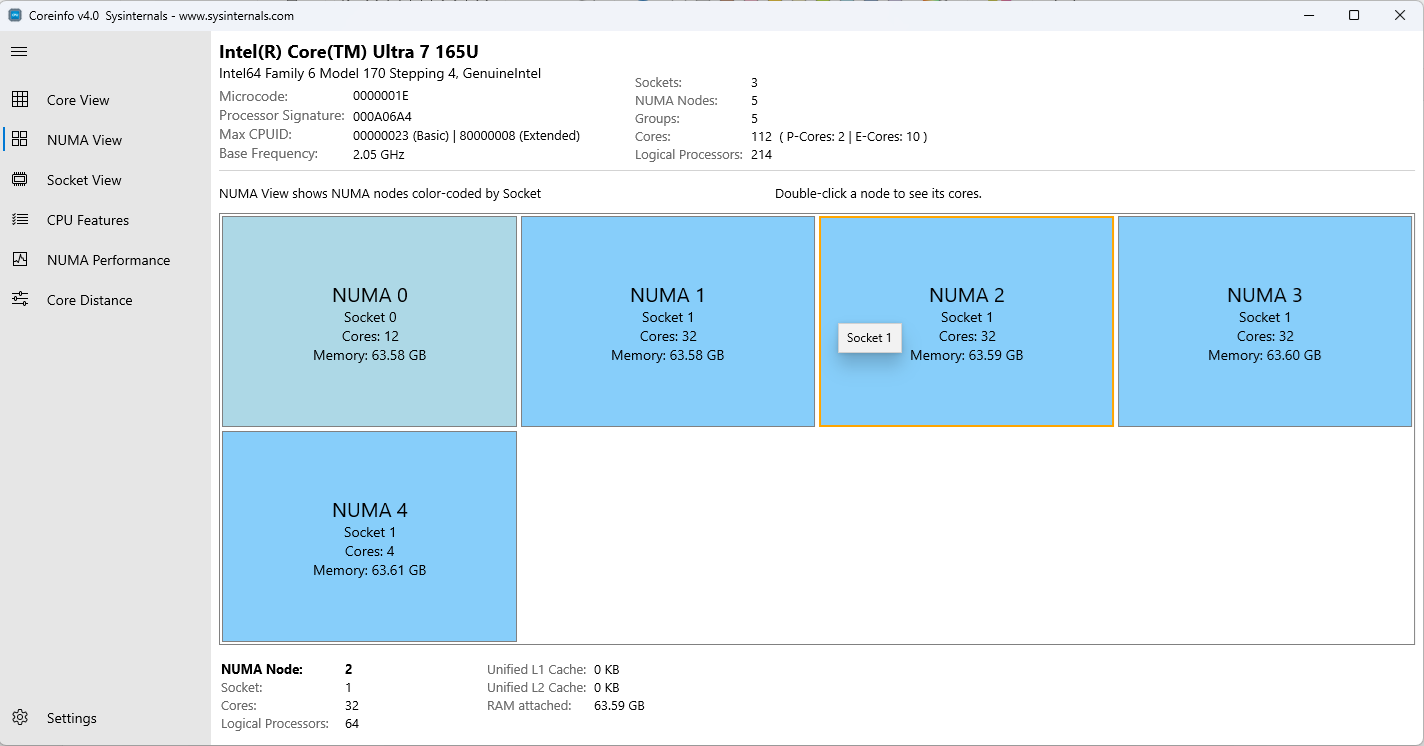

Zobrazení NUMA (Non-Uniform Memory Access) uspořádá jádra podle přiřazení uzlů NUMA, což usnadňuje pochopení umístění paměti a vzorů přístupu.

Rysy:

- Organizace založená na uzlech: Jádra seskupená podle NUMA uzlu

- Fyzická a logická jádra: Zobrazuje oba počty pro každý uzel.

- Informace o paměti: Zobrazí dostupnou paměť na uzel NUMA.

-

Interaktivní navigace:

- Jedním kliknutím na uzel NUMA zobrazíte podrobnosti v dolním podokně podrobností.

- Poklikáním na uzel NUMA přejděte do základního zobrazení zobrazující všechna jádra z vybraného uzlu NUMA.

- Hierarchické zobrazení: Zobrazuje vztah mezi uzly NUMA a jádry.

Zobrazené informace:

- Počet uzlů NUMA

- Počet jader na uzel NUMA (fyzický a logický)

- Kapacita paměti na uzel

- Základní distribuce mezi uzly

- Počet jader efektivnosti (pokud je k dispozici)

NUMA zobrazuje jádra organizovaná do uzlů NUMA

NUMA zobrazuje jádra organizovaná do uzlů NUMA

Případy použití:

- Optimalizace vzorů přístupu k paměti

- Principy výkonu aplikací podporujících technologii NUMA

- Plánování umístění vlákna nebo procesu pro zajištění optimálního výkonu

3. Zobrazení soketů

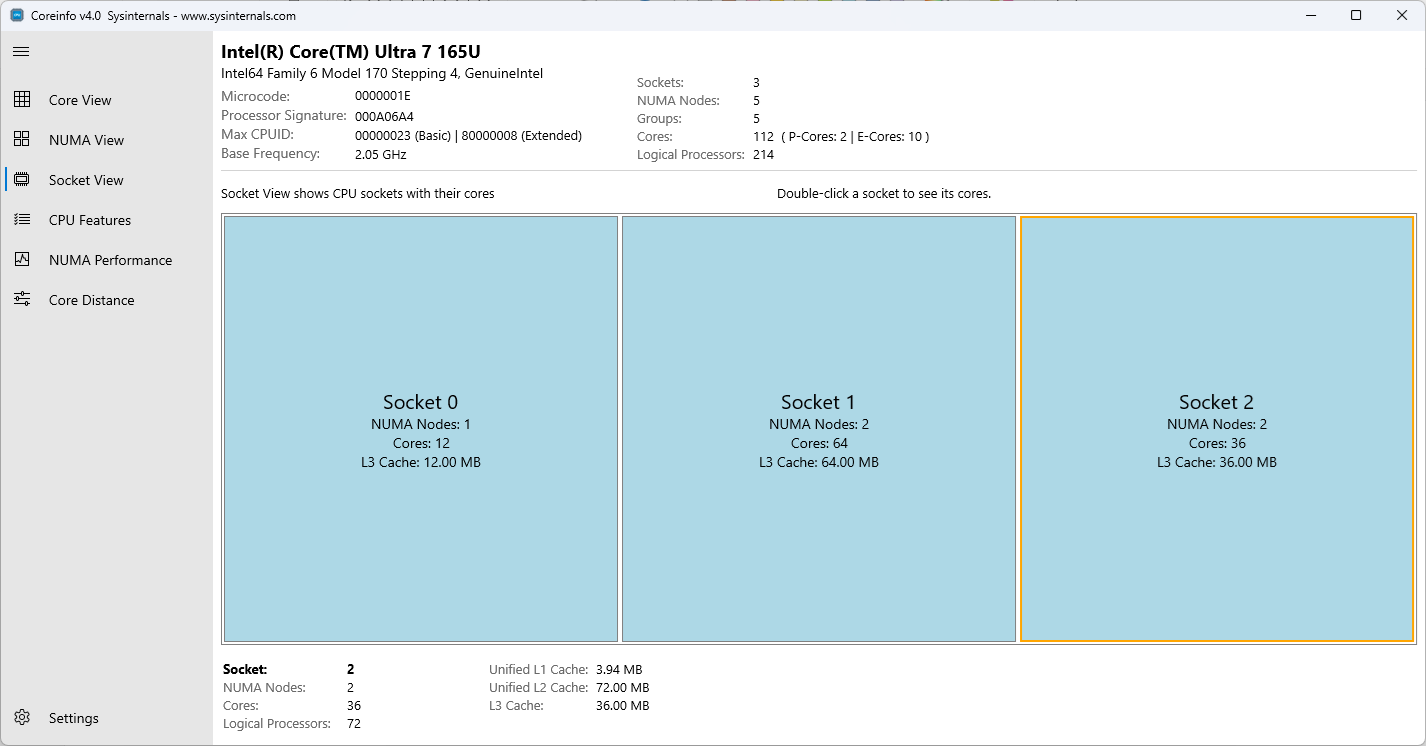

Zobrazení soketů zobrazuje jádra uspořádaná podle fyzického soketu procesoru, která jsou užitečná pro pochopení systémů s více sokety a distribuce prostředků na úrovni soketů.

Rysy:

- Seskupení na základě soketu: Jádra uspořádaná podle fyzického soketu

- Informace o soketu: Počet soketů a distribuce jader

-

Interaktivní navigace:

- Jedním kliknutím na soket zobrazíte jeho podrobnosti v dolním podokně podrobností.

- Poklikáním na soket přejdete do zobrazení jádra zobrazující všechna jádra z vybraného soketu.

- Sdílení mezipaměti: Vizualizace jader sdílejících mezipaměti na úrovni soketů

Zobrazené informace:

- Počet fyzických soketů

- Jádra na soket (fyzické a logické)

- Informace o mezipaměti na úrovni soketů

- Uzly NUMA na jeden soket

který zobrazuje jádra uspořádaná podle soketů procesoru

který zobrazuje jádra uspořádaná podle soketů procesoru

Případy použití:

- Analýza systému s více sokety

- Porozumění nákladům mezisoketové komunikace

- Plánování distribuce úloh na serverech s více sokety

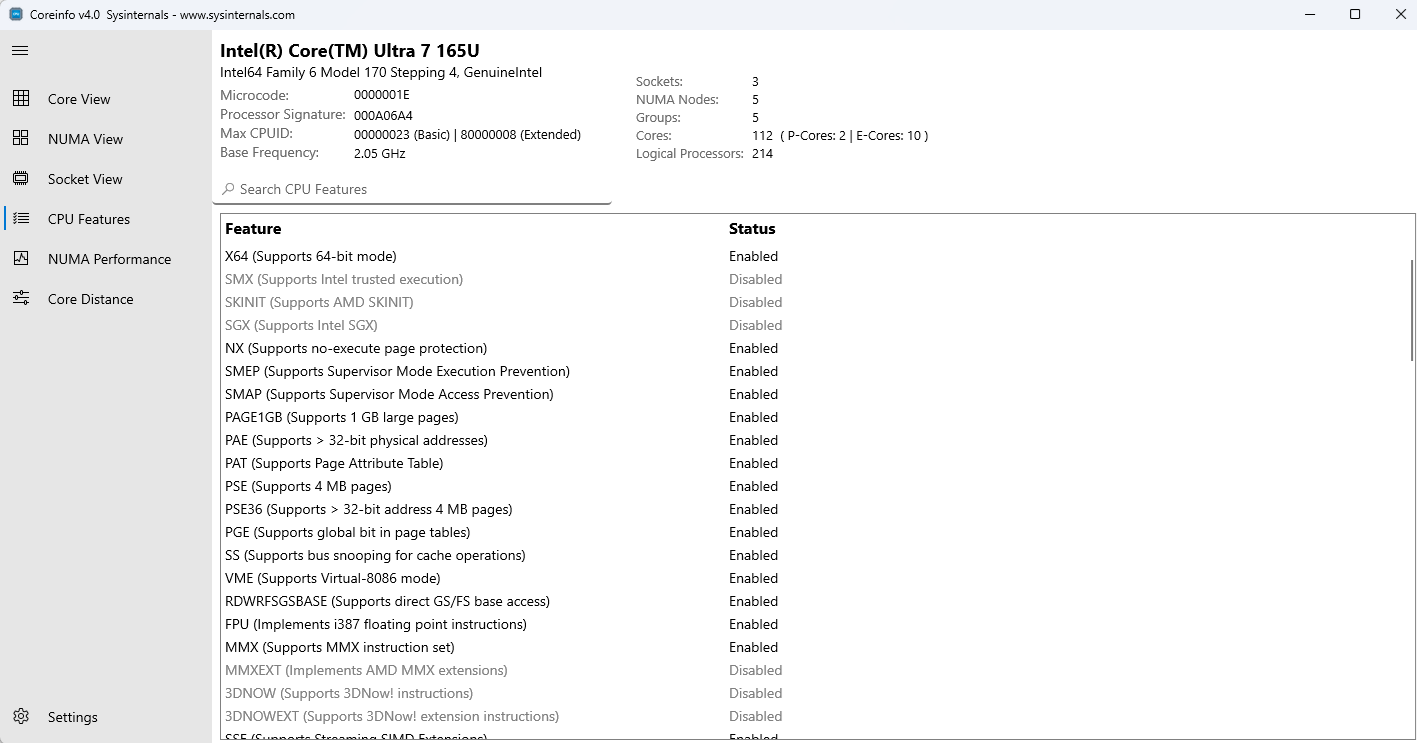

4. Zobrazení funkcí procesoru

Zobrazení funkcí procesoru zobrazuje úplný seznam funkcí procesoru, rozšíření sady instrukcí a hardwarových funkcí podporovaných vaším procesorem.

Rysy:

- Prohledávatelný seznam: Rychlé vyhledání konkrétních funkcí procesoru pomocí panelu hledání

-

Indikátory stavu: Jasné vizuální označení podporovaných/nepodporovaných funkcí pomocí barevného kódování

- Podporované funkce se zobrazují v normální barvě.

- Nepodporované nebo zakázané funkce jsou zobrazeny šedě

-

Kategorie funkcí:

- Virtualizace (VMX, SVM, HYPERVISOR)

- 64bitová podpora (EM64T, NX)

- Instrukční sady (SSE, AVX, AES atd.)

- Řízení spotřeby (EIST, ACPI, Thermal)

- Funkce zabezpečení (SMX, SKINIT)

- Funkce paměti (PAE, PAT, PSE)

- Funkce pro odstraňování chyb a monitorování

Zobrazené informace:

- Zkratka funkcí

- Stav funkce (podporované nebo nepodporováno)

- Úplný popis funkce (v podokně podrobností)

Zobrazení funkcí procesoru zobrazující seznam schopností procesoru

Zobrazení funkcí procesoru zobrazující seznam schopností procesoru

Poznámka: Některé virtualizační funkce (například VMX, SVM) se dají nesprávně hlásit jako nedostupné při spuštění s aktivním hypervisorem nebo při spuštění z virtuálního počítače. Coreinfo musí být provedeno v systému bez hypervisoru pro dosažení přesných výsledků.

Případy použití:

- Ověření dostupnosti sady instrukcí před nasazením aplikací

- Kontrola podpory virtualizace

- Principy generování a možností procesoru

- Ladění problémů s výkonem souvisejících s chybějícími funkcemi procesoru

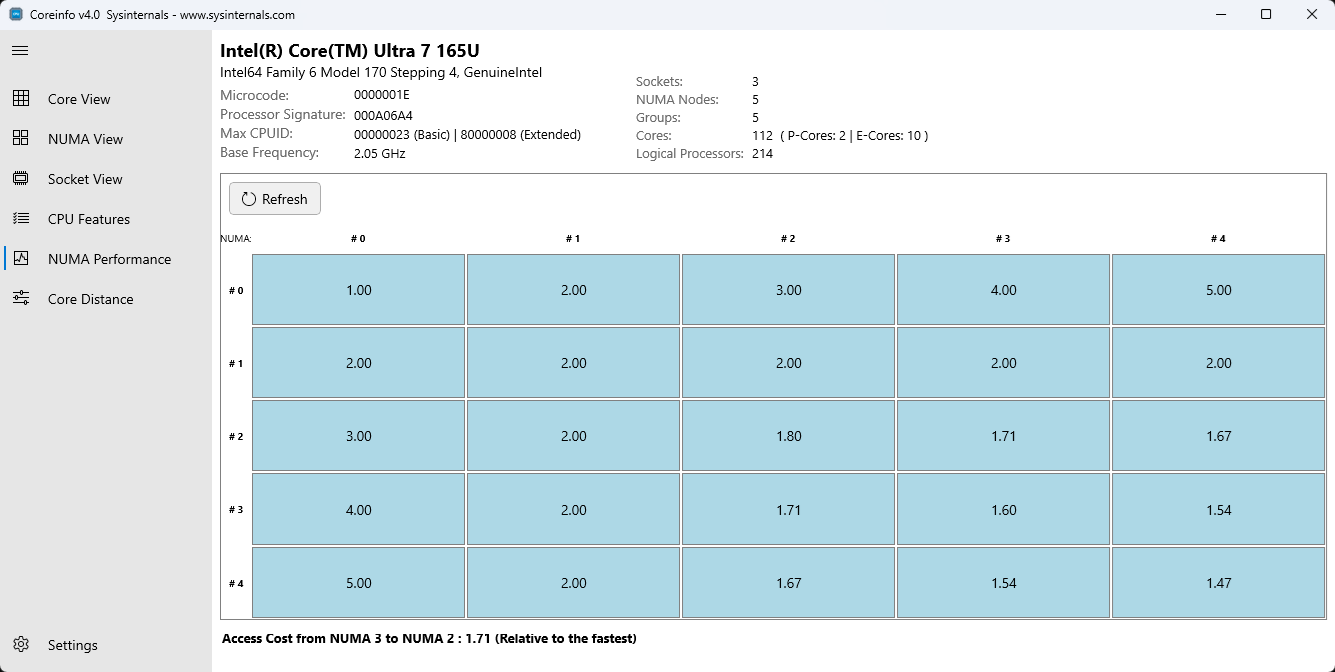

5. Zobrazení výkonu NUMA

Zobrazení výkonu NUMA poskytuje vizualizaci mřížky znázorňující náklady na přístup k paměti mezi uzly NUMA a pomáhá identifikovat kritické body výkonu v systémech NUMA.

Rysy:

- Vizualizace mřížky: Matice zobrazující náklady na relativní přístup k paměti mezi uzly NUMA

- Interaktivní matice: Když najedete myší na buňky, zobrazí se podrobné informace o výkonu.

- Real-Time aktualizace: Dynamické aktualizace dat o výkonu probíhají výběrem tlačítka Aktualizovat

- Zobrazení relativních nákladů: Zobrazuje relativní náklady na přístup k paměti z různých uzlů NUMA.

Zobrazené informace:

- Matice NxN, kde N = počet uzlů NUMA

- Náklady na přístup k paměti ze zdrojového uzlu NUMA (řádek) do cílového uzlu NUMA (sloupec)

- Číselné hodnoty zobrazující relativní náklady na výkon

- Diagonální buňky zobrazují přístup k místní paměti (obvykle s nejnižšími nároky na výpočetní zdroje)

NUMA Performance Grid zobrazující náklady na přístup k paměti

NUMA Performance Grid zobrazující náklady na přístup k paměti

Porozumění mřížce:

- Diagonální prvky: Představuje přístup k místní paměti (uzel přistupující k vlastní paměti) – obvykle nejnižší hodnoty

- Off-diagonální prvky: Představují vzdálený přístup k paměti s relativně vyššími náklady

- Symetrie: Matice nemusí být dokonale symetrická, protože náklady na přístup se mohou lišit podle směru.

Případy použití:

- Identifikace kritických bodů výkonu souvisejících s NUMA

- Optimalizace strategií přidělování paměti

- Plánování procesu nebo připnutí vláken pro systémy NUMA

- Vysvětlení sankcí přístupu k paměti mezi uzly

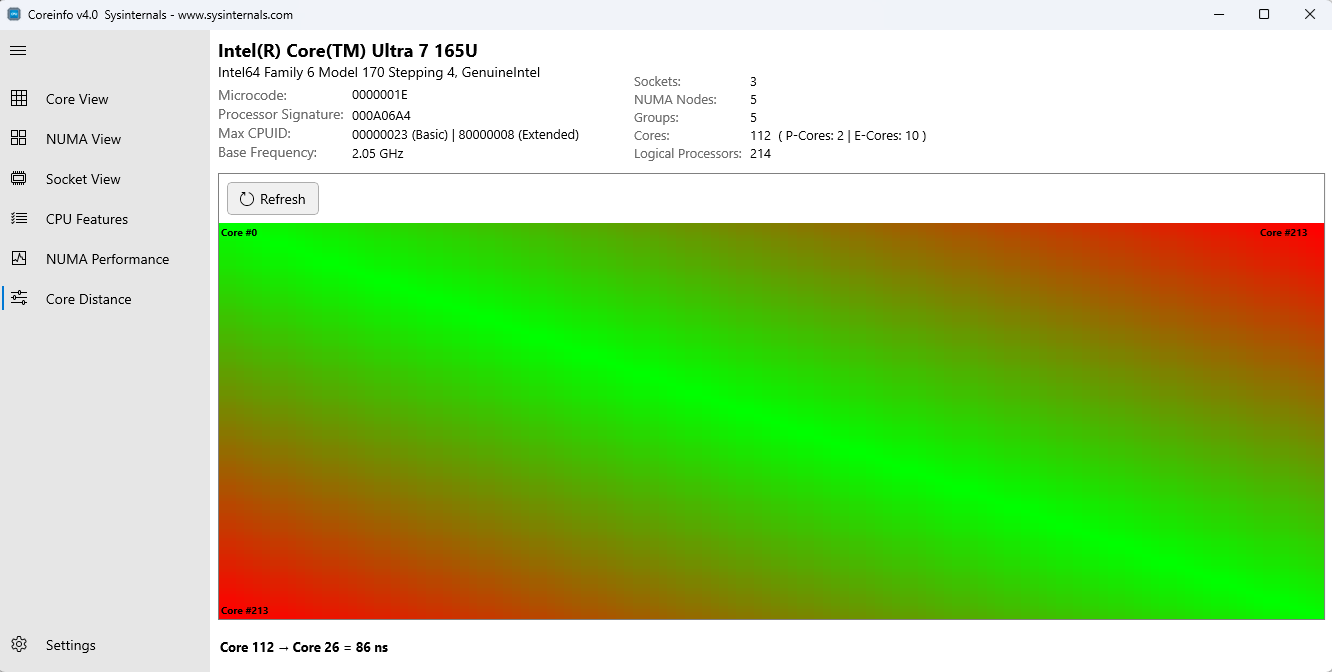

6. Základní zobrazení vzdálenosti

Zobrazení vzdálenosti mezi jádry zobrazuje podrobnou tepelnou mapu nákladů na komunikaci mezi jednotlivými jádry procesoru a poskytuje přehled o latenci při komunikaci mezi jádry a efektivitě komunikace.

Rysy:

-

Core-Level Heat Map: Barevně zakódovaná matice zobrazující relativní vzdálenosti mezi jádry

- Zelená/modrá = nízká latence (stejný základní cluster, sdílená mezipaměť)

- Žlutá/oranžová = střední latence (stejný soket, jiný cluster)

- Red = Vysoká latence (jiný soket nebo uzel NUMA)

- Interaktivní průzkum: Najetí myší na plátno mřížky pro zobrazení podrobných informací o vzdálenosti

- Podrobná analýza: Zobrazuje vztahy mezi jádry v nejpodrobnější úrovni.

- Dynamická aktualizace: Pomocí tlačítka Aktualizovat můžete dynamicky získat aktualizovaná data o vzdálenosti jádra.

Zobrazené informace:

- Matice NxN, kde N = počet logických procesorů

- Relativní vzdálenost/latence od zdrojového jádra (řádku) k cílovému jádru (sloupec)

- Barevné kódování pro rychlou vizuální identifikaci základních vztahů

- Podrobné metriky vzdálenosti v podokně podrobností

Tepelná mapa  ukazující náklady na komunikaci jádro-jádro

ukazující náklady na komunikaci jádro-jádro

Pochopení mapy vzdálenosti:

- Diagonální prvky: Vždy nula (jádro k sobě)

- Nízká vzdálenost (zelená):: Jádra sdílejí mezipaměť L2 nebo L3

- Střední vzdálenost (žlutá):: Jádra na stejném soketu, ale v různých doménách mezipaměti

- Vysoká vzdálenost (červená): Jádra na různých soketech nebo uzlech NUMA

Případy použití:

- Optimalizace afinity vláken

- Principy domén souběžnosti mezipaměti

- Identifikace optimálních párů jader pro komunikaci vláken

- Analýza výkonu vícevláknových aplikací

- Plánování strategií připnutí CPU pro aplikace s nízkou latencí

Interaktivní funkce

Základní výběr a podrobnosti

Kliknutím na procesorové jádro v libovolném zobrazení (Jádro, NUMA nebo socket) se zobrazí podrobné informace v dolním panelu.

- Informace o procesoru: Logické číslo procesoru, maska a spřažení

-

Hierarchie mezipaměti:

- Mezipaměť dat L1 (velikost, asociativita, velikost čáry)

- Mezipaměť instrukcí L1 (velikost, asociativita, velikost řádku)

- Mezipaměť L2 (velikost, asociativita, velikost čáry)

- Mezipaměť L3 (velikost, asociativita, velikost čáry)

- Informace o topologii: Přiřazení uzlů NUMA, soketů a skupin

- Typ jádra: P-Core, E-Core nebo standardní označení jádra

Funkce vyhledávání

Zobrazení Funkce procesoru obsahuje panel hledání, který umožňuje rychle vyhledat konkrétní funkce procesoru:

- Klikněte na ikonu hledání.

- Zadejte název nebo zkratku funkce.

- Seznam automaticky filtruje, aby zobrazoval odpovídající funkce.

- Vymazáním hledání obnovíte úplný seznam.

Přepnout cache mapu

V základním zobrazení přepněte mezi dvěma režimy vizualizace:

- Výchozí režim: Zobrazuje jádra v logickém uspořádání.

- Režim mapování mezipaměti: Reorganizuje jádra pro vizualizaci vztahů sdílení mezipaměti.

Navigace mezi zobrazeními

- Přepínání mezi zobrazeními pomocí levého navigačního podokna

- Při zobrazení určitého uzlu nebo soketu NUMA se kliknutím na stejné zobrazení znovu vrátíte do celkového zobrazení.

- Aktuální zobrazení je zvýrazněné v navigačním podokně.

Nastavení a přizpůsobení

Otevřete nastavení prostřednictvím možnosti Nastavení v navigační nabídce.

Nastavení vzhledu

Možnosti motivu:

- Světlo: Barevné schéma světla optimalizované pro jasná prostředí

- Tmavá: Tmavé barevné schéma pro snížení přetížení očí

- Výchozí nastavení systému: Automaticky odpovídá předvolbě motivu Windows.

Uložit do souboru

Export dat základní topologie:

- Použijte možnost Uložit do k exportu základních topologických dat do souboru.

- Výstupní formát je shodný s výstupem nástroje příkazového řádku.

Principy topologie systému

Základní typy (hybridní architektura)

Moderní procesory můžou používat hybridní architektury s různými typy jader:

- P-Cores (Výkon):: Vysoce výkonná jádra optimalizovaná pro jednovláknová a náročná zatížení

- E-Cores (Efficiency): Energeticky efektivní jádra optimalizovaná pro úlohy na pozadí a úlohy s více vlákny

Uživatelské rozhraní Coreinfo jasně identifikuje a rozlišuje tyto základní typy ve všech příslušných zobrazeních.

Architektura NUMA

Co je NUMA? NUMA (Non-Uniform Memory Access) je návrh paměti, kde každý procesor má místní paměť, ke které má rychlý přístup, a vzdálená paměť, která vyžaduje komunikaci mezi procesory.

Proč je to důležité:

- Přístup k místní paměti je výrazně rychlejší než vzdálený přístup

- Výkon aplikace může být výrazně ovlivněn umístěním NUMA.

- Pochopení topologie NUMA je zásadní pro vysokovýkonné výpočetní prostředí

Použití uživatelského rozhraní Coreinfo pro optimalizaci NUMA:

- Pochopení topologie NUMA systému pomocí zobrazení NUMA

- Zkontrolujte zobrazení výkonu NUMA a podívejte se na náklady na přístup k paměti.

- Optimalizace umístění vlákna nebo procesu na základě přiřazení uzlů NUMA

- Použití zobrazení základní vzdálenosti k pochopení komunikace mezi jádry v uzlech NUMA a mezi uzly NUMA

Hierarchie mezipaměti

Úrovně mezipaměti:

- L1 Cache: Nejmenší a nejrychlejší, rozdělené na data a instrukční mezipaměti

- Mezipaměť L2: Větší jednotná mezipaměť, obvykle soukromá pro každé jádro

- Mezipaměť L3: Největší jednotná mezipaměť, často sdílená mezi více jádry

Použití informací o mezipaměti:

- Pochopit, která jádra sdílejí prostředky mezipaměti

- Optimalizovat umístění dat pro jádra sdílející mezipaměť

- Použití režimu mapy mezipaměti v zobrazení Core View k vizualizaci domén mezipaměti

Použití Coreinfo z příkazového řádku

Pro každý prostředek, který zobrazuje mapu procesorů viditelných operačním systémem, které odpovídají zadaným prostředkům, se znakem *, který představuje příslušné procesory. Například ve 4jádrovým systému je řádek ve výstupu mezipaměti s mapou sdílenou jádry 3 a 4.

Zvyk:

coreinfo [-c][-f][-g][-l][-n][-s][-m][-v]

| Parametr | Popis |

|---|---|

| -c | Výpis informací o jádrech |

| -f | Výpis základních informací o funkcích |

| -g | Výpis informací o skupinách |

| -l | Výpis informací o mezipamětí |

| -n | Výpis informací o uzlech NUMA |

| -s | Výpis informací o soketech |

| -m | Výpis nákladů na přístup NUMA |

| -v | Výpis pouze funkcí souvisejících s virtualizací, včetně podpory překladu adres druhé úrovně. (vyžaduje práva správce v systémech Intel). |

Ve výchozím nastavení jsou vybrané všechny možnosti s výjimkou -v .

Výstup coreinfo:

Coreinfo v4.0 - Dump information on system CPU and memory topology

Copyright © 2008-2025 Mark Russinovich

Sysinternals - www.sysinternals.com

Intel(R) Core(TM) Ultra 7 165U

Intel64 Family 6 Model 170 Stepping 4, GenuineIntel

Microcode signature: 0000001E

Processor signature: 000A06A4

Maximum implemented CPUID leaves: 00000023 (Basic), 80000008 (Extended).

Maximum implemented address width: 48 bits (virtual), 46 bits (physical).

HTT * Hyperthreading enabled

CET * Supports Control Flow Enforcement Technology

Kernel CET - Kernel-mode CET Enabled

User CET * User-mode CET Allowed

X64 * Supports 64-bit mode

SMX - Supports Intel trusted execution

SKINIT - Supports AMD SKINIT

SGX - Supports Intel SGX

NX * Supports no-execute page protection

SMEP * Supports Supervisor Mode Execution Prevention

SMAP * Supports Supervisor Mode Access Prevention

PAGE1GB * Supports 1 GB large pages

PAE * Supports > 32-bit physical addresses

PAT * Supports Page Attribute Table

PSE * Supports 4 MB pages

PSE36 * Supports > 32-bit address 4 MB pages

PGE * Supports global bit in page tables

SS * Supports bus snooping for cache operations

VME * Supports Virtual-8086 mode

RDWRFSGSBASE * Supports direct GS/FS base access

FPU * Implements i387 floating point instructions

MMX * Supports MMX instruction set

MMXEXT - Implements AMD MMX extensions

3DNOW - Supports 3DNow! instructions

3DNOWEXT - Supports 3DNow! extension instructions

SSE * Supports Streaming SIMD Extensions

SSE2 * Supports Streaming SIMD Extensions 2

SSE3 * Supports Streaming SIMD Extensions 3

SSSE3 * Supports Supplemental SIMD Extensions 3

SSE4a - Supports Streaming SIMDR Extensions 4a

SSE4.1 * Supports Streaming SIMD Extensions 4.1

SSE4.2 * Supports Streaming SIMD Extensions 4.2

AES * Supports AES extensions

AVX * Supports AVX instruction extensions

AVX2 * Supports AVX2 instruction extensions

AVX-512-F - Supports AVX-512 Foundation instructions

AVX-512-DQ - Supports AVX-512 double and quadword instructions

AVX-512-IFAMA - Supports AVX-512 integer Fused multiply-add instructions

AVX-512-PF - Supports AVX-512 prefetch instructions

AVX-512-ER - Supports AVX-512 exponential and reciprocal instructions

AVX-512-CD - Supports AVX-512 conflict detection instructions

AVX-512-BW - Supports AVX-512 byte and word instructions

AVX-512-VL - Supports AVX-512 vector length instructions

FMA * Supports FMA extensions using YMM state

MSR * Implements RDMSR/WRMSR instructions

MTRR * Supports Memory Type Range Registers

XSAVE * Supports XSAVE/XRSTOR instructions

OSXSAVE * Supports XSETBV/XGETBV instructions

RDRAND * Supports RDRAND instruction

RDSEED * Supports RDSEED instruction

CMOV * Supports CMOVcc instruction

CLFSH * Supports CLFLUSH instruction

CX8 * Supports compare and exchange 8-byte instructions

CX16 * Supports CMPXCHG16B instruction

BMI1 * Supports bit manipulation extensions 1

BMI2 * Supports bit manipulation extensions 2

ADX * Supports ADCX/ADOX instructions

DCA - Supports prefetch from memory-mapped device

F16C * Supports half-precision instruction

FXSR * Supports FXSAVE/FXSTOR instructions

FFXSR - Supports optimized FXSAVE/FSRSTOR instruction

MONITOR * Supports MONITOR and MWAIT instructions

MOVBE * Supports MOVBE instruction

ERMSB * Supports Enhanced REP MOVSB/STOSB

PCLMULDQ * Supports PCLMULDQ instruction

POPCNT * Supports POPCNT instruction

LZCNT * Supports LZCNT instruction

SEP * Supports fast system call instructions

LAHF-SAHF * Supports LAHF/SAHF instructions in 64-bit mode

HLE - Supports Hardware Lock Elision instructions

RTM - Supports Restricted Transactional Memory instructions

DE * Supports I/O breakpoints including CR4.DE

DTES64 - Can write history of 64-bit branch addresses

DS - Implements memory-resident debug buffer

DS-CPL - Supports Debug Store feature with CPL

PCID * Supports PCIDs and settable CR4.PCIDE

INVPCID * Supports INVPCID instruction

PDCM * Supports Performance Capabilities MSR

RDTSCP * Supports RDTSCP instruction

TSC * Supports RDTSC instruction

TSC-DEADLINE * Local APIC supports one-shot deadline timer

TSC-INVARIANT * TSC runs at constant rate

xTPR * Supports disabling task priority messages

EIST * Supports Enhanced Intel Speedstep

ACPI * Implements MSR for power management

TM * Implements thermal monitor circuitry

TM2 * Implements Thermal Monitor 2 control

APIC * Implements software-accessible local APIC

x2APIC * Supports x2APIC

CNXT-ID - L1 data cache mode adaptive or BIOS

MCE * Supports Machine Check, INT18 and CR4.MCE

MCA * Implements Machine Check Architecture

PBE * Supports use of FERR#/PBE# pin

PSN - Implements 96-bit processor serial number

HTT * Hyperthreading

PREFETCHW * PrefetchW instruction support

HYPERVISOR * Hypervisor is present

VMX - Supports Intel hardware-assisted virtualization

EPT - Supports Intel extended page tables (SLAT)

URG - Supports Intel unrestricted guest

Logical to Physical Processor Map:

**------------ Physical Processor 0 (Hyperthreaded)

--*----------- Physical Processor 1

---*---------- Physical Processor 2

----*--------- Physical Processor 3

-----*-------- Physical Processor 4

------*------- Physical Processor 5

-------*------ Physical Processor 6

--------*----- Physical Processor 7

---------*---- Physical Processor 8

----------**-- Physical Processor 9 (Hyperthreaded)

------------*- Physical Processor 10

-------------* Physical Processor 11

Logical Processor to Socket Map:

************** Socket 0

Logical Processor to NUMA Node Map:

************** NUMA Node 0

No NUMA nodes.

Logical Processor to Cache Map:

**------------ Data Cache 0, Level 1, 48 KB, Assoc 12, LineSize 64

**------------ Instruction Cache 0, Level 1, 64 KB, Assoc 16, LineSize 64

**------------ Unified Cache 0, Level 2, 2 MB, Assoc 16, LineSize 64

************-- Unified Cache 1, Level 3, 12 MB, Assoc 12, LineSize 64

--*----------- Data Cache 1, Level 1, 32 KB, Assoc 8, LineSize 64

--*----------- Instruction Cache 1, Level 1, 64 KB, Assoc 8, LineSize 64

--****-------- Unified Cache 2, Level 2, 2 MB, Assoc 16, LineSize 64

---*---------- Data Cache 2, Level 1, 32 KB, Assoc 8, LineSize 64

---*---------- Instruction Cache 2, Level 1, 64 KB, Assoc 8, LineSize 64

----*--------- Data Cache 3, Level 1, 32 KB, Assoc 8, LineSize 64

----*--------- Instruction Cache 3, Level 1, 64 KB, Assoc 8, LineSize 64

-----*-------- Data Cache 4, Level 1, 32 KB, Assoc 8, LineSize 64

-----*-------- Instruction Cache 4, Level 1, 64 KB, Assoc 8, LineSize 64

------*------- Data Cache 5, Level 1, 32 KB, Assoc 8, LineSize 64

------*------- Instruction Cache 5, Level 1, 64 KB, Assoc 8, LineSize 64

------****---- Unified Cache 3, Level 2, 2 MB, Assoc 16, LineSize 64

-------*------ Data Cache 6, Level 1, 32 KB, Assoc 8, LineSize 64

-------*------ Instruction Cache 6, Level 1, 64 KB, Assoc 8, LineSize 64

--------*----- Data Cache 7, Level 1, 32 KB, Assoc 8, LineSize 64

--------*----- Instruction Cache 7, Level 1, 64 KB, Assoc 8, LineSize 64

---------*---- Data Cache 8, Level 1, 32 KB, Assoc 8, LineSize 64

---------*---- Instruction Cache 8, Level 1, 64 KB, Assoc 8, LineSize 64

----------**-- Data Cache 9, Level 1, 48 KB, Assoc 12, LineSize 64

----------**-- Instruction Cache 9, Level 1, 64 KB, Assoc 16, LineSize 64

----------**-- Unified Cache 4, Level 2, 2 MB, Assoc 16, LineSize 64

------------*- Data Cache 10, Level 1, 32 KB, Assoc 8, LineSize 64

------------*- Instruction Cache 10, Level 1, 64 KB, Assoc 8, LineSize 64

------------** Unified Cache 5, Level 2, 2 MB, Assoc 16, LineSize 64

-------------* Data Cache 11, Level 1, 32 KB, Assoc 8, LineSize 64

-------------* Instruction Cache 11, Level 1, 64 KB, Assoc 8, LineSize 64

Logical Processor to Group Map:

************** Group 0

Coreinfo(3 MB)Spustit nyní z Sysinternals Live.

Coreinfo(3 MB)Spustit nyní z Sysinternals Live.

Běží na:

- Klient: Windows 11 a vyšší.

- Server: Windows Server 2016 a novější.